Fターム[4M104FF32]の内容

Fターム[4M104FF32]に分類される特許

101 - 120 / 230

半導体装置

ここに記載されているのは、組み込まれたPNダイオードを挟み込み素子として有するTJBS(Trench-Junction-Barrier-Schottky-Diode)を備えた半導体装置であり、この半導体装置は、殊に自動車のジェネレータシステムに使用される約20Vの降伏電圧を有するツェナーダイオードに適している。このTJBSは、ショットキーダイオードおよびPNダイオードの組み合わせから構成されている。降伏電圧に対して当てはまるのは、PNダイオードの降伏電圧BV_pnが、ショットキーダイオードの降伏電圧BV_schottkyよりも低いことである。したがってこの半導体装置は、降伏時に大きな電流で動作させることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】オン電圧を低減した半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、前記第1の半導体層の上に設けられた第2導電型の第2の半導体層と、前記第1の半導体層の上に前記第2の半導体層と接して設けられた前記第1の半導体層よりも不純物濃度の高い第1導電型の第3の半導体層と、前記第2の半導体層に接続された第1の金属層と、前記第3の半導体層に接続され前記第1の金属層とは異なる金属からなる第2の金属層と、を有する第1の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

ダイオード

【課題】 n型半導体領域の表面の一部にp型半導体領域が設けられたダイオードにおいて、内在するpn接合ダイオードを活用して順方向抵抗を低減化する技術を提供する。

【解決手段】 n型半導体領域22と、n型半導体領域22の表面の一部に設けられているp型半導体領域14と、n型半導体領域22の表面とp型半導体領域14の表面に接しており、少なくともn型半導体領域22の表面にショットキー接合Jbしているアノード電極2(表面電極)と、n型半導体領域22に接する右側面30b(第1側面)及び左側面30a(第2側面)を有する絶縁領域30を備えている。右側面30bは、ショットキー接合Jbの下方に位置する第2n型半導体領域22bに対向しており、左側面30aは、n型半導体領域22とp型半導体領域14とのpn接合13の下方に位置する第1n型半導体領域22aに対向している。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのSBD10は、半導体からなる基板11と、基板11上に形成されたn型層12と、n型層12上に配置されたアノード電極14と、アノード電極14に接続され、n型層12に突出するp型領域13とを備えている。p型領域13は、n型層12との境界領域において、境界領域に隣接するp型領域13内の領域である高不純物領域13Bよりも導電型がp型であるp型不純物の濃度の低い低不純物領域13Aを含んでいる。

(もっと読む)

傾斜ドープ領域を有する縦型接合電界効果トランジスターおよびダイオードならびに製造方法

半導体装置および装置を製造する方法が記載される。前記装置は、接合障壁ショットキー(JBS)ダイオードまたはPiNダイオードなどの、接合電界効果トランジスター(JFET)またはダイオードであり得る。前記装置は、エピタキシャル成長によって形成された、傾斜したp型半導体層及び/又はp型半導体領域を有する。前記方法は、イオン注入を必要としない。前記装置は、炭化ケイ素(SiC)などの広バンドギャップの半導体材料から製造され得、高温度および高電力の用途で使用され得る。 (もっと読む)

ショットキーバリアダイオードを備えた炭化珪素半導体装置およびその製造方法

【課題】バリアハイトを制御し、逆方向リーク電流値が高くなることを抑制できるショットキーダイオードを備えたSiC半導体装置およびその製造方法を提供する。

【解決手段】ショットキー電極4のうちSiCと直接接触する部分を酸化物層4aにて構成する。これにより、SiCとバリアハイトを高くすることが可能となり、逆方向リーク電流値を低減することができる。さらに、このような酸化物層4aの平均酸素濃度(重量%)を変化させることにより、バリアハイトの値を制御することができる。したがって、バリアハイトを制御し、逆方向リーク電流値が高くなることを抑制できる。

(もっと読む)

ショットキーバリアダイオードを備えた半導体装置およびその製造方法

【課題】サージ耐量の向上が図れ、かつ、順方向における抵抗値の低減も図ることが可能な構造のSBDを備えた半導体装置を提供する。

【解決手段】p+型不純物層3の側面部に沿ってn型不純物層6を形成することで、p+型不純物層3の側面部からn-型ドリフト層2に伸びる空乏層の広がりを小さくする。これにより、PN接合で形成される空乏層幅を狭めることができ、順方向における抵抗値を低減させることが可能となる。そして、順方向における抵抗値の低減が図れることで、SiC半導体装置の単位面積当りのp+型不純物層3の面積を大きく取ることができ、サージ耐量の向上と順方向における抵抗値の低減の両立を図ることが可能となる。

(もっと読む)

半導体装置

【課題】強度を保持しつつ、導通時の抵抗を低減可能な電力用の半導体装置を提供する。

【解決手段】半導体装置10は、基板領域1と、基板領域1上に設けられ、炭化珪素を含む半導体材料からなり、複数の凹部が形成されたドリフト領域2と、側壁に配設されたアノード電極3と、凹部の側壁を挟んでアノード電極3と互いに対面するように側壁に配設され、かつ、アノード電極3と絶縁されたカソード電極4とを有する。

(もっと読む)

超接合ショットキーダイオード

【課題】高速スイッチング特性と低オン抵抗特性とを有し、オン抵抗−リーク電流間のトレードオフ関係を改善する超接合ショットキーダイオードを提供すること。

【解決手段】n型半導体層3の一方の主面上に垂直に形成される層状またはコラム状のn型ドリフト領域1aとp型仕切り領域1bとを、前記主面に平行方向に交互に配置した並列pn層1を備え、前記n型ドリフト領域1aの主面に接し、該n型ドリフト領域1aの比抵抗より高比抵抗のn型第一表面領域2aと、前記p型仕切り領域1bの主面と前記n型第一表面領域1aの側面とに接し、前記n型第一表面領域1aより高比抵抗のn型第二表面領域2bとを備え、前記n型の第一表面領域2aと第二表面領域2bとの主面にショットキー接触するアノード電極4と前記n型半導体層の他方の主面にオーミック接触するカソード電極5を有する超接合ショットキーダイオード10とする。

(もっと読む)

半導体装置とその製造方法

【課題】スイッチング速度の高速化と順方向電圧の低減を進展させることができる半導体装置を提供する。

【解決手段】本発明にかかる半導体装置は、第1の層(n+型のシリコン基板1)と、前記第1の層の一方の面上に形成された前記第1の層と同じ導電型で前記第1の層よりも不純物濃度が低くかつ格子定数が異なる複数の主成分からなる第2の層(n−型のSiGe層2)と、前記第2の層の表面から深さ方向へ延在する前記第2の層とは異なる導電型で前記第2の層よりも不純物濃度が高くかつ前記第2の層とは異なる格子定数を有する埋込層(p型のシリコン層3)を備える。

(もっと読む)

炭化珪素半導体装置及び炭化珪素半導体装置の製造方法

【課題】低い接触抵抗と良好な表面状態とを併せ持つオーミック性電極を備えた炭化珪素半導体装置を提供する。

【解決手段】SiC単結晶基板1上のN型エピタキシャル層2に対するショットキー金属部8と、N型エピタキシャル層に設けられたp型炭化珪素単結晶4に対するオーミック性電極5とを備える。オーミック性電極は、少なくともチタンとアルミニウムと珪素とを含む合金層を有する。合金層のチタンとアルミニウムと珪素との割合が、Al:40〜70質量%、Ti:20〜50質量%、Si:1〜15質量%である。

(もっと読む)

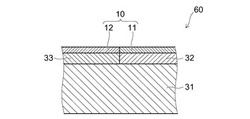

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

トレンチショットキバリアダイオード

【課題】製造ばらつきに起因してキャリアバンスがn過多となった場合でも、逆方向リーク電流IRと順方向降下電圧VFとの間にあるトレードオフの関係を改善することが可能なトレンチショットキバリアダイオードを提供する。

【解決手段】n+型のカソード領域112及びn−型のドリフト領域114を有する半導体基板110と、絶縁層124を介して導電性材料126が埋め込まれた構造を有する複数の第2主面側トレンチ領域122及び複数のp型の第1主面側トレンチ領域120を有するトレンチ領域116と、ドリフト領域114において隣接するトレンチ領域116間に挟まれた部分に位置するメサ領域118と、半導体基板110の第2主面上に形成され、メサ領域118との間でショットキ接合を形成するバリア金属層128とを備えるトレンチショットキバリアダイオード100。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体デバイス及び半導体デバイスの製造方法

【課題】基板が薄型化されるとともに、微細パターンからなる半導体領域が形成された半導体デバイスの製造方法を提供することを目的とする。

【解決手段】SiC単結晶基板1にN型エピタキシャル層2を形成した後、ステッパーによるフォトリソグラフィー法を用いて微細パターンからなるP型不純物領域3、4及び表面オーミックコンタクト電極5を形成する工程と、表面オーミックコンタクト電極5を覆うように保護膜を形成し、前記保護膜の平坦化を行う工程と、SiC単結晶基板1を薄くする基板薄型化工程と、SiC単結晶基板1に裏面オーミックコンタクト電極7を形成する工程と、P型不純物領域3、4及び表面オーミックコンタクト電極5と接続されたショットキー金属部8を形成し、ショットキー金属部8を覆う表面パッド電極9を形成する工程と、を具備する半導体デバイス101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

太陽電池セルおよびその製造方法

【課題】極の位置合わせが容易な太陽電池セルおよびその製造方法を提供する。

【解決手段】p型の半導体基板1と、半導体基板1の受光面側に形成されたn型の拡散層と、n型の拡散層に部分的に形成される1または複数の受光面グリッド電極7とから構成される太陽電池セルであって、n型の拡散層には、複数の高濃度拡散領域5と、それら高濃度拡散領域5間に位置する低濃度拡散領域6が形成され、受光面グリッド電極7は、高濃度拡散領域5に形成され、隣接する高濃度拡散領域5の中心間距離Lが1.5〜3.0mmであり、高濃度拡散領域5の幅Mが、中心間距離Lの20〜60%である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置

【課題】ショットキー接合面積を維持しつつ、設定耐圧値に相応する逆方向バイアスの印加時に、メサ部よりも先に活性領域でブレークダウンを発生させることで、ESD耐量を向上して安定した特性と高信頼性を実現できる半導体装置を提供する。

【解決手段】半導体基板101の外周縁部に斜面をなすメサ部107を形成したものであって、第2の半導体領域106は、第1の電極102と接触して半導体基板101の一方の主面側の活性領域に配置する主領域部106aを有し、主領域部106aが外縁の環状部106cと環状部106cに囲まれた内側域に分散配置する分散部106dとからなり、分散部106dの相互間および分散部106dと環状部106cとの間に第1の半導体領域105の一部が介在するものにおいて、分散部を小ピッチ領域と大ピッチ領域とで構成し、順方向電圧を所望の値に維持しつつ、所望の耐圧を達成する。

(もっと読む)

半導体装置

【課題】広い電流密度範囲で、動作電圧の小さい半導体装置を得ることを目的とする。

【解決手段】本発明における半導体装置10は、第1導電型の半導体基板1と、半導体基板1上に半導体基板1より低ドーピング濃度で形成された第1導電型の半導体層2と、半導体層2の表層に所定間隔を有して並置された第2導電型の第1の半導体領域3と、半導体層2および第1の半導体領域3上に形成され、半導体層2とはショットキ接触、第1の半導体領域3とはオーミック接触する第1の電極5と、半導体基板1の裏面に形成された第2の電極6と、を備え、第1の半導体領域3の幅Wp(μm)と半導体層2のドーピング濃度N(cm-3)とが、Wp>−72×ln(N)+2685の関係を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】p−i−n接合とショットキー接合を備えるダイオードを有する炭化珪素パワー半導体装置において、逆方向漏れ電流を抑制した上で、素子のオン抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】n型炭化珪素半導体基板上に設けられたn型エピタキシャル炭化珪素半導体層表面の一部領域にp型不純物をイオン注入し、p型不純物領域を形成する工程と、n型エピタキシャル炭化珪素半導体層表面に、n型エピタキシャル炭化珪素半導体層との間にショットキー障壁を形成する第1の金属層を堆積する工程と、第1の金属層上にアルミニウムを含有する第2の金属層を堆積する工程と、第2の金属層を堆積する工程の後に熱処理する工程とを有し、熱処理により第2の金属層に含有されるアルミニウムを選択的に前記p型不純物領域に拡散させることを特徴とする半導体装置の製造方法。

(もっと読む)

101 - 120 / 230

[ Back to top ]