Fターム[4M104FF32]の内容

Fターム[4M104FF32]に分類される特許

21 - 40 / 230

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高い逆方向耐圧VR及び低いリーク電流IRを維持したまま、順方向降下電圧VFを低くしたり、逆回復時間trrを短くしたりすることが可能な半導体装置を提供する。

【解決手段】n+型半導体層112とn−型半導体層114とを有する半導体基体110と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130とを備える半導体装置であって、半導体基体110には、n−型半導体層114の表面で濃度が最も高くなるように重金属としての白金が拡散されている。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および閾値電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有するSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。そして、ショットキーバリアダイオード1の閾値電圧Vthを0.3V〜0.7Vにし、定格電圧VRにおけるリーク電流Jrを1×10−9A/cm2〜1×10−4A/cm2にする。

(もっと読む)

半導体デバイス及びその製造方法

【課題】接合障壁ショットキーダイオード及びその製造方法を提供すること。

【解決手段】第1の導電型を有する半導体層と、この半導体層上にあり、半導体層と共にショットキー接合部を形成する金属接点と、半導体層内に半導体領域とを含んでいる。半導体領域と半導体層とが、第1のp−n接合部を、ショットキー接合部と並列に形成する。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、ショットキー接合部に隣接する半導体層内に空乏領域を発生させるように構成され、それによってショットキー接合部を通る逆漏れ電流が制限される。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、第1のp−n接合部のパンチスルーが、ショットキー接合部の降伏電圧よりも低い電圧で起こるように構成される。

(もっと読む)

炭化珪素半導体装置

【課題】少ない工程数で形成でき、耐熱性に優れた温度検出素子を備える炭化珪素(SiC)半導体装置を提供する。

【解決手段】SiC半導体装置は、SiC基板1に形成された半導体素子と、底面にバリアメタル14を備える配線層を用いて形成したソース電極15およびゲートパッド16と、その配線層のバリアメタル14の一部を用いて形成した測温抵抗体20を備える。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面の金属汚染を十分除去することにより、製造された炭化珪素半導体素子の初期特性を改善する。また、金属汚染を低減し、半導体装置の長期信頼性を向上する方法を提供する。

【解決手段】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面を酸化するステップと、該ステップにより炭化珪素表面に形成された二酸化シリコンを主成分とする膜を除去するステップとからなる炭化珪素表面の金属汚染除去工程を適用する。

(もっと読む)

半導体装置

【課題】本発明は、トレンチの設計自由度が損なわれることなく、プロセス条件に制約されることなく、電気的特性を向上することができる半導体装置を提供する。

【解決手段】半導体装置10は、第1の半導体領域1内のトレンチ15の底部に第4の半導体領域4を介して配設され、隣り合う同士において相互に離間され、第1の半導体領域1よりも高い不純物密度を有する第1の導電型の第5の半導体領域5を備える。

(もっと読む)

炭化珪素ダイオード

【課題】SiC製のJBSダイオードにおいて、サージ耐量を低下させることなく、通電劣化現象を抑制することのできる技術を提供する。

【解決手段】アクティブ領域のn−ドリフト層2内の表面側に、アノード電極4とオーミック接触する複数の第1p領域6と、第1p領域6とは分離され、アノード電極4とショットキー接触する複数の第2領域7とを形成し、アクティブ領域を(11−20)面に射影したときに、複数の第1p領域6を<1−100>方向に正孔の拡散長の2倍よりも広い間隔を置いて配置し、<1−100>方向に配置された第1p領域6と第1p領域6との間に第2p領域7を配置する。

(もっと読む)

半導体装置

【課題】順方向電圧降下の増大が抑制され、且つ順方向サージ耐量の高い、整流機能を有する半導体装置を提供する。

【解決手段】互いに対向する第1の主面110から第2の主面120に向かって延伸し、且つ底部が第2の主面120に達しない複数の溝部15が形成された第1導電型の半導体積層体10と、それぞれの外縁領域の一部が溝部15の側面に露出するように半導体積層体10の第1の主面110に互いに離間して埋め込まれた第2導電型の複数のアノード領域20と、アノード領域20の形成されていない領域において半導体積層体10とショットキー接合を形成し、且つアノード領域20とオーミック接合を形成して、半導体積層体10の第1の主面110に配置されたアノード電極30と、半導体積層体10の第2の主面120に配置されたカソード電極40とを備える。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】コンタクト抵抗を低減しつつ、イオン注入したp+層の消失を低減できる炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる炭化珪素半導体装置の製造方法は、(a)炭化珪素半導体基体表面にマスクとしての酸化膜マスク層21、酸化膜マスク層22を形成し、室温でイオン注入する工程と、(b)イオン注入を行った炭化珪素半導体基体表面を活性化アニールする工程と、(c)活性化アニール後の炭化珪素半導体基体表面を、ドライエッチングする工程と、(d)ドライエッチング後の炭化珪素半導体基体表面を犠牲酸化し、犠牲酸化膜5を形成する工程と、(e)犠牲酸化膜5を濃度10%以下の希フッ酸で5分以内のエッチングにより除去する工程と、(f)炭化珪素半導体基体裏面にオーミック電極6を、炭化珪素半導体基体表面の所定領域にショットキー電極7をそれぞれ形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

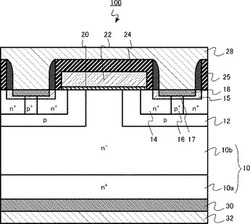

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、CMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供する。

【解決手段】n−型ドリフト層114と、n−型ドリフト層114における活性領域R1に形成したp型半導体材料からなる複数の柱状埋込層118と、周辺耐圧領域R2に形成したリング状の第2トレンチ122、第2トレンチ122の内面に形成した絶縁膜124及び第2トレンチ122の内部に絶縁膜124を介して形成した導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分のn−型ドリフト層114を空乏化させる周辺耐圧構造120と、周辺領域R3に形成したp型半導体材料からなる1又は2以上の第2柱状埋込層130とを備える半導体装置100。

(もっと読む)

半導体装置

【課題】順方向電圧の低減及びリーク電流の低減を図る半導体装置を提供する。

【解決手段】本実施形態に係る半導体装置は、第1導電形の第1半導体層と、第2導電形の領域であって、前記第1半導体層の第1主面の側に離間して設けられた複数の第2半導体領域と、第2導電形の領域であって、前記第1半導体層の前記第1主面の側に前記複数の第2半導体領域を囲むように設けられた第3半導体領域と、前記第1半導体層及び前記複数の第2半導体領域の上に設けられた第1電極と、を備える。前記第1半導体層は、第1部分と、前記第1部分よりも比抵抗が低く、前記第1部分と前記第1主面とのあいだであって、前記複数の第2半導体領域のあいだ、及び前記第3半導体領域の外側に設けられた第2部分と、を有する。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、サージ耐量が高く、順方向の電流密度を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面に選択的に設けられた第2導電形の第1の領域と、前記第1の領域に接続して前記第1の主面に選択的に設けられた第2導電形の第2の領域と、を備える。そして、前記半導体層と前記第1の領域とに接して設けられた第1の電極と、前記第2の領域に接して設けられた第2の電極と、前記半導体層の前記第1の主面とは反対の第2の主面側に電気的に接続された第3の電極とを備える。

(もっと読む)

半導体装置

【課題】リーク電流を抑制した半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、第1導電型の半導体層、複数のトレンチ、絶縁層、導電層、第1半導体拡散層、及びアノード電極を有する。半導体層は、半導体基板上に形成され第1の不純物濃度よりも小さい第2の不純物濃度を有する。複数のトレンチは、半導体層の上面から下方に延びるように半導体層中に形成されている。導電層は、絶縁層を介してトレンチを埋めるように形成され且つ半導体層の上面から第1の位置まで下方に延びる。第1半導体拡散層は、複数のトレンチの間に位置する半導体層の上面から第2の位置に達し且つ第2の不純物濃度より小さい第3の不純物濃度を有する。アノード電極は、第1半導体拡散層とショットキー接合されている。半導体層の上面から第2の位置までの長さは、半導体層の上面から第1の位置までの長さの1/2以下である。

(もっと読む)

ダイオードの製造方法

【課題】製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えること。

【解決手段】ダイオードの製造方法は、エピタキシャル層の表面にキャップ層を形成するキャップ層形成工程(S3)と、キャップ層が形成されている状態でドーパントを活性化させるアニール工程(S4)と、キャップ層を除去するキャップ層除去工程(S5)と、エッチング技術を利用してエピタキシャル層の表面を洗浄する洗浄工程(S6)と、エピタキシャル層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程(S7)と、を備えている。

(もっと読む)

21 - 40 / 230

[ Back to top ]