ダイオードの製造方法

【課題】製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えること。

【解決手段】ダイオードの製造方法は、エピタキシャル層の表面にキャップ層を形成するキャップ層形成工程(S3)と、キャップ層が形成されている状態でドーパントを活性化させるアニール工程(S4)と、キャップ層を除去するキャップ層除去工程(S5)と、エッチング技術を利用してエピタキシャル層の表面を洗浄する洗浄工程(S6)と、エピタキシャル層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程(S7)と、を備えている。

【解決手段】ダイオードの製造方法は、エピタキシャル層の表面にキャップ層を形成するキャップ層形成工程(S3)と、キャップ層が形成されている状態でドーパントを活性化させるアニール工程(S4)と、キャップ層を除去するキャップ層除去工程(S5)と、エッチング技術を利用してエピタキシャル層の表面を洗浄する洗浄工程(S6)と、エピタキシャル層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程(S7)と、を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ダイオードの製造方法に関する。

【背景技術】

【0002】

ダイオードの製造方法では、半導体基板上にn型のエピタキシャル層を結晶成長させる工程と、そのエピタキシャル層の表面部にドーパントを導入してp型領域を形成する工程と、導入したドーパントをアニール処理によって活性化させる工程が行われる。エピタキシャル層の表面部に形成されるp型領域は、ダイオードに必要な領域を構成する。例えば、p型領域は、終端領域を一巡するガードリング等の耐圧構造を構成するために形成されることがある。また、p型領域は、アノード領域を構成するために形成されることがある。半導体材料に炭化珪素が用いられる場合、エピタキシャル層に導入されたドーパントを活性化させるためには、高温のアニール処理が必要とされる。このため、炭化珪素のエピタキシャル層では、アニール処理中にエピタキシャル層の表面からシリコン原子が昇華し、表面荒れが増大することが知られている。

【0003】

このような表面荒れを抑えるために、アニール処理に先立って、エピタキシャル層の表面にキャップ層を形成する技術が知られている(特許文献1〜4)。キャップ層は、高温のアニール処理に対して安定な材料で形成されている。このため、エピタキシャル層の表面にキャップ層が形成されていると、アニール処理においてエピタキシャル層の表面からのシリコン原子の昇華を抑制することができ、エピタキシャル層の表面荒れを抑えることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−068428号公報

【特許文献2】特開2007−115875号公報

【特許文献3】特開2009−266969号公報

【特許文献4】特開2009−290160号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

表面荒れを抑えるために形成されたキャップ層は、最終的には除去する必要がある。例えば、キャップ層は、プラズマエッチング処理(アッシング処理ともいう)と犠牲酸化処理を利用して除去される。犠牲酸化処理は、酸素雰囲気下で実施され、プラズマエッチング処理で除去しきれないキャップ層を除去するために行われる。

【0006】

ところで、炭化珪素のエピタキシャル層には、螺旋転位及び刃状転位を含む貫通転位、さらに基底面内転位が多く存在することが知られている。上記したように、キャップ層を除去するために酸化処理を実施すると、エピタキシャル層の表面部の貫通転位及び基底内転位の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。エピタキシャル層の表面部にこのような酸化膜が形成されていると、エピタキシャル層の表面に形成されるアノード電極のコンタクト抵抗を増大させてしまう。このため、このような酸化膜は、アノード電極を形成するのに先立って、洗浄工程を利用して除去される。例えば、このような酸化膜は、ウェットエッチング処理を用いた洗浄工程を利用して除去される。このような洗浄工程を実施すると、エピタキシャル層の表面部には、貫通転位及び基底内転位の存在部位に応じて円錐状又は六角錐状のエッチピットが形成される。円錐状又は六角錐状のエッチピットは、ダイオードに逆バイアスが印加されたときに、リーク電流を発生させる原因となってしまう。

【0007】

特許文献2では、キャップ層を除去した後に、CMP(Chemical Mechanical Polishing)技術を利用して、エピタキシャル層の表面を研磨する技術を開示する。しかしながら、形成されるエッチピットの深さによっては、エピタキシャル層の表面部を相当程度に研磨しなければならない。例えば、エピタキシャル層の表面を研磨する量が多いと、エピタキシャル層の厚みが薄くなるので、ダイオードの耐圧が低下してしまう。このように、エピタキシャル層の厚みを大幅に変えてしまう処理は、半導体装置の特性を所望のものから逸脱させてしまうという問題がある。

【0008】

なお、エピタキシャル層の表面部に形成されるエッチピットは、キャップ層を除去するための酸化処理とその後の洗浄工程でのみ形成されるわけではない。例えば、キャップ層を利用しないでエピタキシャル層の表面荒れを抑える技術として、シラン雰囲気下でアニール処理を実施する技術が知られている。シラン雰囲気下でアニール処理を実施すると、エピタキシャル層の表面からのシリコン原子の昇華を抑制することができ、エピタキシャル層の表面荒れを抑えることができる。このような場合も、エピタキシャル層の表面にアノード電極を形成するのに先立って、パーティクル及び金属汚染等を除去するために、例えばRCA洗浄工程が実施される。特に、このRCA洗浄工程で用いられるSC−1洗浄液(アンモニアと過酸化水素水の混合液)に浸漬されると、エピタキシャル層の表面部には、貫通転位及び基底内転位の存在部位に応じて円錐状又は六角錐状のエッチピットが形成される。

【0009】

本明細書で開示される技術は、製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えることを目的としている。

【課題を解決するための手段】

【0010】

本発明者らは、エッチピットの底角に着目した。本発明者らは、リーク電流の大きさがエッチピットの底角に依存していることを突き止めた。

【0011】

図1及び2に、エッチピットの底角と深さのリーク電流依存性をシミュレーションした結果を示す。図1に示されるように、このシミュレーションで用いたショットキーダイオード1は、n+型の半導体基板2と、半導体基板2上に形成されるn−型のエピタキシャル層3を備えている。半導体基板2の裏面には、図示しないカソード電極が形成されており、そのカソード電極は半導体基板2の裏面にオーミック接触している。エピタキシャル層3の表面には、図示しないアノード電極が形成されており、そのアノード電極はエピタキシャル層3の表面にショットキー接触している。エピタキシャル層3の表面部には、円錐状のエッチピット4が形成されている。図示を省略したアノード電極は、エッチピット4内にも充填されている。半導体基板2は、ドーパント濃度を5.9×1018cm−3とし、厚みを350μmとした。エピタキシャル層3は、ドーパント濃度を5.0×1015cm−3とし、厚みを13μmとした。エッチピット4の密度を1.27×106個/cm2とした。アノード電極のショットキー障壁高さを1.2eVとした。このシミュレーションでは、逆バイアスとして1200Vを印加した。

【0012】

図2に示されるように、エッチピット4の深さ4bが同一の場合、エッチピット4の底角4aが大きいほどリーク電流が低下することが分かる。また、エッチピット4の底角4aが同一の場合、エッチピット4の深さ4bが浅いほどリーク電流が低下することが分かる。このように、リーク電流の大きさは、エッチピット4の底角4aと深さ4bの双方に依存している。

【0013】

通常、表面粗さの指標として算術平均荒さRaが用いられることが多い。算術平均荒さRaでは、エッチピット4のそれぞれの底角4aが変化しない場合、深さ4bが小さいほど、算術平均荒さRaが小さくなる。一方、エッチピット4のそれぞれの深さ4bが変化しない場合、底角4aが変化しても、算術平均荒さRaは変化しない。

【0014】

通常の技術志向では、エッチピット4に起因するリーク電流を抑えようとする場合、算術平均荒さRaを低下させようとする。このため、エッチピット4の深さ4bを低下させる処理、すなわち、エピタキシャル層3の表面部を研磨する処理を実施する。本明細書で開示される技術は、このような技術志向とは明白に異なる。本願明細書で開示される技術では、従来から指標として用いられていた算術平均荒さRaの低減を目的とする処理ではなく、エッチピット4の底角4aを大きくすることで、ダイオードのリーク電流を低減させることを特徴としている。

【0015】

本願明細書で開示されるダイオードの製造方法は、結晶成長工程とドーパント導入工程とアニール工程と洗浄工程と底部平滑化工程とを備えている。結晶成長工程では、半導体基板上に第1導電型の半導体層を結晶成長させる。ドーパント導入工程では、結晶成長工程の後に、半導体層の表面部の一部にドーパントを導入し、第2導電型領域を形成する。アニール工程では、ドーパント導入工程の後に、ドーパントを活性化させる。洗浄工程では、アニール工程の後に、エッチング技術を利用して半導体層の表面を洗浄する。底部平滑化工程では、洗浄工程の後に、半導体層の表面部に形成されているエッチピットの底部を平滑化させる。上記製造方法によると、エッチピットの底部が平滑化されているので、エッチピットの底角が実質的に増大し、製造されるダイオードのリーク電流が抑制される。

【0016】

上記製造方法は、キャップ層形成工程とキャップ層除去工程をさらに備えていてもよい。キャップ層形成工程では、ドーパント導入工程とアニール工程の間に、半導体層の表面にキャップ層を形成する。キャップ層除去工程では、アニール工程と洗浄工程の間に、キャップ層を除去する。この製造方法によると、キャップ層の除去とその後の洗浄工程で形成されるエッチピットに起因するリーク電流を抑制することができる。

【0017】

キャップ層は、アニール工程において、半導体層の表面から半導体層を構成する原子が昇華するのを抑制するのが望ましい。これにより、アニール工程において、半導体層の表面荒れを抑えることができる。

【0018】

底部平滑化工程は、水素を含む雰囲気下で熱処理を実施するのが望ましい。水素を含む雰囲気下で熱処理を実施すると、半導体層の厚みを維持しながらエッチピットの底部を平滑化させることができる。

【0019】

本願明細書で開示される製造方法は、底部平滑化工程の後に、半導体層の表面にアノード電極を形成する工程をさらに備えるのが望ましい。アノード電極が半導体層の表面部のエッチピットに充填されていると、リーク電流の発生が特に問題となる。本願明細書で開示される技術は、このような問題に対処することができる。より好ましくは、アノード電極が半導体層の表面にショットキー接触するのが望ましい。リーク電流の発生は、ショットキー接触の場合に起こり易く、このような場合に本願明細書で開示される技術は特に有用である。

【発明の効果】

【0020】

本願明細書で開示される技術によると、製造過程で半導体層に形成されるエッチピットに起因するリーク電流を抑えることができる。

【図面の簡単な説明】

【0021】

【図1】図1は、シミュレーションで用いたショットキーダイオードの構造を示す。

【図2】図2は、シミュレーション結果を示す。

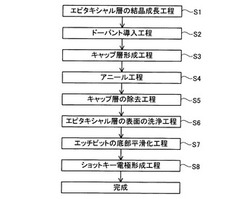

【図3】図3は、第1実施例のショットキーダイオードの製造工程の概略を示す。

【図4】図4は、第1実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図5】図5は、第1実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図6】図6は、第1実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図7】図7は、第1実施例のショットキーダイオードの製造過程の断面図を示す(4)。

【図8】図8は、第1実施例のショットキーダイオードの製造過程の断面図を示す(5)。

【図9】図9は、第1実施例のショットキーダイオードの製造過程の断面図を示す(6)。

【図10】図10は、エッチピットの底部が平滑化する様子を示す。

【図11】図11は、第1実施例のショットキーダイオードの製造過程の断面図を示す(7)。

【図12】図12は、第2実施例のショットキーダイオードの製造工程の概略を示す。

【図13】図13は、第2実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図14】図14は、第2実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図15】図15は、第2実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図16】図16は、第3実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図17】図17は、第3実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図18】図18は、第3実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図19】図19は、第3実施例のショットキーダイオードの製造過程の断面図を示す(4)。

【図20】図20は、第3実施例のショットキーダイオードの製造過程の断面図を示す(5)。

【図21】図21は、第3実施例のショットキーダイオードの製造過程の断面図を示す(6)。

【発明を実施するための形態】

【0022】

本願明細書で開示される技術の特徴を整理しておく。

(第1特徴) 本願明細書で開示される技術は、PINダイオード、ショットキーダイオード、ジャンクションバリアショットキーダイオードに有用である。

(第2特徴) 半導体基板は、その上に形成される半導体層と同一の半導体材料であるのが望ましい。例えば、炭化珪素の半導体基板上に炭化珪素の半導体層をエピタキシャル成長させるのが望ましい。

(第3特徴) 製造される半導体装置が縦型の場合、半導体基板はドーパントを含んでいるのが望ましい。

(第4特徴) 半導体層の表面部に形成される第2導電型領域は、ダイオードに必要な領域を構成する。例えば、第2導電型領域は、終端領域に形成される耐圧構造であってもよい。耐圧構造には、ガードリング、リサーフ層等が含まれる。また、第2導電型領域は、素子領域に形成されるアノード領域であってもよい。

(第5特徴) キャップ層は、1800℃のアニール工程において、融解及び昇華しない安定した材料であり、且つ半導体層内に拡散しない材料であるのが望ましい。典型的には、キャップ層には、炭素を原料とするカーボン膜が用いられてもよく、例えば、ダイヤモンドライクカーボン膜(DLC)、有機レジストを炭化したカーボン膜が用いられてもよい。あるいは、キャップ層には、炭化遷移金属が用いられてもよく、例えば、炭化タンタル、炭化チタンが用いられてもよい。

(第6特徴) キャップ層の除去には、様々な手法を採用することできる。キャップ層が炭素を含むカーボン膜の場合、キャップ層を酸素と反応させて一酸化炭素又は二酸化炭素として除去するのが望ましい。典型的には、キャップ層の除去には、酸素プラズマを用いたプラズマエッチング処理、酸素雰囲気下での犠牲酸化処理を採用するのが望ましい。また、キャップ層が炭化遷移金属の場合、キャップ層を酸化した後に酸溶液でエッチング除去するのが望ましい。例えば、キャップ層が炭化タンタルの場合、酸素雰囲気下で酸化した後に燐酸を含んだ溶液でエッチングしてもよい。キャップ層が炭化チタンの場合、酸素雰囲気下で酸化した後に塩酸と過酸化水素水の混合液でエッチングしてもよい。

(第7特徴)エッチピットの底部を平滑化させる底部平滑化工程には、半導体層の表面をマイグレーション(原子拡散)させる様々な手法を採用することができる。典型的には、底部平滑化工程には、減圧水素雰囲気下での熱処理、シランとアルゴン混合雰囲気下での熱処理と水素雰囲気下での熱処理の組合わせを採用するのが望ましい。

【実施例】

【0023】

以下、図面を参照して各実施例を説明する。なお、各実施例において、共通する構成要素に関して共通の符号を付し、その説明を省略することがある。また、共通する工程に関しては、その説明を省略することがある。

【0024】

(第1実施例)

図3に、第1実施例のショットキーバリアダイオードを製造する工程の概略を示す。以下、図4〜図10を参照して、第1実施例のショットキーバリアダイオードの製造方法を説明する。まず、図4に示されるように、n+型の半導体基板20を用意する。半導体基板20は、4H−SiC(0001)Si面の1〜8°オフ基板であり、ドーピング濃度が約1×1018〜1×1020cm−3であり、厚みが約350μmである。

【0025】

次に、図4に示されるように、エピタキシャル成長技術を利用して、半導体基板20上に炭化珪素のn−型エピタキシャル層30を結晶成長させる(図3のステップS1)。エピタキシャル層30の厚みは約8〜13μmであり、そのドーピング濃度は約1×1015〜1×1016cm−3である。エピタキシャル層30には、貫通転位40が裏面から表面まで伸びている。

【0026】

次に、図5に示されるように、エピタキシャル層30の表面にマスク53を形成する。具体的には、熱酸化技術を利用して、エピタキシャル層30の表面に酸化シリコンの酸化膜52を形成した後に、酸化膜52の表面にレジスト54をパターニングし、終端領域に対応した範囲の一部に開孔を有するように酸化膜52の一部をエッチングする。マスク53に形成される開孔の位置は、終端領域を一巡するガードリングの位置に対応している。酸化膜52がパターニングされた後に、酸化膜52上のレジスト54は除去される。

【0027】

次に、図6に示されるように、イオン注入技術を利用して、エピタキシャル層30の表面部の一部にアルミニウム又はボロンのドーパントを導入し、ガードリング60を形成する(図3のステップS2)。このときの半導体基板20の温度は500℃以下に保たれており、イオン注入に伴うアモルファス化を抑制している。ドーパントが導入された後に、酸化膜52は除去される。

【0028】

次に、図7に示されるように、CVD(Chemical Vapor Deposition)技術を利用して、エピタキシャル層30の表面にキャップ層70を形成する(図3のステップS3)。この例では、キャップ層70の材料には、炭素を材料とするカーボン膜が用いられる。次に、エピタキシャル層30の表面にキャップ層70が存在した状態で、アニール処理を実施する(図3のステップS4)。アニール処理では、半導体基板20の温度が1600°以上であり、処理時間は約5〜60分である。このアニール処理により、ガードリング60を形成するために導入されたドーパントが活性化する。なお、このアニール処理では、エピタキシャル層30の表面にキャップ層70が形成されているので、エピタキシャル層30の表面からシリコン原子が昇華する現象が抑えられ、エピタキシャル層30の表面荒れが抑えられる。

【0029】

次に、図8に示されるように、酸素プラズマエッチング技術を利用して、キャップ層70を除去する(図3のステップS5)。さらに、熱酸化技術を利用して、プラズマエッチング処理で除去しきれないキャップ層70を完全に除去する。このとき、エピタキシャル層30の表面部の貫通転位40の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。次に、この酸化膜をフッ酸溶液で除去し、エピタキシャル層30の表面を洗浄する(図3のステップS6)。この洗浄工程を経ると、図8に示されるように、エピタキシャル層30の表面部には、貫通転位40の存在部分に応じてエッチピット42が形成される。

【0030】

図8では、3つのエッチピット42a,42b,42cが形成される様子を示す。エッチピット42a,42b,42cは、貫通転位40の状態に応じて、その深さ及び底角が異なる。この例では、エッチピット42bの深さ及び底角が最も大きい。例えば、エピタキシャル層30の表面部からエッチピット42a,42b,42cを完全に除去しようとすれば、最も深いエッチピット42bの深さまでエピタキシャル層30の表面部を研磨しなければならない。このような処理を実施すると、エピタキシャル層30の厚みが相当程度に変化するので、製造されるダイオードの特性が所望のものから逸脱してしまう。本実施例の製造方法では、エピタキシャル層30を研磨する工程を実施しない。以下で説明するように、本実施例の製造方法では、ガスエッチング技術を利用して、エッチピット42の底角を実質的に増大させる。

【0031】

次に、図9に示されるように、水素を含む雰囲気下で熱処理を実施し、エッチピット42の底部を平滑化させる(図3のステップS7)。熱処理では、半導体基板20の温度が1600°〜1700°であり、熱処理時間は約5〜30分である。また、この熱処理は、減圧下で行うのが望ましく、この例では、チャンバー内の圧力が約300Torr以下である。

【0032】

この工程は、図10のエッチピット42bの拡大断面図を参照してより詳細に説明する。図10の破線は底部平滑化工程前のエッチピット42bの形態であり、図10の実線は底部平滑化工程後のエッチピット42bの形態である。図10に示されるように、底部平滑化工程の前後において、エッチピット42bの底部は平滑化されており、実質的な低角が増大している。なお、ここでいう平滑化とは、エッチピットの縦断面において、斜辺に対して引いた接線の垂直線に対する角度が、少なくとも最深部周辺において、最深部に向けて増大することをいう。

【0033】

減圧水素雰囲気下で熱処理を実施すると、円錐状のエッチピット42bの底部が平滑化する。この処理では、エッチピット42bの深さは実質的に変化しないので、算術平均粗さRaは実質的に変化しない。なお、エッチピット42の底部を平滑化させるためには、上記処理に代えて、シランとアルゴン混合雰囲気下で1600°〜1800°の熱処理を実施し、その後に水素雰囲気下で1400°〜1500°の熱処理を実施してもよい。

【0034】

次に、図11に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する(図3のステップS8)。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0035】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の底角が、減圧水素雰囲気下の高温熱処理によって実質的に増大されている。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、減圧水素雰囲気下の高温熱処理では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0036】

(第2実施例)

図12に、第2実施例のショットキーバリアダイオードの製造工程の概略を示す。第2実施例のショットキーバリアダイオードの製造方法は、第1実施例のステップS6とS7の間に、エッチピットを充填するための工程が付加されていることを特徴としている。以下、図13〜図15を参照して、第2実施例のショットキーバリアダイオードの製造方法を説明する。エッチピット42の底部を平滑化させる工程までは第1実施例と共通である。

【0037】

次に、図13に示されるように、エピタキシャル成長技術を利用して、エピタキシャル層30上に炭化珪素の第2エピタキシャル層32を成長させる(図12のステップS11)。第2エピタキシャル層32の厚みは、特に制限されないが、好ましくは最も深いエッチピット42bが完全に充填されるように調整されるのが望ましい。なお、この例では、第2エピタキシャル層32の厚みは、エッチピット42a,42cが完全に充填される一方で、エッチピット42bは完全に充填されない場合を例示する。また、第2エピタキシャル層32のドーピング濃度は、エピタキシャル層30と同一であるのが望ましい。

【0038】

次に、図14に示されるように、CMP(Chemical Mechanical Polishing)技術を利用して、第2エピタキシャル層32を研磨する(図12のステップS12)。研磨する厚みは、第2エピタキシャル層32の厚み以下であるのが望ましく、より好ましくは第2エピタキシャル層32の厚みと同一であるのが望ましい。さらに、必要に応じて、ドライエッチング技術を利用して、エピタキシャル層30の表面部に形成された変質層を除去してもよい。これにより、図14に示されるように、エッチピット42内には、第2エピタキシャル層32の一部が残存する。これにより、エッチピット42a,42cは第2エピタキシャル層32で完全に充填され、エッチピット42bの一部は第2エピタキシャル層32で充填される。このように、第2エピタキシャル層32の形成及び研磨を実施することで、エッチピット42の深さは浅くなる。なお、第2エピタキシャル層32の研磨工程では、第2エピタキシャル層32の厚みを超えて、エピタキシャル層30の表面部の一部を研磨してもよい。研磨工程に先立ってエッチピット42の深さが浅く調整されているので、エッチピット42を完全に除去するのに要する研磨量が抑えられ、エピタキシャル層30の厚みが維持される。

【0039】

次に、図15に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0040】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の深さが、第2エピタキシャル層32の形成及び研磨によって小さくなる。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、第2エピタキシャル層32の形成及び研磨では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0041】

(第3実施例)

図16〜図21を参照して、第3実施例のジャンクションバリアショットキーダイオードの製造方法を説明する。エピタキシャル層30を成長させる工程までは第1実施例と共通である。

【0042】

次に、図16に示されるように、エピタキシャル層30の表面にマスク57を形成する。具体的には、熱酸化技術を利用して、エピタキシャル層30の表面に酸化シリコンの酸化膜56を形成した後に、酸化膜56の表面にレジスト58をパターニングし、素子領域に対応した範囲の一部及び終端領域に対応した範囲の一部に開孔を有するように酸化膜56の一部をエッチングする。マスク57に形成される開孔の位置は、素子領域に分散して形成されるp型拡散領域及び終端領域を一巡するガードリングの位置に対応している。酸化膜56がパターニングされた後に、酸化膜56上のレジスト58は除去される。

【0043】

次に、図17に示されるように、イオン注入技術を利用して、エピタキシャル層30の表面部の一部にアルミニウム又はボロンのドーパントを導入し、p型拡散領域62(アノード領域ということもできる)及びガードリング60を形成する。このときの半導体基板20の温度は500℃以下に保たれており、イオン注入に伴うアモルファス化を抑制している。ドーパントが導入された後に、酸化膜56は除去される。このように、本実施例では、p型拡散領域62及びガードリング60を共通の工程で作製することを1つの特徴としている。

【0044】

次に、図18に示されるように、CVD(Chemical Vapor Deposition)技術を利用して、エピタキシャル層30の表面にキャップ層70を形成する。次に、エピタキシャル層30の表面にキャップ層70が存在した状態で、アニール処理を実施し、p型拡散領域62及びガードリング60を形成するために導入されたドーパントを活性化させる。

【0045】

次に、図19に示されるように、酸素プラズマエッチング技術を利用して、キャップ層70を除去する。さらに、熱酸化技術を利用して、プラズマエッチング処理で除去しきれないキャップ層70を完全に除去する。このとき、エピタキシャル層30の表面部の貫通転位40の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。次に、この酸化膜をフッ酸溶液で除去し、エピタキシャル層30の表面を洗浄する。この洗浄工程を経ると、図19に示されるように、エピタキシャル層30の表面部には、貫通転位40の存在部分に応じてエッチピット42が形成される。

【0046】

次に、図20に示されるように、減圧水素雰囲気下で熱処理を実施し、エッチピット42の底部を平滑化させる。

【0047】

次に、図21に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0048】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の底部が、減圧水素雰囲気下の高温熱処理によって実質的に増大されている。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、減圧水素雰囲気下の高温熱処理では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるジャンクションバリアショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0049】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0050】

20:半導体基板

30:エピタキシャル層(半導体層の一例)

32:第2エピタキシャル層

40:貫通転位

42,42a,42b,42c:エッチピット

60:ガードリング

62:p型拡散領域

70:キャップ層

84:ショットキー電極部

85:アノード電極

86:配線電極部

【技術分野】

【0001】

本発明は、ダイオードの製造方法に関する。

【背景技術】

【0002】

ダイオードの製造方法では、半導体基板上にn型のエピタキシャル層を結晶成長させる工程と、そのエピタキシャル層の表面部にドーパントを導入してp型領域を形成する工程と、導入したドーパントをアニール処理によって活性化させる工程が行われる。エピタキシャル層の表面部に形成されるp型領域は、ダイオードに必要な領域を構成する。例えば、p型領域は、終端領域を一巡するガードリング等の耐圧構造を構成するために形成されることがある。また、p型領域は、アノード領域を構成するために形成されることがある。半導体材料に炭化珪素が用いられる場合、エピタキシャル層に導入されたドーパントを活性化させるためには、高温のアニール処理が必要とされる。このため、炭化珪素のエピタキシャル層では、アニール処理中にエピタキシャル層の表面からシリコン原子が昇華し、表面荒れが増大することが知られている。

【0003】

このような表面荒れを抑えるために、アニール処理に先立って、エピタキシャル層の表面にキャップ層を形成する技術が知られている(特許文献1〜4)。キャップ層は、高温のアニール処理に対して安定な材料で形成されている。このため、エピタキシャル層の表面にキャップ層が形成されていると、アニール処理においてエピタキシャル層の表面からのシリコン原子の昇華を抑制することができ、エピタキシャル層の表面荒れを抑えることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−068428号公報

【特許文献2】特開2007−115875号公報

【特許文献3】特開2009−266969号公報

【特許文献4】特開2009−290160号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

表面荒れを抑えるために形成されたキャップ層は、最終的には除去する必要がある。例えば、キャップ層は、プラズマエッチング処理(アッシング処理ともいう)と犠牲酸化処理を利用して除去される。犠牲酸化処理は、酸素雰囲気下で実施され、プラズマエッチング処理で除去しきれないキャップ層を除去するために行われる。

【0006】

ところで、炭化珪素のエピタキシャル層には、螺旋転位及び刃状転位を含む貫通転位、さらに基底面内転位が多く存在することが知られている。上記したように、キャップ層を除去するために酸化処理を実施すると、エピタキシャル層の表面部の貫通転位及び基底内転位の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。エピタキシャル層の表面部にこのような酸化膜が形成されていると、エピタキシャル層の表面に形成されるアノード電極のコンタクト抵抗を増大させてしまう。このため、このような酸化膜は、アノード電極を形成するのに先立って、洗浄工程を利用して除去される。例えば、このような酸化膜は、ウェットエッチング処理を用いた洗浄工程を利用して除去される。このような洗浄工程を実施すると、エピタキシャル層の表面部には、貫通転位及び基底内転位の存在部位に応じて円錐状又は六角錐状のエッチピットが形成される。円錐状又は六角錐状のエッチピットは、ダイオードに逆バイアスが印加されたときに、リーク電流を発生させる原因となってしまう。

【0007】

特許文献2では、キャップ層を除去した後に、CMP(Chemical Mechanical Polishing)技術を利用して、エピタキシャル層の表面を研磨する技術を開示する。しかしながら、形成されるエッチピットの深さによっては、エピタキシャル層の表面部を相当程度に研磨しなければならない。例えば、エピタキシャル層の表面を研磨する量が多いと、エピタキシャル層の厚みが薄くなるので、ダイオードの耐圧が低下してしまう。このように、エピタキシャル層の厚みを大幅に変えてしまう処理は、半導体装置の特性を所望のものから逸脱させてしまうという問題がある。

【0008】

なお、エピタキシャル層の表面部に形成されるエッチピットは、キャップ層を除去するための酸化処理とその後の洗浄工程でのみ形成されるわけではない。例えば、キャップ層を利用しないでエピタキシャル層の表面荒れを抑える技術として、シラン雰囲気下でアニール処理を実施する技術が知られている。シラン雰囲気下でアニール処理を実施すると、エピタキシャル層の表面からのシリコン原子の昇華を抑制することができ、エピタキシャル層の表面荒れを抑えることができる。このような場合も、エピタキシャル層の表面にアノード電極を形成するのに先立って、パーティクル及び金属汚染等を除去するために、例えばRCA洗浄工程が実施される。特に、このRCA洗浄工程で用いられるSC−1洗浄液(アンモニアと過酸化水素水の混合液)に浸漬されると、エピタキシャル層の表面部には、貫通転位及び基底内転位の存在部位に応じて円錐状又は六角錐状のエッチピットが形成される。

【0009】

本明細書で開示される技術は、製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えることを目的としている。

【課題を解決するための手段】

【0010】

本発明者らは、エッチピットの底角に着目した。本発明者らは、リーク電流の大きさがエッチピットの底角に依存していることを突き止めた。

【0011】

図1及び2に、エッチピットの底角と深さのリーク電流依存性をシミュレーションした結果を示す。図1に示されるように、このシミュレーションで用いたショットキーダイオード1は、n+型の半導体基板2と、半導体基板2上に形成されるn−型のエピタキシャル層3を備えている。半導体基板2の裏面には、図示しないカソード電極が形成されており、そのカソード電極は半導体基板2の裏面にオーミック接触している。エピタキシャル層3の表面には、図示しないアノード電極が形成されており、そのアノード電極はエピタキシャル層3の表面にショットキー接触している。エピタキシャル層3の表面部には、円錐状のエッチピット4が形成されている。図示を省略したアノード電極は、エッチピット4内にも充填されている。半導体基板2は、ドーパント濃度を5.9×1018cm−3とし、厚みを350μmとした。エピタキシャル層3は、ドーパント濃度を5.0×1015cm−3とし、厚みを13μmとした。エッチピット4の密度を1.27×106個/cm2とした。アノード電極のショットキー障壁高さを1.2eVとした。このシミュレーションでは、逆バイアスとして1200Vを印加した。

【0012】

図2に示されるように、エッチピット4の深さ4bが同一の場合、エッチピット4の底角4aが大きいほどリーク電流が低下することが分かる。また、エッチピット4の底角4aが同一の場合、エッチピット4の深さ4bが浅いほどリーク電流が低下することが分かる。このように、リーク電流の大きさは、エッチピット4の底角4aと深さ4bの双方に依存している。

【0013】

通常、表面粗さの指標として算術平均荒さRaが用いられることが多い。算術平均荒さRaでは、エッチピット4のそれぞれの底角4aが変化しない場合、深さ4bが小さいほど、算術平均荒さRaが小さくなる。一方、エッチピット4のそれぞれの深さ4bが変化しない場合、底角4aが変化しても、算術平均荒さRaは変化しない。

【0014】

通常の技術志向では、エッチピット4に起因するリーク電流を抑えようとする場合、算術平均荒さRaを低下させようとする。このため、エッチピット4の深さ4bを低下させる処理、すなわち、エピタキシャル層3の表面部を研磨する処理を実施する。本明細書で開示される技術は、このような技術志向とは明白に異なる。本願明細書で開示される技術では、従来から指標として用いられていた算術平均荒さRaの低減を目的とする処理ではなく、エッチピット4の底角4aを大きくすることで、ダイオードのリーク電流を低減させることを特徴としている。

【0015】

本願明細書で開示されるダイオードの製造方法は、結晶成長工程とドーパント導入工程とアニール工程と洗浄工程と底部平滑化工程とを備えている。結晶成長工程では、半導体基板上に第1導電型の半導体層を結晶成長させる。ドーパント導入工程では、結晶成長工程の後に、半導体層の表面部の一部にドーパントを導入し、第2導電型領域を形成する。アニール工程では、ドーパント導入工程の後に、ドーパントを活性化させる。洗浄工程では、アニール工程の後に、エッチング技術を利用して半導体層の表面を洗浄する。底部平滑化工程では、洗浄工程の後に、半導体層の表面部に形成されているエッチピットの底部を平滑化させる。上記製造方法によると、エッチピットの底部が平滑化されているので、エッチピットの底角が実質的に増大し、製造されるダイオードのリーク電流が抑制される。

【0016】

上記製造方法は、キャップ層形成工程とキャップ層除去工程をさらに備えていてもよい。キャップ層形成工程では、ドーパント導入工程とアニール工程の間に、半導体層の表面にキャップ層を形成する。キャップ層除去工程では、アニール工程と洗浄工程の間に、キャップ層を除去する。この製造方法によると、キャップ層の除去とその後の洗浄工程で形成されるエッチピットに起因するリーク電流を抑制することができる。

【0017】

キャップ層は、アニール工程において、半導体層の表面から半導体層を構成する原子が昇華するのを抑制するのが望ましい。これにより、アニール工程において、半導体層の表面荒れを抑えることができる。

【0018】

底部平滑化工程は、水素を含む雰囲気下で熱処理を実施するのが望ましい。水素を含む雰囲気下で熱処理を実施すると、半導体層の厚みを維持しながらエッチピットの底部を平滑化させることができる。

【0019】

本願明細書で開示される製造方法は、底部平滑化工程の後に、半導体層の表面にアノード電極を形成する工程をさらに備えるのが望ましい。アノード電極が半導体層の表面部のエッチピットに充填されていると、リーク電流の発生が特に問題となる。本願明細書で開示される技術は、このような問題に対処することができる。より好ましくは、アノード電極が半導体層の表面にショットキー接触するのが望ましい。リーク電流の発生は、ショットキー接触の場合に起こり易く、このような場合に本願明細書で開示される技術は特に有用である。

【発明の効果】

【0020】

本願明細書で開示される技術によると、製造過程で半導体層に形成されるエッチピットに起因するリーク電流を抑えることができる。

【図面の簡単な説明】

【0021】

【図1】図1は、シミュレーションで用いたショットキーダイオードの構造を示す。

【図2】図2は、シミュレーション結果を示す。

【図3】図3は、第1実施例のショットキーダイオードの製造工程の概略を示す。

【図4】図4は、第1実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図5】図5は、第1実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図6】図6は、第1実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図7】図7は、第1実施例のショットキーダイオードの製造過程の断面図を示す(4)。

【図8】図8は、第1実施例のショットキーダイオードの製造過程の断面図を示す(5)。

【図9】図9は、第1実施例のショットキーダイオードの製造過程の断面図を示す(6)。

【図10】図10は、エッチピットの底部が平滑化する様子を示す。

【図11】図11は、第1実施例のショットキーダイオードの製造過程の断面図を示す(7)。

【図12】図12は、第2実施例のショットキーダイオードの製造工程の概略を示す。

【図13】図13は、第2実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図14】図14は、第2実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図15】図15は、第2実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図16】図16は、第3実施例のショットキーダイオードの製造過程の断面図を示す(1)。

【図17】図17は、第3実施例のショットキーダイオードの製造過程の断面図を示す(2)。

【図18】図18は、第3実施例のショットキーダイオードの製造過程の断面図を示す(3)。

【図19】図19は、第3実施例のショットキーダイオードの製造過程の断面図を示す(4)。

【図20】図20は、第3実施例のショットキーダイオードの製造過程の断面図を示す(5)。

【図21】図21は、第3実施例のショットキーダイオードの製造過程の断面図を示す(6)。

【発明を実施するための形態】

【0022】

本願明細書で開示される技術の特徴を整理しておく。

(第1特徴) 本願明細書で開示される技術は、PINダイオード、ショットキーダイオード、ジャンクションバリアショットキーダイオードに有用である。

(第2特徴) 半導体基板は、その上に形成される半導体層と同一の半導体材料であるのが望ましい。例えば、炭化珪素の半導体基板上に炭化珪素の半導体層をエピタキシャル成長させるのが望ましい。

(第3特徴) 製造される半導体装置が縦型の場合、半導体基板はドーパントを含んでいるのが望ましい。

(第4特徴) 半導体層の表面部に形成される第2導電型領域は、ダイオードに必要な領域を構成する。例えば、第2導電型領域は、終端領域に形成される耐圧構造であってもよい。耐圧構造には、ガードリング、リサーフ層等が含まれる。また、第2導電型領域は、素子領域に形成されるアノード領域であってもよい。

(第5特徴) キャップ層は、1800℃のアニール工程において、融解及び昇華しない安定した材料であり、且つ半導体層内に拡散しない材料であるのが望ましい。典型的には、キャップ層には、炭素を原料とするカーボン膜が用いられてもよく、例えば、ダイヤモンドライクカーボン膜(DLC)、有機レジストを炭化したカーボン膜が用いられてもよい。あるいは、キャップ層には、炭化遷移金属が用いられてもよく、例えば、炭化タンタル、炭化チタンが用いられてもよい。

(第6特徴) キャップ層の除去には、様々な手法を採用することできる。キャップ層が炭素を含むカーボン膜の場合、キャップ層を酸素と反応させて一酸化炭素又は二酸化炭素として除去するのが望ましい。典型的には、キャップ層の除去には、酸素プラズマを用いたプラズマエッチング処理、酸素雰囲気下での犠牲酸化処理を採用するのが望ましい。また、キャップ層が炭化遷移金属の場合、キャップ層を酸化した後に酸溶液でエッチング除去するのが望ましい。例えば、キャップ層が炭化タンタルの場合、酸素雰囲気下で酸化した後に燐酸を含んだ溶液でエッチングしてもよい。キャップ層が炭化チタンの場合、酸素雰囲気下で酸化した後に塩酸と過酸化水素水の混合液でエッチングしてもよい。

(第7特徴)エッチピットの底部を平滑化させる底部平滑化工程には、半導体層の表面をマイグレーション(原子拡散)させる様々な手法を採用することができる。典型的には、底部平滑化工程には、減圧水素雰囲気下での熱処理、シランとアルゴン混合雰囲気下での熱処理と水素雰囲気下での熱処理の組合わせを採用するのが望ましい。

【実施例】

【0023】

以下、図面を参照して各実施例を説明する。なお、各実施例において、共通する構成要素に関して共通の符号を付し、その説明を省略することがある。また、共通する工程に関しては、その説明を省略することがある。

【0024】

(第1実施例)

図3に、第1実施例のショットキーバリアダイオードを製造する工程の概略を示す。以下、図4〜図10を参照して、第1実施例のショットキーバリアダイオードの製造方法を説明する。まず、図4に示されるように、n+型の半導体基板20を用意する。半導体基板20は、4H−SiC(0001)Si面の1〜8°オフ基板であり、ドーピング濃度が約1×1018〜1×1020cm−3であり、厚みが約350μmである。

【0025】

次に、図4に示されるように、エピタキシャル成長技術を利用して、半導体基板20上に炭化珪素のn−型エピタキシャル層30を結晶成長させる(図3のステップS1)。エピタキシャル層30の厚みは約8〜13μmであり、そのドーピング濃度は約1×1015〜1×1016cm−3である。エピタキシャル層30には、貫通転位40が裏面から表面まで伸びている。

【0026】

次に、図5に示されるように、エピタキシャル層30の表面にマスク53を形成する。具体的には、熱酸化技術を利用して、エピタキシャル層30の表面に酸化シリコンの酸化膜52を形成した後に、酸化膜52の表面にレジスト54をパターニングし、終端領域に対応した範囲の一部に開孔を有するように酸化膜52の一部をエッチングする。マスク53に形成される開孔の位置は、終端領域を一巡するガードリングの位置に対応している。酸化膜52がパターニングされた後に、酸化膜52上のレジスト54は除去される。

【0027】

次に、図6に示されるように、イオン注入技術を利用して、エピタキシャル層30の表面部の一部にアルミニウム又はボロンのドーパントを導入し、ガードリング60を形成する(図3のステップS2)。このときの半導体基板20の温度は500℃以下に保たれており、イオン注入に伴うアモルファス化を抑制している。ドーパントが導入された後に、酸化膜52は除去される。

【0028】

次に、図7に示されるように、CVD(Chemical Vapor Deposition)技術を利用して、エピタキシャル層30の表面にキャップ層70を形成する(図3のステップS3)。この例では、キャップ層70の材料には、炭素を材料とするカーボン膜が用いられる。次に、エピタキシャル層30の表面にキャップ層70が存在した状態で、アニール処理を実施する(図3のステップS4)。アニール処理では、半導体基板20の温度が1600°以上であり、処理時間は約5〜60分である。このアニール処理により、ガードリング60を形成するために導入されたドーパントが活性化する。なお、このアニール処理では、エピタキシャル層30の表面にキャップ層70が形成されているので、エピタキシャル層30の表面からシリコン原子が昇華する現象が抑えられ、エピタキシャル層30の表面荒れが抑えられる。

【0029】

次に、図8に示されるように、酸素プラズマエッチング技術を利用して、キャップ層70を除去する(図3のステップS5)。さらに、熱酸化技術を利用して、プラズマエッチング処理で除去しきれないキャップ層70を完全に除去する。このとき、エピタキシャル層30の表面部の貫通転位40の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。次に、この酸化膜をフッ酸溶液で除去し、エピタキシャル層30の表面を洗浄する(図3のステップS6)。この洗浄工程を経ると、図8に示されるように、エピタキシャル層30の表面部には、貫通転位40の存在部分に応じてエッチピット42が形成される。

【0030】

図8では、3つのエッチピット42a,42b,42cが形成される様子を示す。エッチピット42a,42b,42cは、貫通転位40の状態に応じて、その深さ及び底角が異なる。この例では、エッチピット42bの深さ及び底角が最も大きい。例えば、エピタキシャル層30の表面部からエッチピット42a,42b,42cを完全に除去しようとすれば、最も深いエッチピット42bの深さまでエピタキシャル層30の表面部を研磨しなければならない。このような処理を実施すると、エピタキシャル層30の厚みが相当程度に変化するので、製造されるダイオードの特性が所望のものから逸脱してしまう。本実施例の製造方法では、エピタキシャル層30を研磨する工程を実施しない。以下で説明するように、本実施例の製造方法では、ガスエッチング技術を利用して、エッチピット42の底角を実質的に増大させる。

【0031】

次に、図9に示されるように、水素を含む雰囲気下で熱処理を実施し、エッチピット42の底部を平滑化させる(図3のステップS7)。熱処理では、半導体基板20の温度が1600°〜1700°であり、熱処理時間は約5〜30分である。また、この熱処理は、減圧下で行うのが望ましく、この例では、チャンバー内の圧力が約300Torr以下である。

【0032】

この工程は、図10のエッチピット42bの拡大断面図を参照してより詳細に説明する。図10の破線は底部平滑化工程前のエッチピット42bの形態であり、図10の実線は底部平滑化工程後のエッチピット42bの形態である。図10に示されるように、底部平滑化工程の前後において、エッチピット42bの底部は平滑化されており、実質的な低角が増大している。なお、ここでいう平滑化とは、エッチピットの縦断面において、斜辺に対して引いた接線の垂直線に対する角度が、少なくとも最深部周辺において、最深部に向けて増大することをいう。

【0033】

減圧水素雰囲気下で熱処理を実施すると、円錐状のエッチピット42bの底部が平滑化する。この処理では、エッチピット42bの深さは実質的に変化しないので、算術平均粗さRaは実質的に変化しない。なお、エッチピット42の底部を平滑化させるためには、上記処理に代えて、シランとアルゴン混合雰囲気下で1600°〜1800°の熱処理を実施し、その後に水素雰囲気下で1400°〜1500°の熱処理を実施してもよい。

【0034】

次に、図11に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する(図3のステップS8)。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0035】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の底角が、減圧水素雰囲気下の高温熱処理によって実質的に増大されている。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、減圧水素雰囲気下の高温熱処理では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0036】

(第2実施例)

図12に、第2実施例のショットキーバリアダイオードの製造工程の概略を示す。第2実施例のショットキーバリアダイオードの製造方法は、第1実施例のステップS6とS7の間に、エッチピットを充填するための工程が付加されていることを特徴としている。以下、図13〜図15を参照して、第2実施例のショットキーバリアダイオードの製造方法を説明する。エッチピット42の底部を平滑化させる工程までは第1実施例と共通である。

【0037】

次に、図13に示されるように、エピタキシャル成長技術を利用して、エピタキシャル層30上に炭化珪素の第2エピタキシャル層32を成長させる(図12のステップS11)。第2エピタキシャル層32の厚みは、特に制限されないが、好ましくは最も深いエッチピット42bが完全に充填されるように調整されるのが望ましい。なお、この例では、第2エピタキシャル層32の厚みは、エッチピット42a,42cが完全に充填される一方で、エッチピット42bは完全に充填されない場合を例示する。また、第2エピタキシャル層32のドーピング濃度は、エピタキシャル層30と同一であるのが望ましい。

【0038】

次に、図14に示されるように、CMP(Chemical Mechanical Polishing)技術を利用して、第2エピタキシャル層32を研磨する(図12のステップS12)。研磨する厚みは、第2エピタキシャル層32の厚み以下であるのが望ましく、より好ましくは第2エピタキシャル層32の厚みと同一であるのが望ましい。さらに、必要に応じて、ドライエッチング技術を利用して、エピタキシャル層30の表面部に形成された変質層を除去してもよい。これにより、図14に示されるように、エッチピット42内には、第2エピタキシャル層32の一部が残存する。これにより、エッチピット42a,42cは第2エピタキシャル層32で完全に充填され、エッチピット42bの一部は第2エピタキシャル層32で充填される。このように、第2エピタキシャル層32の形成及び研磨を実施することで、エッチピット42の深さは浅くなる。なお、第2エピタキシャル層32の研磨工程では、第2エピタキシャル層32の厚みを超えて、エピタキシャル層30の表面部の一部を研磨してもよい。研磨工程に先立ってエッチピット42の深さが浅く調整されているので、エッチピット42を完全に除去するのに要する研磨量が抑えられ、エピタキシャル層30の厚みが維持される。

【0039】

次に、図15に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0040】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の深さが、第2エピタキシャル層32の形成及び研磨によって小さくなる。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、第2エピタキシャル層32の形成及び研磨では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0041】

(第3実施例)

図16〜図21を参照して、第3実施例のジャンクションバリアショットキーダイオードの製造方法を説明する。エピタキシャル層30を成長させる工程までは第1実施例と共通である。

【0042】

次に、図16に示されるように、エピタキシャル層30の表面にマスク57を形成する。具体的には、熱酸化技術を利用して、エピタキシャル層30の表面に酸化シリコンの酸化膜56を形成した後に、酸化膜56の表面にレジスト58をパターニングし、素子領域に対応した範囲の一部及び終端領域に対応した範囲の一部に開孔を有するように酸化膜56の一部をエッチングする。マスク57に形成される開孔の位置は、素子領域に分散して形成されるp型拡散領域及び終端領域を一巡するガードリングの位置に対応している。酸化膜56がパターニングされた後に、酸化膜56上のレジスト58は除去される。

【0043】

次に、図17に示されるように、イオン注入技術を利用して、エピタキシャル層30の表面部の一部にアルミニウム又はボロンのドーパントを導入し、p型拡散領域62(アノード領域ということもできる)及びガードリング60を形成する。このときの半導体基板20の温度は500℃以下に保たれており、イオン注入に伴うアモルファス化を抑制している。ドーパントが導入された後に、酸化膜56は除去される。このように、本実施例では、p型拡散領域62及びガードリング60を共通の工程で作製することを1つの特徴としている。

【0044】

次に、図18に示されるように、CVD(Chemical Vapor Deposition)技術を利用して、エピタキシャル層30の表面にキャップ層70を形成する。次に、エピタキシャル層30の表面にキャップ層70が存在した状態で、アニール処理を実施し、p型拡散領域62及びガードリング60を形成するために導入されたドーパントを活性化させる。

【0045】

次に、図19に示されるように、酸素プラズマエッチング技術を利用して、キャップ層70を除去する。さらに、熱酸化技術を利用して、プラズマエッチング処理で除去しきれないキャップ層70を完全に除去する。このとき、エピタキシャル層30の表面部の貫通転位40の存在部位で酸化が進行し、下に凸状の酸化膜が形成される。次に、この酸化膜をフッ酸溶液で除去し、エピタキシャル層30の表面を洗浄する。この洗浄工程を経ると、図19に示されるように、エピタキシャル層30の表面部には、貫通転位40の存在部分に応じてエッチピット42が形成される。

【0046】

次に、図20に示されるように、減圧水素雰囲気下で熱処理を実施し、エッチピット42の底部を平滑化させる。

【0047】

次に、図21に示されるように、素子領域に開孔を有する層間絶縁膜82を形成した後に、その開孔に対応してアノード電極85を形成する。アノード電極85は、ショットキー電極部84と配線電極部86を有する。ショットキー電極部84の材料には、モリブデン、ニッケル、チタン等を用いることができる。配線電極部86の材料には、アルミニウムを用いることができる。最後に、半導体基板20の裏面に図示しないカソード電極(材料としてアルミニウムを用いることができる)を形成すると、ショットキーダイオードが製造される。

【0048】

上記したように、本実施例では、エピタキシャル層30の表面部に形成されているエッチピット42の底部が、減圧水素雰囲気下の高温熱処理によって実質的に増大されている。このため、図2に示されるように、エッチピット42に起因するリーク電流が大幅に減少する。また、減圧水素雰囲気下の高温熱処理では、エピタキシャル層30の厚みが実質的に維持されるので、耐圧を所望のものとすることができる。したがって、本実施例の製造方法で作製されるジャンクションバリアショットキーダイオードは、耐圧を所望のものとしながら、リーク電流を大幅に改善することができる。

【0049】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0050】

20:半導体基板

30:エピタキシャル層(半導体層の一例)

32:第2エピタキシャル層

40:貫通転位

42,42a,42b,42c:エッチピット

60:ガードリング

62:p型拡散領域

70:キャップ層

84:ショットキー電極部

85:アノード電極

86:配線電極部

【特許請求の範囲】

【請求項1】

ダイオードの製造方法であって、

半導体基板上に第1導電型の半導体層を結晶成長させる結晶成長工程と、

前記結晶成長工程の後に、前記半導体層の表面部の一部にドーパントを導入し、第2導電型領域を形成するドーパント導入工程と、

前記ドーパント導入工程の後に、前記ドーパントを活性化させるアニール工程と、

前記アニール工程の後に、エッチング技術を利用して前記半導体層の表面を洗浄する洗浄工程と、

前記洗浄工程の後に、前記半導体層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程と、を備えている製造方法。

【請求項2】

前記ドーパント導入工程と前記アニール工程の間に、前記半導体層の表面にキャップ層を形成するキャップ層形成工程と、

前記アニール工程と前記洗浄工程の間に、前記キャップ層を除去するキャップ層除去工程と、をさらに備えている請求項1に記載の製造方法。

【請求項3】

前記キャップ層は、前記アニール工程において、前記半導体層の表面から前記半導体層を構成する原子が昇華するのを抑制する請求項2に記載の製造方法。

【請求項4】

前記底部平滑化工程は、水素を含む雰囲気下で熱処理を実施する請求項1〜3のいずれか一項に記載の製造方法。

【請求項5】

前記底部平滑化工程の後に、前記半導体層の表面にアノード電極を形成する工程をさらに備える請求項1〜4のいずれか一項に記載の製造方法。

【請求項6】

前記アノード電極が前記半導体層の表面にショットキー接触する請求項5に記載の製造方法。

【請求項7】

前記半導体層の材料が炭化珪素である請求項1〜6のいずれか一項に記載の製造方法。

【請求項8】

ダイオードの製造方法であって、

半導体層の表面に電極を形成するのに先立って、エッチング技術を利用して前記半導体層の表面を洗浄する洗浄工程と、

前記洗浄工程の後であり、且つ前記半導体層の表面に電極を形成するのに先立って、前記半導体層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程と、を備えている製造方法。

【請求項1】

ダイオードの製造方法であって、

半導体基板上に第1導電型の半導体層を結晶成長させる結晶成長工程と、

前記結晶成長工程の後に、前記半導体層の表面部の一部にドーパントを導入し、第2導電型領域を形成するドーパント導入工程と、

前記ドーパント導入工程の後に、前記ドーパントを活性化させるアニール工程と、

前記アニール工程の後に、エッチング技術を利用して前記半導体層の表面を洗浄する洗浄工程と、

前記洗浄工程の後に、前記半導体層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程と、を備えている製造方法。

【請求項2】

前記ドーパント導入工程と前記アニール工程の間に、前記半導体層の表面にキャップ層を形成するキャップ層形成工程と、

前記アニール工程と前記洗浄工程の間に、前記キャップ層を除去するキャップ層除去工程と、をさらに備えている請求項1に記載の製造方法。

【請求項3】

前記キャップ層は、前記アニール工程において、前記半導体層の表面から前記半導体層を構成する原子が昇華するのを抑制する請求項2に記載の製造方法。

【請求項4】

前記底部平滑化工程は、水素を含む雰囲気下で熱処理を実施する請求項1〜3のいずれか一項に記載の製造方法。

【請求項5】

前記底部平滑化工程の後に、前記半導体層の表面にアノード電極を形成する工程をさらに備える請求項1〜4のいずれか一項に記載の製造方法。

【請求項6】

前記アノード電極が前記半導体層の表面にショットキー接触する請求項5に記載の製造方法。

【請求項7】

前記半導体層の材料が炭化珪素である請求項1〜6のいずれか一項に記載の製造方法。

【請求項8】

ダイオードの製造方法であって、

半導体層の表面に電極を形成するのに先立って、エッチング技術を利用して前記半導体層の表面を洗浄する洗浄工程と、

前記洗浄工程の後であり、且つ前記半導体層の表面に電極を形成するのに先立って、前記半導体層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程と、を備えている製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−199382(P2012−199382A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−62399(P2011−62399)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【出願人】(000004260)株式会社デンソー (27,639)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【出願人】(000004260)株式会社デンソー (27,639)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]