Fターム[4M104FF35]の内容

Fターム[4M104FF35]に分類される特許

1 - 20 / 314

半導体装置

半導体装置の製造方法

炭化珪素半導体装置の製造方法

炭化珪素半導体装置及びその製造方法

ジャンクションバリアショットキーダイオード

【課題】 リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供する。

【解決手段】 SiCジャンクションバリアショットキーダイオードにおいて、ショットキー接合界面にかかる電界強度を0.1MV/cm以下になるようにトレンチの深さと間隔を設定することで実現する。その結果として、リーク電流が低減し、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供できる。

(もっと読む)

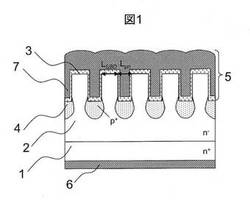

半導体装置

【課題】 SiCを含む基板を用いた接合障壁ショットキーダイオードの逆バイアス時の耐圧の低下を抑制することで、半導体装置の信頼性を向上させる。

【解決手段】 0.1cm2以上のアクティブ面積を有するJBSダイオードにおいて、アクティブ領域内の接合障壁領域であるp型半導体領域3の割合を相対的に大きくすることで、ドリフト層2とショットキー電極4とが接するショットキー界面の面積を十分に小さくし、ドリフト層2内に存在する欠陥に起因する耐圧の低下を防ぐ。

(もっと読む)

窒化物半導体装置

【課題】電極のコンタクト抵抗や逆方向リーク電流を低減できる窒化物半導体装置を提供する。

【解決手段】窒化物半導体層103と、窒化物半導体層103よりもバンドギャップが大きい窒化物半導体層104との接合体が少なくとも1つ基板101上に積層されている。窒化物半導体層104の上面から窒化物半導体層103における窒化物半導体層104との界面よりも下側までの範囲に位置する部分の前記接合体の両側端にテーパ部108及び109が形成されている。テーパ部108の側面上には窒化物半導体層103とショットキー接触するようにアノード電極106が形成されており、テーパ部109の側面上には窒化物半導体層103とオーミック接触するようにカソード電極107が形成されている。各テーパ部108及び109の側面が基板101の主面に対してなす角度は、20度以上で且つ75度以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体装置の製造方法は、(a)オフ角を有するSiC基板1上に、ドリフト層2と、酸化膜31と、レジスト32とをこの順に形成する工程と、(b)酸化膜31に第1開口部31aを形成するともに、レジスト32に第2開口部32bを形成する工程と、(c)不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入することにより、p型領域13,23をドリフト層2の上部に形成する工程とを備える。

(もっと読む)

ショットキーバリアダイオードの製造方法

【課題】リーク電流を抑制することが可能なショットキーバリアダイオードの製造方法を提供することである。

【解決手段】主面20Sを有する炭化珪素基板20が準備される。第1の温度で炭化珪素基板20の主面20Sを熱酸化することで、主面20Sの上に酸化膜30が形成される。酸化膜30が形成された後に、第1の温度よりも高い第2の温度で炭化珪素基板20が熱処理される。酸化膜30に主面20Sの一部を露出する開口部OPが形成される。開口部OPにより露出された主面20Sの上にショットキー電極40が形成される。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

ショットキーバリアダイオード

【課題】逆方向耐圧を大きくしても順方向電圧の増大、オーミック電極層とのコンタクト抵抗の増大を抑制することが可能なショットキーバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード1は、n型の導電性を有するGa2O3系化合物半導体からなるn型半導体層3と、n型半導体層3に対しショットキー接触するショットキー電極層2とを備え、n型半導体層3には、ショットキー電極層2にショットキー接触する電子キャリア濃度が比較的低いn−半導体層31と、n−半導体層31よりも高い電子キャリア濃度を有するn+半導体層32とが形成されている。

(もっと読む)

トレンチ型ショットキー接合型半導体装置及びその製造方法

【課題】 耐圧を低下させることなく、トレンチ開口幅を小さくすることができるショットキー接合型半導体装置を提供する。

【解決手段】 トレンチの断面形状を、トレンチの底面部の中央が高く、周辺が低いサブトレンチ形状とし、p型不純物をドリフト層表面に対して垂直に導入することで、サブトレンチが設けられたトレンチの内壁部に接するように形成されたp+SiC領域が、トレンチの底面の中央での接合位置よりも、トレンチの底面の周辺での接合位置が深くなるように形成する。

(もっと読む)

半導体装置

【課題】SiCを含む基板を用いたショットキーダイオードのショットキー界面のドリフト層に結晶欠陥が生じている場合に、逆方向漏れ電流の発生を防ぐことで、半導体装置の信頼性を向上させる。

【解決手段】半導体基板上のドリフト層2とショットキー電極4とのショットキー接合部を含むショットキーダイオードにおいて、ドリフト層2の上面に達する結晶欠陥12の上面に、ショットキー電極4を構成する金属に応じて規定される濃度および深さで、アクセプタ不純物を導入してp型半導体領域3を形成し、逆方向漏れ電流の増大を防ぐ。

(もっと読む)

半導体装置

【課題】高耐圧を確保できながら、逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】その表面12にショットキーメタル22が形成されたエピタキシャル層6を備えるショットキーバリアダイオード1において、エピタキシャル層6の表面12に沿う方向に互いに間隔を空けて配列され、それぞれが表面12から裏面11へ向かってエピタキシャル層6の厚さ方向に延びるp型ピラー層17を形成することにより、エピタキシャル層6にスーパージャンクション構造を形成する。また、エピタキシャル層6の表面12の近傍に、p型ピラー層17よりも不純物濃度の高い電界緩和層19を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

炭化珪素半導体装置

【課題】ボンディング耐性を向上させた炭化珪素半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、炭化珪素基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に平面視してリング状に形成された低濃度p型JTE領域3と、n型炭化珪素層2の表面近傍の低濃度p型JTE3の内側に該低濃度p型JTE領域3に接触して平面視してリング状に形成された高濃度p型領域4と、高濃度p型領域4上の一部に形成されたp型オーミック電極5と、p型オーミック電極5を覆うと共に高濃度p型領域4上及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】ショットキー電極形成前に酸洗浄を行ってもp型オーミック電極がその酸に曝されることなく、p型オーミック電極とショットキー電極との電気的接続が良好な炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成された複数のp型不純物領域3と、p型不純物領域3上の一部に形成されたp型オーミック電極4と、p型不純物領域3上の一部に、p型オーミック電極4を覆うように形成された耐酸性のバリアメタル層5と、バリアメタル層5、p型不純物領域3、及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板1のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、電界集中を緩和することで十分なサージ電流耐性を有した半導体装置およびその製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、炭化珪素からなる第1導電型の半導体層としてのn型半導体層1と、n型半導体層1表層において、ショットキーダイオードの素子領域を平面視上囲んで形成された、第2導電型の第1不純物層としてのp++型半導体層5aと、n型半導体層1表層において、素子領域を、少なくともp++型半導体層5aの平面視上外側から囲んで形成された、第2導電型の第2不純物層としてのp++型半導体層5bと、p++型半導体層5a表層まで延設して素子領域上に形成されたアノード電極3とを備え、p++型半導体層5aの不純物濃度が1×1020cm-3以上である。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

半導体装置

【課題】絶縁ゲート型バイポーラトランジスタとダイオードとが一体化された半導体装置において、スイッチング速度を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、ドリフト層11、ベース層17、複数の第1のトレンチ12、複数のゲート電極14、複数のエミッタ層19、複数の第2のトレンチ13、エミッタ電極15、バッファ層21、複数のコレクタ層22、およびコレクタ電極23、を具備する。複数の第1のトレンチ12は、ベース層17の上面において互いに平行かつ離間するように配置され、ベース層17を貫通するように形成される。複数の第2のトレンチ13のぞれぞれは、第1のトレンチ12の間に配置され、ベース層17を貫通しないように形成される。エミッタ電極15は、複数の第2のトレンチ13の内部を含むベース層17の表面上に形成される。

(もっと読む)

1 - 20 / 314

[ Back to top ]