Fターム[4M104GG06]の内容

Fターム[4M104GG06]に分類される特許

161 - 180 / 275

高電圧炭化ケイ素半導体デバイスのための環境的に堅固なパッシベーション構造

炭化ケイ素における高電界半導体デバイスのための改良された終端構造を開示する。該終端構造は、高電界動作のための炭化ケイ素ベースのデバイスと、該デバイスにおける活性領域と、該活性領域のためのエッジ終端パッシベーションとを含み、該エッジ終端パッシベーションは、表面状態を満足させ、界面密度を低下させるための該デバイスの炭化ケイ素部分の少なくとも一部分上の酸化物層と、水素の取り込みを回避するため、および寄生容量を減少させ、捕捉を最小化するための該酸化物層上の窒化ケイ素の非化学量論的層と、該非化学量論的層および該酸化物層を封入するための該非化学量論的層上の窒化ケイ素の化学量論的層と、を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、コレクタ領域が広く形成されるため、デバイスサイズを縮小し難いという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板2上にN型のエピタキシャル層4が積層されている。エピタキシャル層4には、ベース引き出し領域としてのN型の拡散層5、エミッタ領域としてのP型の拡散層6、7、コレクタ領域としてのP型の拡散層8、9が形成されている。エミッタ領域は、その表面近傍よりも深部に拡散幅の広い領域を有し、横型PNPトランジスタ1は、エピタキシャル層4深部に最小のベース幅が形成されている。この構造により、コレクタ領域を狭めた場合でも所望のhfe値を実現することができる。そして、デバイスサイズを縮小することができる。

(もっと読む)

半導体装置の製造方法

【課題】エミッタ層の寸法幅を微細化した高性能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、素子分離膜3に囲まれた活性領域A1を形成する。素子分離膜3の上には活性領域A1を含む側の所定の領域に開口部A2を有するシリコン酸化膜からなる保護膜4を設ける。この活性領域A1上にSiGe合金層6aを形成し、SiGe合金層6a上にシリコン膜7およびn型拡散層(エミッタ層)13を形成する。このn型拡散層13は断面凸状のシリコン膜7の一部にn型不純物を拡散させて形成する。またn型拡散層13の上に多結晶シリコン膜8aおよびシリサイド膜15aを形成する。さらにn型拡散層13、多結晶シリコン膜8a、及びシリサイド膜15aは、絶縁膜からなる側壁膜11で囲う。さらにSiGe合金層6aのうち内部ベース層として働く領域の外側に、外部ベース層としてp+拡散層12aおよびシリサイド膜15bを形成する。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】ベース抵抗が小さく、最大発振周波数などの高周波特性が優れ、低雑音なバイポーラトランジスタおよびその製造方法を提供する。

【解決手段】Siコレクタ層3a上に、SiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5が形成され、Siキャップ層5上にエミッタ引き出し電極7が形成され、エミッタ引き出し電極7およびそのサイドウォール直下を除いたSiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5にボロン注入でベース引き出し電極11が形成され、リンをSiキャップ層5中に拡散してエミッタ拡散層5aが形成され、ボロンをSiコレクタ層3a中に拡散して外部ベース拡散層1cが形成され、エミッタ拡散層5aの直下の真性ベース領域Bint に対して、ベース引き出し電極11と外部ベース拡散層1cで構成される外部ベース注入領域Bexを自己整合的に形成し、ベースリンク領域を削除し、ベース抵抗を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】エミッタからベース電極間の抵抗が低減され、高速動作が可能であり、高性能のバイポーラトランジスタを有する半導体装置を提供する。

【解決手段】半導体基体上に形成された絶縁膜の開口を含むように、シリコン層9A,9C、シリコンとゲルマニウム及び/又はカーボンとを有する層9B、により成るシリコン混晶層9によって形成されたエピタキシャルベース領域を有するバイポーラトランジスタが形成されて成り、シリコン混晶層9の最上層9Cがシリコン層であり、シリコン混晶層9から成るベース領域のうち、単結晶シリコン混晶層上及び多結晶シリコン混晶層上に、多結晶シリコン膜10を介してコバルトシリサイド11が形成されて成る半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、分離領域を構成するP型の埋込拡散層の横方向拡散幅が広がり、デバイスサイズを縮小し難いという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板6上に2層のエピタキシャル層7、8が形成されている。エピタキシャル層7、8には、分離領域3、4、5を構成するP型の埋込拡散層43、44、45及びP型の拡散層46、47、48が形成されている。このとき、P型の埋込拡散層43、44、45は1層目のエピタキシャル層7表面から拡散して形成されている。この構造により、P型の埋込拡散層43、44、45の横方向拡散幅W1、W2、W3が狭まり、NPNトランジスタ1のデバイスサイズを縮小することができる。

(もっと読む)

p型ひずみInGaNベース層を有するGaNヘテロ接合バイポーラトランジスタとその製造方法

【課題】オーミックコンタクトを有効に形成し、デバイスの操作特性を向上させる、p型ひずみInGaNベース層を有するGaNへテロ接合バイポーラトランジスタおよびその製造方法を提供する。

【解決手段】p型ひずみInGaNベース層を有する窒化ガリウムへテロ接合バイポーラトランジスタが提供され、窒化ガリウムへテロ接合バイポーラトランジスタが、基板、基板上に設置される高濃度ドープしたコレクタ接触層、前記コレクタ接触層上に設置される低濃度ドープしたコレクタ層、前記コレクタ層上のp型ベース層、前記p型ベース層上に設置された高濃度ドープしたp型ひずみInGaNベース層、前記p型ひずみInGaNベース層上に設置されるエミッタ層、前記エミッタ層上に設置される高濃度ドープしたエミッタ接触層および前記エミッタ接触層上、前記p型ひずみInGaNベース層上、および前記コレクタ接触層上にそれぞれ設置される、エミッタ金属電極、ベース金属電極およびコレクタ金属電極を含む。

(もっと読む)

半導体装置の製造方法

【課題】 エミッタ層の寸法幅を微細化した高性能な半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上に、素子分離領域3に囲まれたエピタキシャル層2(活性領域2a)を形成する。この活性領域2a上にSiGe合金層4を形成し、SiGe合金層4上にシリコン膜5およびn型拡散層(エミッタ層)6を形成する。このn型拡散層6は断面凸状のシリコン膜5の一部にn型不純物を拡散させて形成する。またn型拡散層6の上に多結晶シリコン膜7aおよびシリサイド膜11aを形成する。さらにn型拡散層6、多結晶シリコン膜7a、及びシリサイド膜11aは、絶縁膜からなる側壁膜9で囲う。さらにSiGe合金層4のうち内部ベース層として働く領域の外側に、外部ベース層としてp+拡散層10およびシリサイド膜11bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 層厚の厚い電極部および信頼性の高い保護膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体層21の積層方向Zの一表面上に電極部34を形成する。次に半導体層21および電極部34とを予め定める第1の温度T1のN2雰囲気下でシンタ処理し、半導体層21と電極部34とのオーミック性を向上させる。次にPSG膜35がアニーリングされかつ堆積される予め定める第2の温度T2において、酸化膜22の表面と電極部34の表面とにPSG膜35を堆積して形成する。次にPSG膜35の一部をエッチングすることによって、電極部34の一部が露出するように第2貫通孔37を形成する。

(もっと読む)

メタルベースナノワイヤトランジスタ

メタルベーストランジスタを示す。該トランジスタは、第一電極2及び第二電極6と、該第一及び第二電極間の電流流れを制御するベース電極3とを備える。第一電極2を半導体材料から作製する。ベース電極は、第一電極を形成する半導体材料の上に堆積した金属層である。本発明によれば、第二電極は、ベース電極3と電気接触した半導体ナノワイヤにより形成される。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法及びかかる方法によって得られる半導体デバイス

本発明は、基板(11)と、少なくとも1つの半導体素子(E)を備える半導体本体(12)とを有する半導体デバイス(10)の製造方法であって、この半導体本体(12)の表面上にメサ型半導体領域(1)が形成され、メサ型半導体領域(1)の頂部上での厚みがメサ型半導体領域(1)に隣接する領域(3)における厚みよりも小さな絶縁層(2)が、このメサ型半導体領域を覆って堆積され、次いで、メサ型半導体領域(1)の上側がなくなるように、メサ型半導体領域(1)の頂部の絶縁層(2)の一部を除去した後、メサ型半導体領域(1)に接触する導電膜(4)を、得られた構造を覆って堆積する方法に関する。本発明によれば、絶縁層(2)は、高密度プラズマ堆積プロセスを用いて堆積される。このような処理は、特に、例えばナノワイヤ形成のような小さなメサ型領域(1)を有するデバイスの製造方法に適している。好ましくは、絶縁層(2)の堆積前に、薄い更なる絶縁層(5)を、他の共形的堆積プロセスを用いて堆積する。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法および該方法で得られた半導体デバイス

本発明は、基板(11)と、少なくとも一つの半導体素子(E)を設けた半導体本体(12)とを有し、単結晶シリコン(1)領域を具え、該単結晶シリコン領域(1)の上に金属シリサイド領域(3)を設け、そして金属シリサイド領域(3)の上に低結晶性シリコン領域(4)を設け、その後、低結晶性シリコン領域(4)を加熱することにより高結晶性を有するエピタキシャルシリコン領域(2)に変化させ、その処理の間に金属シリサイド領域(3)を低結晶性シリコン領域(4)の下部からエピタキシャルシリコン領域(2)の上へと移動させることにより、単結晶シリコン領域(1)の上にエピタキシャルシリコン領域(2)を形成する、半導体デバイス(10)の製造方法に関する。上記本発明によれば、金属シリサイド領域(3)より高い位置に、孔(6)を設けた絶縁層(5)を形成し、低結晶性シリコン領域(4)を孔(6)中および絶縁層(5)の上に析出させ、絶縁層(5)上の低結晶性シリコン領域(4)の一部(4A、4B)を平坦化処理により取り除き、その後にエピタキシャルシリコン領域(2)を形成する。この方法では、自己整合方式で金属シリサイドコンタクト(領域)が設けられており、そしてトランジスタのような半導体素子(E)の一部を形成できる、エピタキシャルシリコン領域(2)、好ましくはナノワイヤ(2)が簡単に得られる。  (もっと読む)

(もっと読む)

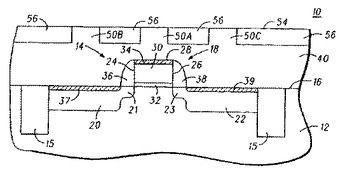

犠牲マスキング構造を用いた半導体装置の製造方法

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールによるバイポーラトランジスタのエミッタ領域の貫通を防ぐとともに、MOSトランジスタのソース領域及びドレイン領域のコンタクトを良好にする。

【解決手段】同一のシリコン基板12に、MOSトランジスタ及びバイポーラトランジスタが形成されている下地10上に、CVD法によりシリコン酸化膜40を形成し、シリコン酸化膜上に反射防止膜45を形成し、その上に、エッチングマスク51を形成する。反射防止膜及びシリコン酸化膜47の積層膜に対して、プラズマエッチングを行うことにより、積層膜を貫通するコンタクトホール60aおよび60bをそれぞれ設ける。プラズマエッチングとして、反射防止膜を主としてエッチングする第1プラズマエッチングと、反射防止膜及びシリコン酸化膜を主としてエッチングする第2プラズマエッチングと、シリコン酸化膜を主としてエッチングする第3プラズマエッチングとをこの順に行う。

(もっと読む)

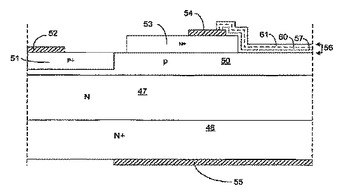

ダイオード内蔵パワースイッチングデバイスとその製造方法

【課題】フライホイールダイオードを内蔵したパワースイッチングデバイスにおける、高速スイッチング性向上と、安価に製造できるデバイス構造と製造方法。

【解決手段】下面にコレクタ電極を有するN+半導体層上面に形成したN-半導体層上面から厚み方向にP型領域を櫛状に形成し、該P型領域上面をエミッタ電極に接続したショトキー金属層に接合してなる、MPS構造体のダイオードをコレクタ・エミッタ間に造り込み、MPS構造のダイオードの逆回復時間が従来のPINダイオードの6分の1に短くすることが出来た。

(もっと読む)

半導体素子及びその製造方法

【課題】 高い信頼性を有し且つn型AlXGaYIn1−X−YN(0≦X≦1、0≦Y≦1、X+Y≦1)半導体層、又はノンドープのAlXGaYIn1−X−YN(0≦X≦1、0≦Y≦1、X+Y≦1)半導体層と良好な低抵抗接触が得られる電極構造を備えた半導体素子及びその製造方法を提供する。

【解決手段】 n型AlXGaYIn1−X−YN(0≦X≦1、0≦Y≦1、X+Y≦1)半導体層、又はノンドープのAlXGaYIn1−X−YN(0≦X≦1、0≦Y≦1、X+Y≦1)半導体層上に、前記半導体層と低抵抗接触する電極を備えた半導体素子であって、前記電極を、少なくともGeを含むCrからなる構成としている。

(もっと読む)

半導体装置及びその製造方法

【課題】 高濃度のドーピングを行うことが可能で、電極と良好なオーミック接触を取ることを可能とする。

【解決手段】 III−V族化合物半導体を用いた半導体装置において、エミッタ電極と該エミッタ電極に接触する金属電極接触層とを有し、前記金属電極接触層が量子構造で構成されている。

(もっと読む)

ダイヤモンドパワー半導体デバイス及びその製造方法

【課題】逆方向リーク電流を抑制したダイヤモンドパワー半導体デバイスと、その製造方法を提供する。

【解決手段】電極とダイヤモンド薄膜を設けた基板からなり、デバイス領域が非エピタキシャル膜及び成長丘状ヒロックの異常成長領域のないダイヤモンド薄膜上に形成されるダイヤモンドパワー半導体デバイス。エピタキシャルダイヤモンド薄膜の異常成長粒子や成長丘などの結晶欠陥を検査し、これを避けて電極用パターンを形成する。

(もっと読む)

バイポーラ接合トランジスタ及びその製造方法

炭化ケイ素(SiC)基板を含むバイポーラ接合トランジスタ(BJT)が提供される。SiC基板上に、エピタキシャルSiCベース領域が設けられる。エピタキシャルSiCベース領域は、第1の導電型を有する。SiC基板上に、エピタキシャルSiCエミッタ領域も設けられる。エピタキシャルSiCエミッタ領域は、第1の導電型とは異なる第2の導電型を有する。エピタキシャルSiCエミッタ領域は、第1及び第2の部分を有する。第1の部分は、SiC基板上に設けられ、第2の部分は、第1の部分上に設けられる。第2の部分は、第1の部分よりも高いキャリア濃度を有する。BJTの製造方法も、本明細書において提供される。  (もっと読む)

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】 ドライエッチングによりメサ形成を行ったHBTにおいて、エアブリッジなどの特別な配線形成工程を必要とせず、良好な特性を示す構造のヘテロ接合バイポーラトランジスタを提供する。

【解決手段】 ヘテロ接合バイポーラトランジスタ100は、少なくとも、ベース層104に形成されているベース電極112と接続されている引き出し配線121の下層に形成されているO3−TEOS膜132と、O3−TEOS膜132の下層に形成されている膜厚200nm以上のSiO2膜131とを備える。

(もっと読む)

161 - 180 / 275

[ Back to top ]