Fターム[4M104GG06]の内容

Fターム[4M104GG06]に分類される特許

141 - 160 / 275

個別電子コンポーネントのマトリクスを形成する方法および形成されるマトリクス

本発明は、基板(100)上にアクティブ層(101)を形成する段階および少なくとも基板(100)が出現するまで、トレンチ(102)をアクティブ層(101)内に形成することでコンポーネントを個別化する段階を含む、電子コンポーネント(111)のマトリクスを製造する方法に関する。この方法は、アクティブ層(101)上に機能材料の層(102)を蒸着する段階と、前記トレンチ(102)を充填し、電子コンポーネント(111)の上側面に薄膜(115)を形成するように、材料の層(103)上に感光性樹脂(104)を蒸着する段階と、トレンチの樹脂の部分の露光を少なくしつつ樹脂(104)を放射線に少なくとも部分的に曝露する段階と、適切に露光された部分を除去するように樹脂(104)を現像する段階と、現像段階の後、外面に現われる機能材料の層(103)の部分を除去する段階と、樹脂の残り部分を除去する段階とを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】従来の製造方法においては、オーバーエッチングによりコンタクト底部の表面荒れが引き起こされ、それにより半導体装置の特性ばらつきが増大してしまう。

【解決手段】P型シリコン基板1に形成されたトレンチの底部に設けられたコレクタ領域4を有するバイポーラトランジスタを形成する。P型シリコン基板1上に層間絶縁膜23を形成する。トレンチの上部の層間絶縁膜23を途中までエッチングすることにより、コレクタコンタクト用開口の一部30を形成する。トレンチの上部の層間絶縁膜23を上記底部に達するまでエッチングすることにより、コレクタコンタクト用開口の残りの部分32を形成する。コレクタコンタクト用開口の残りの部分32の形成は、エミッタコンタクト用開口25およびベースコンタクト用開口27の形成と同時に実行される。

(もっと読む)

窒化物半導体バイポーラトランジスタ及び窒化物半導体バイポーラトランジスタの製造方法

【課題】ベース抵抗が小さく優れた高周波特性を有する窒化物半導体バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】窒化物半導体バイポーラトランジスタにおいて、エミッタ層に接する形で形成されたコンタクト層がn型InAlGaN4元混晶により形成され、前記エミッタ層と前記コンタクト層はその上に形成されたエミッタとの障壁高さが小さくInAlGaN4元混晶上ではオーミック電極コンタクト抵抗を小さくできる例えばWSiエミッタ電極が庇となるように選択的に除去されており、このエミッタ電極をマスクとしてベース電極がセルフアライン工程にて形成される。このような構成にすることにより、エミッタ段差とベース電極端との間の距離を、十分に小さくし、ベース抵抗を低減できる。この結果、良好な高周波特性を有するバイポーラトランジスタを実現することが可能となる。

(もっと読む)

半導体装置

【課題】1つの整流又はショットキーバリアコンタクトを含む電界効果トランジスタのような金属半導体化合物/半導体の接合領域を含む半導体装置の提供。

【解決手段】所定のドーピングレベルの半導体基板2に形成された第1および第2電極6を有する半導体装置1であって、第1および第2電極6は半導体領域5により互いに分離され、第3電極3は半導体領域5の導電性を制御し、第1および第2電極6の少なくとも1つは半導体領域5と整流コンタクトを形成し、整流コンタクトはポテンシャルバリアを有する半導体装置を提供する。本発明によれば、少なくとも第1および第2電極の間の方向に対して、半導体領域5は、半導体基板2のドーピングレベルより高いドーピングレベルを有するように均一にドープされ、動作中に、少なくとも1つの整流コンタクトのポテンシャルバリアを低くする鏡像力メカニズムを誘起する。更に、そのような半導体装置の製造方法。

(もっと読む)

略自然降伏デバイス

【課題】 バイアス電圧が印加されるときに半導体デバイス上に自然降伏状態を作り出すような「略自然降伏状態」を提供する。

【解決手段】 本発明の半導体デバイスは第1半導体領域を含み、第1半導体領域は、強制または非強制略自然降伏領域であり、この領域は、非自然降伏(例えば、ツェナー降伏及び雪崩降伏)の降伏電圧以下の大きさを有する所定電圧がデバイスの両端に印加されるときに完全に空乏化される。

(もっと読む)

半導体装置およびその製造方法

【課題】省スペース性および高周波特性を両立する半導体装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、半導体基板1と、半導体基板1上に形成されたサブコレクタ層2と、サブコレクタ層2上に形成されたコレクタ層3と、コレクタ層3上に形成されたベース層4と、ベース層4上に形成されたエミッタ層5と、コレクタ層3と接続されるコレクタ電極8aと、ベース層4と接続されるベース電極7と、エミッタ層5と接続されるエミッタ電極6と、サブコレクタ層2をスパイラル状に区画する絶縁領域16と、スパイラル状に区画されたサブコレクタ層2の一端に接続される第1のインダクタ電極8bと、スパイラル状に区画されたサブコレクタ層2の他端に接続される第2のインダクタ電極8cとを備える。

(もっと読む)

化合物半導体バイポーラトランジスタ

【課題】エッチピットを低減可能な構造を有するバイポーラトランジスタ及びその製造方法を提供する。

【解決手段】HBT1は、半絶縁性のInP基板2と、同基板2上に形成されたバッファ層30と、バッファ層30上に形成されたサブコレクタ層40と、コレクタ層80と、ベース層90と、エミッタ層100と、エミッタ層100上に形成されたエミッタコンタクト層110とを有する。エミッタ層100のエッジは、エミッタコンタクト層110のエッジから離れて設けられている。また、エミッタ層110の表面は、平坦化されている。HBT1は、サブコレクタ層40上にコレクタ電極17と、エミッタ層100上にベース電極16と、エミッタコンタクト層110上にエミッタ電極15とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧性および耐湿性が向上された半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、トランジスタ等が形成される活性領域19を囲むように、分離領域13A、13Bを設けている。この分離領域13A等は、半導体基板11の上面から下面まで連続して延在していおり、内部にはシリコン酸化膜等から成る絶縁物層14Aが形成されている。従って、活性領域19が形成される半導体基板11の側面の全てを絶縁物により被覆することができるので、半導体装置の耐圧性および耐湿性を向上させることができる。

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

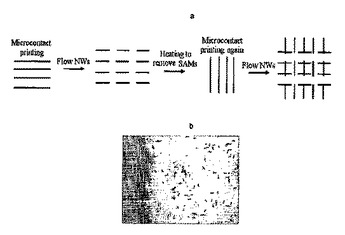

ナノスケール電子素子製造のための表面上へのナノワイヤのパターン形成

本発明は、基板の規定された領域に、基板表面と結合でき且つナノワイヤと結合できる少なくとも1つの化合物(C1)を接触させて、基板表面上に結合サイトのパターンを提供し、および/または基板の規定された領域に、基板表面と結合し且つナノワイヤの結合を阻止する少なくとも1つの化合物(C2)を接触させて、基板表面上に非結合サイトのパターンを提供し、且つ、基板表面を液体媒体中のナノワイヤの懸濁液と接触させて適用したナノワイヤの少なくとも一部分を、(C1)で被覆されている、および/または(C2)で被覆されていない基板表面の少なくとも一部分と結合させる工程を含む、基板表面へのナノワイヤの堆積方法に関する。  (もっと読む)

(もっと読む)

エミッタ−ベーススペーサ領域中に低K材料を有するバイポーラトランジスタの作製方法

【課題】本発明はエミッタ−ベーススペーサ領域中に低K材料を有するバイポーラトランジスタの作製方法を提供する。

【解決手段】本発明は半導体ウエハ基板上に配置されたバイポーラトランジスタを供する。バイポーラトランジスタは半導体ウエハ基板中に配置されたコレクタ、コレクタ中に配置されたベース、ベース上に配置され、ベースの少くとも一部と接触するエミッタを含んでよく、エミッタはその中に低K層を有する。低K層はたとえば、エミッタの一方の側に近接して配置するか、エミッタの相対する側に近接して配置してよい。しかし、すべての実施例において、低K層はバイポーラトランジスタの適切な機能を妨げず、従来のバイポーラトランジスタに典型的に付随したエミッタ−ベース容量を、本質的に減す。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】庇部を有する電極の庇部下の空洞を絶縁膜で埋め込むことで、層間絶縁膜や配線の段切れ、配線の短絡等を防止することを可能とする。

【解決手段】基板10に形成された導電層(エミッタキャップ層15)に接続されるもので庇部20a有するコンタクト電極(エミッタ電極)20と、エミッタ電極20の庇部20a下の空洞28部分に埋め込まれた絶縁膜31と、エミッタ電極20および絶縁膜31側部を被覆する層間絶縁膜21と、層間絶縁膜21に形成された接続孔24を通じてエミッタ電極20に接続されるとともに、層間絶縁膜21上をエミッタ電極20上より電極周辺部に配設されている配線27とを備えたことを特徴とする。

(もっと読む)

半導体基板を金属基板に結合する方法

半導体基板を金属基板に結合する方法を開示する。或る実施の形態では、この方法は第1の表面を含む半導体素子を半導体基板内に形成することを含む。この方法は更に、金属基板を得ることを含む。金属基板を半導体素子の第1の表面に結合し、金属基板の少なくとも一部は半導体素子の電気端子を形成する。  (もっと読む)

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】HBTの動作の信頼性向上と動作の高速性向上とを同時に実現する。

【解決手段】 半絶縁性基板11上にコレクタコンタクト層12、コレクタ層13、ベース層14、エミッタ層15,16、エミッタコンタクト層17、エミッタ電極18,19が形成され、ベース層上、コレクタコンタクト層上にベース電極21、コレクタ電極25を取付けたHBTにおいて、エミッタ層を、ベース層側の第1のエミッタ層15とエミッタコンタクト層側の第2のエミッタ層16とで形成し、第1のエミッタ層の延設部23に空乏化されたリッジを形成する。さらに、第2のエミッタ層、エミッタコンタクト層及びエミッタ電極は、エミッタ電極に対するアンダーカット31を有したエミッタメサ22を形成し、ベース電極をエミッタメサに対してセルフアライン形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】従来は、1層のAlの金属電極層を素子領域にコンタクトさせ、当該金属電極層上にAuのボンディングワイヤを固着していた。この場合時間経過に伴いAu/Al共晶層が形成され、素子領域に悪影響を及ぼす問題があった。

【解決手段】金属電極層を、第1電極層、Tiを含むバリアメタル層、第2電極層の3層の構造にする。バリアメタル層により、第1電極層、第2電極層の膜厚を従来と同等としてもAu/Al共晶層が素子領域に到達することを防止できる。また3層の金属電極層は同一チャンバー内で連続して形成し、1つのマスクで一度のエッチング工程でパターンニングが可能である。抵抗の増大、素子領域への不均一な電圧印加、製造工程の増加や生産効率の悪化等の弊害を招くことなく、Au/Al共晶層による不良を回避できる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、縦型PNPトランジスタと縦型NPNトランジスタとを備えた半導体装置の製造方法に関し、縦型NPNトランジスタの特性の劣化を抑制することを課題とする。

【解決手段】第1のN型埋め込み拡散層21と、P型拡散層23,25と、第1のN型エピタキシャル成長層22とを有する縦型PNPトランジスタ15と、第2のN型埋め込み拡散層40と、第2のN型エピタキシャル成長層41とを有する縦型NPNトランジスタ16とを備えた半導体装置10の製造方法であって、第1及び第2のN型埋め込み拡散層21,40を形成後に、第1及び第2のN型エピタキシャル成長層22,41を形成し、第1及び第2のN型エピタキシャル成長層22,41を形成後にP型拡散層23,25を形成した。

(もっと読む)

ミドル・オブ・ザ・ライン(MOL)用途のための無電解コバルト含有ライナ

【課題】 従来技術のMOLメタラジを用いてその欠点を回避する新しいMOLメタラジとその製造方法を提供すること。

【解決手段】 酸素ゲッター層と金属含有導電性材料との間に配置されたCo含有ライナを含む半導体構造が提供される。Co含有ライナ、酸素ゲッター層及び金属含有導電性材料は、Co含有ライナが従来のTiNライナと取って代わるMOLメタラジを形成する。「Co含有」とは、ライナが、元素状Coのみを含むか、又は元素状CoとP又はBの少なくとも1つを含むことを意味する。高アスペクト比のコンタクト開口部内により良好な段差被覆性の本発明のCo含有ライナを提供するために、Co含有ライナが、無電解蒸着プロセスによって形成される。

(もっと読む)

ヒューズ素子及びヒューズ素子を備えた半導体装置並びに半導体装置の製造方法

【課題】より低い電圧の印加によって溶断可能であって、しかも溶断に要する熱量を低減可能なヒューズ素子、及びヒューズ素子を備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】ヒューズ素子は、半導体基板上に少なくともシリコンと、このシリコンよりも融点が低い元素とで形成した導電層と、この導電層の上面に形成した金属シリサイド層とで形成する。シリコンよりも融点が低い元素はゲルマニウムとする。特に、半導体基板には、上面に金属シリサイド層を設けたシリコン−ゲルマニウム層からなるベース引き出し電極を備えたバイポーラトランジスタが形成されており、導電層はバイポーラトランジスタにおけるシリコン−ゲルマニウム層の形成にともなってヒューズ素子部分に形成されたシリコン−ゲルマニウム層で形成する。

(もっと読む)

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング(34)を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域(38)を有する。炭化ケイ素層上に窒化ケイ素層(56)が設けられ、窒化ケイ素層上に有機保護層(66)が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法も又、開示されている。  (もっと読む)

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】 低抵抗及び低インダクタンスの裏面貫通ビア及びその製造法

【解決手段】 裏面コンタクト構造体及びその構造体を製造する方法を提供する。この方法は、表面及び対向する裏面を有する基板(100)内に誘電体分離(250)を形成するステップと、基板(100)の表面上に第1誘電体層(105)を形成するステップと、誘電体分離(250)の周囲上及び内部に位置合せされ、誘電体分離(250)まで延びるトレンチ(265C)を第1誘電体層(105)内に形成するステップと、第1誘電体層(105)内に形成されたトレンチ(265C)を、誘電体分離(250)を貫通して基板(100)の厚さより小さな深さ(D1)まで基板(100)内部に延ばすステップと、トレンチ(265C)を充填し、且つトレンチ(265C)の上面を第1誘電体層(105)の上面と同一平面にして、導電性貫通ビア(270C)を形成するステップと、基板(100)の裏面から基板(100)を薄くして貫通ビア(270C)を露出させるステップとを含む。

(もっと読む)

141 - 160 / 275

[ Back to top ]