Fターム[4M104GG06]の内容

Fターム[4M104GG06]に分類される特許

261 - 275 / 275

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】 第1の主面と該第1の主面に背向する第2の主面とを有するn+型SiC基板11と、第2の主面上に形成されたエピタキシャル層13と、エピタキシャル層13上に形成されると共に、エピタキシャル層13とオーミック接触した電極14とを有することを特徴とする。

(もっと読む)

バイポーラトランジスタとその製造方法

【課題】 ベース電極がエアブリッジ構造を有するバイポーラトランジスタにおいて、構造の簡潔化、ベース電極に対する外部配線としてのベース配線のコンタクト位置の自由度を高めることができるようにする。

【解決手段】 ベース層13の少なくとも一部が上面に臨んで形成された半導体メサ部BMを有し、そのベース層13にコンタクトされたベース電極15が、半導体メサ部BMより外側の空間に浮上延長する浮上延長部15Fを有し、この延長浮上部15Fをベース電極13に対するベース配線42のコンタクト部15Cとする。このようにして、コンタクト部を固定部に設ける場合におけるこの固定部を形成するための構造、製造の煩雑さを回避でき、かつベース電極に対するベース配線のコンタクト部の選定の自由度をたかめ、レイアウト等の設計の自由度を高めるものである。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができる半導体素子および半導体素子の製造方法を提供する。

【解決手段】 n型SiC基板1上に、1b族と8族のFe列以外とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる第1の貴金属膜2を形成し、第1の貴金属膜2上に、4a族と5a族と6a族と7a族と8族のFe列とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる耐熱金属膜3を形成し、耐熱金属膜3上に、1b族と8族のFe列以外とのいずれかに属する元素のうち、いずれか1つ又は2つ以上からなる第2の貴金属膜4を形成し、その後、これらを960℃から1000℃までの範囲で加熱する。

(もっと読む)

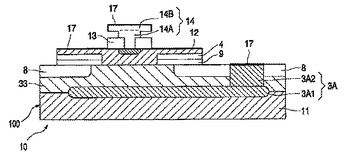

半導体装置及びその製造方法

【課題】 組立後に発生する内在応力及び使用条件下で発生する外因性応力を緩和し、とくにチップ表面に近い領域に形成された浅いジャンクションを有する製品に適した表面積層電極構造を備えた半導体装置を提供する。

【解決手段】 複数のリード2の下面は、樹脂封止体4の下面から露出しておりシリコン半導体基板10上には、半田を介してフレームを接続するために、半田接合用金属層8を含む積層電極構造7が形成されている。積層電極構造7は、半導体基板とショットキージャンクションを形成する第1の金属層11と、その上のジャンクションに対する応力を緩和するAlを主成分とする第2の金属層12と、その上のAlと金属間化合物を起し難いMo又はTiを主成分とする第3の金属層13と、その上の少なくともNi層を含む半田接合用金属層8とを備えている。第2の金属層がAlによる応力緩和作用を十分に発揮させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 小型化及び低コスト化できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】 N型半導体基板12下面に形成され、該N型半導体基板12よりも高抵抗なN型エピタキシャル層14下面の一部分にP型拡散層22,22を設け、該P型拡散層22,22及びその周辺のN型エピタキシャル層14下面に第1電極層20を有する半導体装置10において、前記N型エピタキシャル層14下面の前記第1電極層20が形成されていない部分の凹部の底に、N型半導体基板12に接続された第2電極層21を有する構成にする。

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

電気的な構成要素と該構成要素の電気的な接続導体とを有するシステム並びに該システムを製造する方法

本発明は、少なくとも1つの電気的な接触面(20)を有する少なくとも1つの電気的な構成要素(2)と、該構成要素(2)の前記接触面(20)を電気的に接触させるための少なくとも1つの電気的な接続導体(3)と、前記構成要素(2)の上に配置された少なくとも1つの絶縁層(4)とを有し、該絶縁層(4)が該絶縁層(4)の厚さ方向でこれを貫通する少なくとも1つの開口(42)を有し、該開口(42)が前記構成要素(2)の接触面(20)に向き合って配置されており、前記絶縁層(4)が前記開口(42)を制限する側面(43)を有し、前記電気的な接続導体(3)が前記側面(43)に配置された少なくとも1つの金属化層(30)を有しているシステムに関する。該システムは、前記金属化層(30)が前記接触面(20)に対し斜めに配向されていることを特徴としている。斜めに配向された金属化層によっては、前記絶縁層の上に配置された前記接続導体の区分と前記絶縁層と前記構成要素とが互いに機械的にかなり結合される。有利には金属化層は数μmの厚さを有している。機械的な減結合によって、前記接続導体と前記絶縁体と前記構成要素とは、熱的な膨張係数の異なる材料から成っていることができる。本発明は特に、出力半導体構成要素を大きな面積で電気的に接触させるために使用される。  (もっと読む)

(もっと読む)

窒化物半導体装置のオーム性電極構造

窒化物半導体を有する窒化物半導体装置のオーム性電極構造であって、窒化物半導体上に形成された第1の金属膜と、第1の金属膜上に形成された第2の金属膜とを有する。第1の金属膜は、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zrから成るグループの中から選ばれた少なくとも一つの材料で構成されている。第2の金属膜は、第1の金属膜102と異なる、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zr、Pt、Auから成るグループの中から選ばれた少なくとも一つの材料で構成されている。 (もっと読む)

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

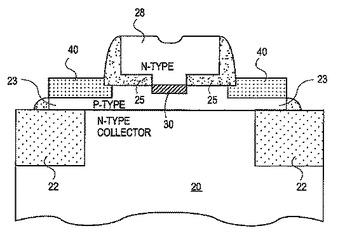

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

部分的シリサイド化シリコン層を有する集積回路

この集積回路(1)は、シリサイド化部(122)及び非シリサイド化部(123)を有する第1のシリコン層(120)を有する抵抗素子などの電気的装置(2)と、例えばキャパシタ、電界効果トランジスタ又は不揮発性メモリゲート堆積部などの他の電気的装置(3)とを有する。他の電気的装置(3)は、誘電層厚さ(D)を有する誘電層(130)を有する。電気的装置(2)の非シリサイド化部(123)は、誘電層厚さ(D)を有する他の誘電層(131)により被覆され、シリサイド化部(122)は、他の誘電層(131)により被覆されない。このような集積回路(1)は、リソグラフィ工程数の少ない本発明による方法によって形成可能となる。

(もっと読む)

(もっと読む)

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

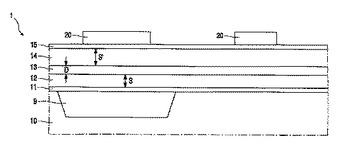

高いfTおよびfmaxを有するバイポーラ・トランジスタおよびこれを製造する方法

【課題】 ベース抵抗を低減したバイポーラ・トランジスタを提供する。

【解決手段】 高いfTおよびfmaxを有するバイポーラ・トランジスタ(100)は、エミッタ(104)、ベース(120)、およびコレクタ(116)を含む。エミッタは、下部(108)と、この下部を越えて延在する上部(112)とを有する。ベースは、真性ベース(140)および外部ベース(144)を含む。真性ベースは、エミッタの下部とコレクタとの間に位置する。外部ベースは、エミッタの下部からエミッタの上部を越えて延在し、エミッタの上部の下からエミッタの上部の下よりも外側まで延在する連続導体(148)を含む。連続導体は、ベース・コンタクト(図示せず)から固有ベースまでの低電気抵抗の経路を提供する。このトランジスタは、第2の導体(152)を含むことができ、これは、エミッタの上部の下に延在せず、これによって、外部ベースを介した電気抵抗を更に低減する。

(もっと読む)

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

261 - 275 / 275

[ Back to top ]