Fターム[4M104GG14]の内容

Fターム[4M104GG14]に分類される特許

201 - 220 / 3,371

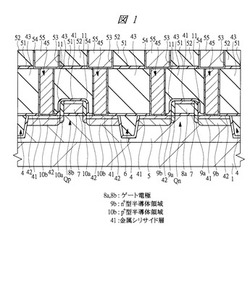

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

TFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法

【課題】成膜条件(成膜中の圧力、成膜に用いるガス種等)を変更しなくても、成膜された銅膜中の引張残留応力を低減できるTFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法を提供する。

【解決手段】本発明に係るTFT用銅スパッタリングターゲット材は、銅材からなり、銅と不可避的不純物とからなる無酸素銅、又は銅合金からなるスパッタ面を備え、かつ、(111)面と、(200)面と、(220)面と、(311)面との総和に対する、(111)面の占有割合が、15%以上であるTFT用銅スパッタリングターゲット材である。

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

半導体装置

【課題】スイッチング損失を低減した半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、ベース層と、ベース層上に設けられた第2導電形半導体層と、第2導電形半導体層の表面からベース層側に向けて延び、ベース層には達しない複数の第1のトレンチの内壁に設けられた第1の絶縁膜と、第1の絶縁膜を介して第1のトレンチ内に設けられると共に第2導電形半導体層の表面に接する第1の電極とを備えている。第2導電形半導体層は、第1のトレンチで挟まれた第1の第2導電形領域と、第1の第2導電形領域とベース層との間および第1のトレンチの底部とベース層との間に設けられ、第1の第2導電形領域よりも第2導電形不純物量が少ない第2の第2導電形領域とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】可能な限り従来の設備及び加工プロセスを継承してコストの上昇を抑制するも、Ta含有の導電材料を難除去性の残留付着物を発生せしめることなく所望に加工し、容易且つ確実に信頼性の高い半導体装置を実現する。

【解決手段】半導体基板上に、Ta含有層、TiN層、及び多結晶シリコン膜等のドライエッチング可能な層を順次積層し、TiN層をエッチングストッパーとして多結晶シリコン膜をドライエッチングして所定形状に残し、TiN層及びTa含有層をSPM、APM等を用いてウェットエッチングして多結晶シリコン膜下で所定形状に残す。

(もっと読む)

半導体装置の作製方法

【課題】高性能、高信頼性のトランジスタを有する半導体装置を作製する技術を提供する。

【解決手段】配線層を導電層から形成する際に酸化物半導体層を保護するための保護導電膜を酸化物半導体層と導電層との間に形成して、2段階のエッチングを行う。第1のエッチング工程には、保護導電膜は導電層よりエッチングされにくく、導電層と保護導電膜とのエッチング選択比が高い条件で行うエッチング方法を採用し、第2のエッチング工程には、保護導電膜は酸化物半導体層よりエッチングされやすく、保護導電膜と酸化物半導体層とのエッチング選択比が高い条件で行うエッチング方法を採用する。

(もっと読む)

半導体装置

【課題】逆方向耐圧を向上させることができる半導体装置を提供する。

【解決手段】一導電型の半導体層100と、絶縁体層130と、絶縁体層中に設けられた半導体層210と、半導体層210に設けられた能動素子20と、半導体層100の前記一主面201に設けられた他の導電型の半導体領域112と、半導体領域112内に設けられた他の導電型であって半導体領域112よりも高不純物濃度の半導体領域114と、絶縁体層130に設けられたスルーホール144内に半導体領域144に接続して設けられた導電体154と、絶縁体層130上または中に設けられた導電体214であって、導電体154の周囲に設けられ、外側端部が半導体領域114よりも外側にある導電体214と、導電体154と導電体214とを接続して設けられた導電体192と、半導体層100に接続して設けられた導電体152,120と、を備える。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

EL表示装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものと

して、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を

有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線

上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層

と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前

記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを

特徴としている。

(もっと読む)

201 - 220 / 3,371

[ Back to top ]