Fターム[4M104GG14]の内容

Fターム[4M104GG14]に分類される特許

141 - 160 / 3,371

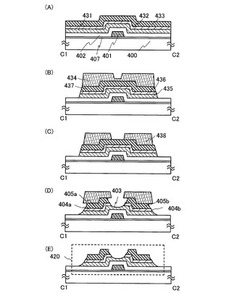

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置

【課題】十分な電流を流すことのできるトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】一実施形態の半導体装置は、半導体基板と、半導体基板上に設けられ、上面および側面が鞍形状を形成し、上面における鞍点を含む領域における第1方向の両端に凸部をそれぞれ有する半導体領域と、凸部の上面を除いた半導体領域の上面と、第1方向に沿った側面と、第1方向に直交する第2方向に沿った、上面における鞍点を含む領域側の前記凸部の側面との上に設けられたゲート絶縁膜と、ゲート絶縁膜の上に設けられたゲート電極であって、上面における鞍点を含む領域の直上に設けられた本体部と、本体部に接続され半導体領域の第1方向に沿った側面を覆う脚部と、を有し、脚部の第1方向における長さが上面における鞍点を含む領域の直上に設けられた本体部の第1方向における長さよりも長くなるように構成されたゲート電極と、ゲート電極の両側の半導体基板に設けられた第1および第2不純物領域と、を備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体装置の製造方法

【課題】高歩留まりの薄型半導体装置の製造方法を提供する。

【解決手段】まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。

(もっと読む)

半導体装置

【課題】縦型のフィールドプレート構造を有する絶縁ゲート電界効果トランジスタにおいて、寄生バイポーラトランジスタによるアバランシェ電流の集中を緩和する。

【解決手段】本実施形態の半導体装置は、素子部とダイオード部を有する。素子部は、ドレイン層と、ドレイン層の上に設けられたドリフト層と、ドリフト層の上に設けられたベース領域と、ベース領域の表面に選択的に設けられた第1導電形のソース領域と、ソース領域の表面からベース領域を貫通して、ドリフト層に接する複数の第1トレンチ内に設けられた第1ゲート電極と、この下に設けられたフィールドプレート電極と、を有する。ダイオード部は、ドレイン層とドリフト層とにおいて素子部と共有し、ベース領域の表面を貫通して、ドリフト層に接する複数の第2トレンチを有する。このダイオード部の第2トレンチ間の距離が素子部の第1トレンチ間の距離と比較して大きくなるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

141 - 160 / 3,371

[ Back to top ]