Fターム[4M104HH20]の内容

Fターム[4M104HH20]に分類される特許

2,001 - 2,020 / 2,580

半導体装置及びその製造方法

【課題】ゲート配線の幅が狭いフルシリサイド化ゲートプロセスを用いた半導体装置において、ゲート配線の設計ルールを変更することなく、ゲート配線とコンタクトとの接触面積を確保することが容易で且つゲート配線の配線抵抗が小さい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10に形成された素子分離領域12及び素子分離領域12に囲まれた活性領域11と、素子分離領域12及び活性領域11の上に形成され、フルシリサイド化されたゲート配線19と、ゲート配線19の側面を連続的に覆う絶縁性のサイドウォール21とを備えている。ゲート配線19の少なくとも一部分は、サイドウォール21から突出して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】

接合リーク電流の発生が軽減されたエレベーテッド・ソース/ドレイン構造を有する半導体装置の製造方法を提供することができる。

【解決手段】

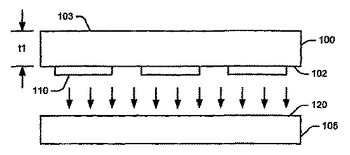

本発明に係る半導体装置の製造方法は、半導体基板102表面の所定の位置に溝部105を形成する工程と、溝部105を埋設するとともに、半導体基板102表面から突出した形状を有する素子分離膜106を形成する工程と、半導体基板102および素子分離膜106を覆うように膜108を形成する工程と、膜108を選択的に除去して、半導体基板102上に露出する素子分離膜106の側壁106aに保護膜110を形成する工程と、半導体基板102上にゲート電極部123を作製する工程と、保護膜110とゲート電極部123との間の半導体基板102の表面にエピタキシャル層124を形成する工程と、エピタキシャル層124の少なくとも一部にシリサイド層130を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ロールオフ特性の改善および接合リークの抑制を図った半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、半導体基板1に形成され、活性領域を区画する素子分離絶縁膜10と、活性領域における半導体基板1上にゲート絶縁膜2を介して形成されたゲート電極3と、ゲート電極3の両側における半導体基板1上に積層された2つのエクステンション層5と、ゲート電極3の側壁およびエクステンション層5の一部を覆うサイドウォール絶縁膜SWと、エクステンション層5上に積層された2つのソース・ドレイン層6と、ソース・ドレイン層6に形成されたシリサイド層7と、素子分離絶縁膜2の端部に生じた窪み部10aを埋めるように形成された埋め込み絶縁膜8bとを有する。

(もっと読む)

半導体構造の形成方法

【課題】ゲート金属層の側壁エッジ酸化を防止する半導体構造の形成方法を提供する。

【解決手段】ゲート電極は、ドープトシリコン層108と該ドープトシリコン層上の金属層112とからなり、側壁エッジに沿って第2シリコン層120を形成する過程であって、前記第2シリコン層120は、前記側壁エッジのドープトシリコン層領域108及び金属層領域112に沿っており且つ前記ドープトシリコン層より不純物が低濃度にドープされ、前記側壁エッジの金属層領域に沿ってシリサイドを形成するために、前記第2シリコン層のシリコンを前記金属層領域の金属と反応させる過程と、前記反応後、前記ドープトシリコン層のドープトシリコンに対して、前記第2シリコン層のシリコンを選択的に除去する過程と、前記第2のシリコン層のシリコンを選択的に除去した後、側壁エッジのドープトシリコン層領域を酸化する過程を具備することを特徴とする。

(もっと読む)

アクティブマトリクス基板の製造方法、その製造方法により製造されたアクティブマトリクス基板を備えた表示装置

【課題】アクティブマトリクス基板を製造する際に必要なフォトマスクの枚数を従来よりも減らすと共に、低消費電力駆動を実現する。

【解決手段】まず、第1のフォトマスクを用いて、ゲート線1、ゲート電極1a及びソース線下層部3aを形成する。次いで、第2のフォトマスク11を用いてレジスト層12を形成する。続いて、レジスト層12の第1開口部12aを介してn+アモルファスシリコン膜、真性アモルファスシリコン膜及びゲート絶縁膜4をエッチングする。その後、レジスト層12の第2開口部12bを介してn+アモルファスシリコン膜をエッチングして、ソース領域5b及びドレイン領域5cをパターニングして半導体層5を形成する。さらに、第3のフォトマスクを用いて、コンタクトホール6a、6b及び6cを形成する。最後に、第4のフォトマスクを用いて画素電極8a及びソース線3を形成する。

(もっと読む)

半導体装置の製造方法

【課題】カーボンナノチューブを形成するための触媒粒子を含有する薄膜層を容易かつ確実に溝構造底部に形成することができる半導体装置の製造方法を提供する。

【解決手段】シートフィルムFに感光性樹脂薄膜層1を塗布形成し、さらにその上層にカーボンナノチューブ形成のための触媒となる金属または金属化合物の粒子を含有するゲル状またはペースト状の触媒薄膜層2を塗布形成する。一方、半導体ウェハWのパターン形成面には下層配線層3および層間絶縁層4が形成されており、層間絶縁層4にはパターン化された溝部5が形成されている。これらのシートフィルムFと半導体ウェハWと押し付けて密着させることにより、感光性樹脂薄膜層1および触媒薄膜層2を半導体ウェハWに転写し、溝部5に感光性樹脂薄膜層1および触媒薄膜層2を充填する。その後、感光性樹脂薄膜層1と層間絶縁層4上面の触媒薄膜層2とを除去する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 リーク電流が十分に抑制可能な高誘電率絶縁膜20を有する半導体装置の製造方法を提供する。

【解決手段】 半導体領域19の上に高誘電率絶縁膜20をアトミックレイヤーデポジション法により成膜し、高誘電率絶縁膜20の上にアルミナ膜21をアトミックレイヤーデポジション法により成膜し、アルミナ膜21をアニールし、アルミナ膜21の上に導電層22を還元雰囲気下で成膜する。

(もっと読む)

半導体装置

【課題】High-k絶縁膜をゲート絶縁膜として使用する電界効果トランジスタを含む半導体装置であって、メタルゲート電極化を行わずに、フェルミレベルピニングに起因するしきい値電圧固定を抑制可能な半導体装置を実現する。

【解決手段】Pチャネル型電界効果トランジスタ4において、High-k絶縁膜たる金属酸化物(好ましくは、ハフニウム酸化物(HfO2やHfSiON、HfSiO4など)またはジルコニウム酸化物(ZrO2やZrSiON、ZrSiO4など))を有するゲート絶縁膜6bと、ポリシリコンゲート電極7との間に窒化チタン(TiN)膜8を形成する。窒化チタン膜は、金属酸化物を有するゲート絶縁膜に接して形成されてもフェルミレベルピニングが起きない。また、ポリシリコンゲート電極の下部が窒化チタン膜との金属膜となっているので、ゲートの空乏化が抑止でき、電流駆動能力向上も図れる。

(もっと読む)

半導体装置およびその製造方法

【課題】 トレンチゲート構造の半導体装置において、トレンチ上方コーナ部に結晶欠陥が生じることを抑制する。また、半導体装置の小型化が可能となる構造の半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極7の形状を、その断面がT字となるように、トレンチ5の内部から半導体基板4の表面に至って形成された形状とし、ソースとなるN+型領域15をトレンチ5から離れた位置であって、ゲート電極7における半導体基板4の表面上に位置する部分7aの下に配置した構造とした場合、ゲート電極7の上方部7aのトレンチ側壁5aに対するオーバラップ量を0.3μm以上とする。また、ゲート電極7とゲート配線10とを電気的に接続させるためのコンタクトホール18を、層間絶縁膜8のうち、トランジスタ領域内におけるトレンチ5の上方の位置に形成する。

(もっと読む)

相補型MOS装置およびその製造方法

【課題】相補型MOS(CMOS)装置とその製造方法を提供する。

【解決手段】本発明は、CMOS装置とその製造方法を提供し、PMOSトランジスタは、圧縮歪みSiGeチャンネルを有し、NMOSトランジスタは、キャップ層により生成される局部引っ張り歪みSiチャンネルを有する。前者により、歪みSiチャンネルのホール移動度増加不足の問題を克服し、歪みSiGeチャンネル、歪みSiチャンネルが、それぞれ、価電子帯、伝導帯において生じるバンドオフセットにより、等価バンドギャップを小さくし、高誘電率のゲート誘電層、および、単一の仕事関数を有する金属ゲートに適用し、整合しにくい二重金属のゲート問題を回避し、高移動度増加の歪みチャンネルMOSトランジスタが形成される。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】絶縁膜との密着度が高いフィールドプレート部を有するフィールドプレート構造に形成されて一層高耐圧化された電極を備えること。

【解決手段】HEMT100は、基板1上に、バッファ層2と、電子走行層3と、中間層6と、電子供給層4とを、この順に積層して形成された化合物半導体層を有し、電子供給層4上には、ソース電極7S、ゲート電極7Gおよびドレイン電極7Dと、これら複数電極間に挟み込まれた絶縁膜8と、を備える。ゲート電極7Gは、電子供給層4とショットキー接合したショットキー電極層7Gaと、このショットキー電極層7Ga上に積層され、ドレイン電極7Dに臨んで絶縁膜8上に張り出すとともに絶縁膜8上に密着する張出部としてのフィールドプレート部7FPを有したフィールドプレート電極層7Gbと、を用いてフィールドプレート構造に形成されている。

(もっと読む)

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

炭化ケイ素半導体デバイスを形成するいくつかの方法が開示される。これらの方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、炭化ケイ素基板の第1の表面にキャリア基板を取り付けるステップとを含む。キャリア基板は、炭化ケイ素基板に機械的支持を提供する。これらの方法はさらに、炭化ケイ素基板を、第1の厚さ未満の厚さまで薄くするステップ、炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、および炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面にオーミックコンタクトを形成するために、金属層を局所的にアニールするステップを含む。炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。  (もっと読む)

(もっと読む)

半導体装置

【課題】本発明は、Fin型MISFETにおいて、Finの下部で生じるパンチスルーを抑制できるようにする。

【解決手段】たとえば、Si基板11の表面上には、素子領域となるFin12が設けられている。Fin12には、ソース・ドレイン拡散層23a,23bが形成されている。ソース・ドレイン拡散層23a,23bの相互間には、チャネル部が形成されている。このチャネル部に対応する、上記Fin12の一部を覆うようにしてゲート電極部21が設けられている。ゲート電極部21は、第1の仕事関数を有する第1のゲート電極21a上に、第1のゲート電極21aとは異なる、第2の仕事関数を有する第2のゲート電極21bを積層してなる構成とされている。

(もっと読む)

基板処理装置、COR処理モジュール、及び基板リフト装置

【課題】成膜不良の発生を防止することができる基板処理装置を提供する。

【解決手段】CVD処理装置のPMはチャンバを備え、該チャンバは容器、該容器内に配置されたESC33、及び容器内に配置されたウエハリフト装置80を有し、ウエハリフト装置80は、容器内においてESC33を囲うように配置されている円環状のピンホルダ81と、ピンホルダ81に接続される3つのリフトアーム83と、各リフトアーム83に遊嵌結合されて担持される3つのリフトピン42とを有し、各リフトピン42は、ピンホルダ81の昇降に連動して昇降する。

(もっと読む)

半導体装置

【課題】 ゲート電極の実効仕事関数をトランジスタの動作閾値電圧が最適なものとなるように制御するこを可能にする。

【解決手段】 半導体基板2と、半導体基板上に設けられたゲート絶縁膜4と、ゲート絶縁膜上に設けられたゲート電極8と、ゲート電極の両側の半導体基板に設けられたソース・ドレイン領域12、14と、ゲート電極とゲート絶縁膜との界面に、ゲート電極およびゲート絶縁膜を構成する元素と異なる電気陰性度を有する元素を含む層5と、を備えている。

(もっと読む)

原子層蒸着法を利用した金属層形成方法およびこれを用いた半導体素子

【課題】原子層蒸着法を利用したステップカバレージが優秀で、所望する抵抗及び伝導度を容易に決定することができ、酸素の拡散を防止できる金属層形成方法、および前記金属層形成方法によって形成された金属層を障壁金属層、キャパシタの下部電極または上部電極として備えた半導体素子を提供する。

【解決手段】反応性金属A、窒素N、反応性金属と窒素との非晶質結合用元素Bの各ソースガスを、原子層蒸着法によって交互にチャンバー内に注入して各原子層を交互に積層させる金属層形成方法、およびこの方法によって形成された金属層を半導体素子の障壁金属層、下部電極または上部電極として備えてなる半導体素子。

(もっと読む)

半導体装置およびその製造方法

【課題】 金属ゲート電極形成時のゲート絶縁膜や半導体基板へのダメージを低減する。

【解決手段】 金属ゲート電極12,22を形成する際、第1,第2のMOSFET10,20を形成する領域に、一方には所定エッチング条件でエッチングレートの低い第1の金属層31を薄く形成し、他方にはその所定エッチング条件でエッチングレートの高い第2の金属層32を厚く形成して、第1,第2の金属層31,32を同時にエッチングする。それにより、それらのエッチングレート差が厚さの違いで相殺され、第1,第2の金属層31,32のエッチングを同時あるいはほぼ同時に終了させることが可能になる。それにより、ゲート絶縁膜11,21やSi基板2へのエッチングダメージを最小限に抑えることが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】 サイドウォール幅の減少を抑制し、ゲート電極が微細化された場合であっても接合リーク電流に起因する製造歩留まりの低下を回避することができる半導体装置の製造方法を提供する。

【解決手段】 ゲート電極3上にスペーサパターン13を形成し、サイドウォール6形成後にスペーサパターン13を除去する。当該手法により、ゲート電極3の高さより高い、もしくは同等の高さのサイドウォール6を形成した後、コンタクトホール21を形成する。これにより、ストッパ膜7を異方性エッチングする際にサイドウォール6の幅が減少することを抑制し、エクステンション領域が露出することにより生じる接合リーク電流に起因する半導体装置の歩留まり低下を抑制することができる。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】集積化MOSキャパシタの製造工数の削減を図る。

【解決手段】MOSトランジスタおよびMOSキャパシタを集積化する半導体装置の製法において、(A)トランジスタ形成領域100P内に第1導電型の不純物でチャネルドープを行い、同時に、キャパシタ形成領域200C内に第1導電型の第1不純物層38を形成する工程と、(B)トランジスタ形成領域100Pにゲート絶縁層70を形成し、キャパシタ形成領域200Cの第1不純物層38の上方に誘電体層30を形成する工程(C)ゲート絶縁層70の上方にゲート電極72を形成する工程、(D)誘電体層30の上方に導電層32を形成する工程、(E)トランジスタ形成領域100Pに第2導電型のソース74およびドレイン76を形成する工程と、(F)キャパシタ形成領域200Cの導電層32の側方の半導体層10内に、第1導電型の第2不純物層34および第3不純物層36を形成する工程を含む。

(もっと読む)

2,001 - 2,020 / 2,580

[ Back to top ]