Fターム[4M104HH20]の内容

Fターム[4M104HH20]に分類される特許

2,561 - 2,580 / 2,580

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

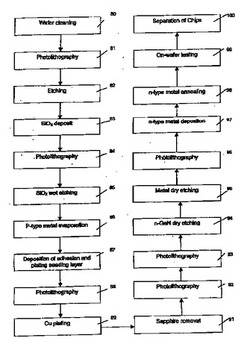

半導体デバイスの製造

基板上に半導体デバイスを製造する方法であり、半導体デバイスは、ウェーハを有する。本発明による方法は、(a)熱伝導性の金属からなる種層をウェーハに付加するステップと、(b)熱伝導性の金属からなる比較的に厚い層を種層上に電気メッキするステップと、(c)基板を除去するステップとを含む。また、それに対応する半導体デバイスが開示される。 (もっと読む)

半導体デバイス上における伝導性金属層の製造

基板上に発光デバイスを製造する方法であり、発光デバイスは、複数のエピタキシャル層および基板の反対側にあるエピタキシャル層上に存在するオーミック接触層を備えるウェーハを有する。本発明による方法は、(a)熱伝導性の金属からなる種層をオーミック接触層に付加するステップと、(b)熱伝導性の金属からなる比較的に厚い層を種層上に電気メッキするステップと、(c)基板を除去するステップとを含む。また、それに対応する発光デバイスが、開示される。発光デバイスは、GaN発光ダイオードまたはGaNレーザダイオードである。 (もっと読む)

長寿命スパッタ用ターゲット

スパッタ用ターゲット組立体20を製造する方法、及びその製品が提供される。本方法はバッキングプレート26を製造するステップを含み、バッキングプレートは平坦な上面とそこに円筒形状凹部28を備える。次に、バッキングプレート26の円筒形状凹部に対応する円錐台背面24及び前面を有する最終形状に近いターゲットインサート22が製造される。ターゲットインサート22はバッキングプレート26の降伏強度よりも大きな降伏強度を有し、かつバッキングプレート26の円筒形状凹部の深さよりも高さが大きい。その後、バッキングプレート26にターゲットインサート22を拡散接合し、ターゲット組立体を形成するために、塑性変形の状態までターゲット22をバッキングプレート26の円筒形状凹部28へ加温圧縮する。ターゲットインサート22はバッキングプレート26の平坦な面上に突出する。  (もっと読む)

(もっと読む)

スパッタ処理システムにおけるプラズマ遷移の制御

物質処理に使用されるプラズマを制御するための方法および装置は、プラズマ容器および電源に連結された、共振回路およびスイッチ部の共同作用を特徴とする。プラズマ容器にあるプラズマの状態に関連する信号を取得するためのセンサーは、前記スイッチ部のクローズドループ制御に対応している。共振回路を短絡するためにスイッチ部を閉じることにより、前記センサーによって検出されたプラズマの好ましくない状態を取り除くことができる。 (もっと読む)

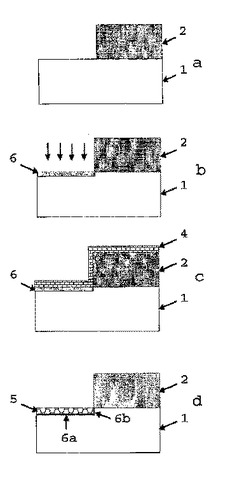

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

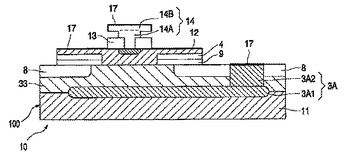

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

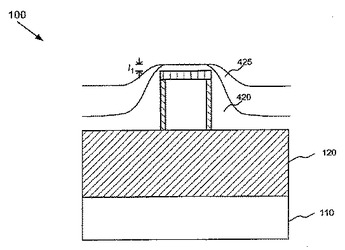

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

PN接合ダイオード装置及びその製造方法

【課題】より小型が可能なPN接合ダイオード装置及びその製造方法を提供することにある。

【解決手段】PN接合ダイオードのカソード電極22及びアノード電極23を共に、シリコン基板10の一方の主面に形成することにより、カソード電極22及びアノード電極23とをリードフレーム26に、ワイヤー等で接続することなく、接着することを可能にする。

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

熱処理装置

【課題】 例えば50〜600℃程度の低温域での降温率を高くでき、熱処理のスループットを向上させることが可能な熱処理装置を提供する。

【解決手段】 被処理体Wに対して所定の熱処理を施す熱処理装置40において、排気可能になされた筒体状の処理容器42と、複数の前記被処理体を多段に保持して前記処理容器内へ挿脱される被処理体保持手段58と、前記処理容器内へ所定の処理ガスを導入する処理ガス導入手段78と、前記処理容器の内側に配置されて前記被処理体を加熱する加熱手段76と、前記処理容器の壁面を冷却する容器冷却手段110と、を備える。これにより、全体としての熱容量が小さくなり、しかも、処理容器の壁面が冷たいので、低温域での降温率(降温速度)及び動特性を大幅に向上させることが可能となる。

(もっと読む)

配線構造並びにその形成方法及び装置

【課題】 凹部への埋め込み性が良好で、長期に亘り安定した良好な電気的特性を得ることができ、さらに作製工程を可及的に低減し得る配線構造を提供する。

【解決手段】 Cu板と基板3との温度及び温度差を所定通りに制御しつつ、原料ガスであるCl2 ガスのプラズマによりCu板をエッチングすることによりCu成分とCl2 ガスとの前駆体であるCuClを形成し、この前駆体が基板3に吸着され、その後Cu成分を析出させることによりCuの薄膜を形成する成膜反応と、この成膜反応により形成されたCu膜をCl2 ガスのプラズマでエッチングするエッチング反応とを共存させるとともに、前記成膜反応の速度が前記エッチング反応の速度よりも大きくなるように制御することにより前記凹部3aにその底部から順にCu膜を積層してこの凹部3aにCuを埋め込んだ。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

窒化物系III―V族化合物半導体装置の電極構造

【課題】 半導体上の膜付着力が強く、かつ温度特性が優れたショットキー電極を備えた窒化物系III−V族化合物半導体装置の電極構造を提供する。

【解決手段】 この窒化物系III−V族化合物半導体装置の電極構造は、電極4の材料として金属窒化物(窒化タングステン)を用いたので、半導体GaN層3への膜付着力が強く、かつ、加熱によってショットキー特性が劣化することがないショットキー電極4を得ることができた。

(もっと読む)

2,561 - 2,580 / 2,580

[ Back to top ]