Fターム[4M106BA01]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | プローバ (2,607)

Fターム[4M106BA01]に分類される特許

121 - 140 / 2,607

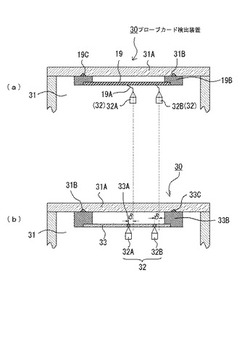

プローブカード検出装置、ウエハの位置合わせ装置及びウエハの位置合わせ方法

【課題】検査室内においてプローブカードのプローブの針先を検出することなくプローブカードと半導体ウエハの位置合わせを行うことができ、また、ダミーウエハを用いる必要がなく、迅速にプローブと半導体ウエハの位置合わせを行うことができるプローブカード検出装置を提供する。

【解決手段】プローブカード検出装置30は、プローブカード19またはプローブ補正カード33を所定位置に位置決めして着脱可能に装着される支持体31Aを有するプローブ検出室31と、プローブ検出室31内に移動可能に設けられ且つプローブ19Aの針先またはターゲット33Aを検出する第1、第2のカメラ32A、32Bと、を備え、第1、第2のカメラ32A、32Bで検出される、2つのプローブ19Aの針先の水平位置と2つのターゲット33Aの水平位置との差を、プローブ19Aと半導体ウエハの電極パッドのアライメントを行うために用いられる補正値δとして検出する。

(もっと読む)

半導体装置の検査方法および検査装置

【課題】半導体ウエハ上に形成された半導体装置の特性不良を精度よく検出することができる半導体装置の検査方法および検査装置を提供すること。

【解決手段】実施形態によれば、第1ウエハ検査工程と、2ウエハ検査工程と、判定工程とを含む半導体装置の検査方法が提供される。第1ウエハ検査工程は、複数個の半導体装置に同時にプローブ針を接触させるプローブカードを用いて半導体ウエハ上に形成された半導体装置の特性を検査する。第2ウエハ検査工程は、第1ウエハ検査工程によって特性不良と判定された半導体装置の半導体ウエハ上の分布に基づいて、プローブカードの半導体ウエハに対する位置を第1ウエハ検査工程の位置からずらして、半導体装置の特性を再検査する。判定工程は、第2ウエハ検査工程による再検査の結果に基づいて、半導体装置の特性不良のうち、複数個の半導体装置単位で行われる製造処理において生じる特性不良を判定する。

(もっと読む)

工程解析システム、工程解析プログラムおよび工程解析方法

【課題】工程間時間に基づいた工程解析を容易に行うことができる工程解析システムを提供すること。

【解決手段】実施形態の工程解析システムは、基準判定部が、各ロットの工程間時間が基準範囲内であるか否かを工程毎に判定する。割合算出部は、前記工程間時間が基準範囲外となったロットの割合を工程毎に算出する。基準外工程抽出部は、前記割合が所定値以上である工程を基準範囲外工程として抽出し、所定期間における抽出回数を前記工程毎に記憶部に記憶させる。工程抽出部は、前記抽出回数に基づいて、トラブル発生の可能性がある工程を抽出する。相関関係算出部は、抽出された工程で処理されたロット内の基板が有する回路パターンに関する特性と、前記工程間時間と、の相関関係を算出する。限界値算出部は、前記相関関係に基づいて、前記工程間時間の限界値を算出する。

(もっと読む)

故障診断支援方法、プログラム及び装置

【課題】特徴の数に対して十分な量の故障データがないケースに対処する。

【解決手段】本方法は、故障について検討すべき第1半導体装置と当該第1半導体装置と同じ回路を実装した第2半導体装置とについての分類要素のグループ毎に当該グループにおいて発生した実故障数と故障要因となる各特徴についての特徴量とを含むデータと予め定められた算出式とから、特徴とグループとの組み合わせ毎に故障数期待値を算出するステップと、特徴とグループとの組み合わせ毎の故障数期待値と、グループ毎の実故障数とから、各特徴について、グループに渡る故障数期待値の分布とグループに渡る実故障数の分布との類似度を表す指標値を算出するステップとを含む。

(もっと読む)

電子部品検査装置用配線基板およびその製造方法

【課題】設計に要する時間および製造期間を短縮することができ、且つ比較的少ない治具で容易に製造できる電子部品検査装置用配線基板とその製造方法を提供する。

【解決手段】表面4および裏面5を有し且つ少なくとも表面4が絶縁層にて形成された基板本体2aと、該基板本体2aの表面4における中心側に複数のプローブ用パッド6が形成されたプローブ用パッド領域paと、基板本体2aの表面4における周辺側で且つプローブ用パッド領域paの外側に複数の外部接続端子7が形成された外部接続端子領域caと、を備えた電子品検査装置用配線基板1aであって、上記プローブ用パッド6と外部接続端子7との間は、上記基板本体2aの表面4における上記2つの領域pa,ca間に形成された表面配線8によって接続されている、電子品検査装置用配線基板1a。

(もっと読む)

テストプローブ用のクリーニングパッドおよびテストプローブのクリーニング方法

【課題】プローブ先端形状が変化しても針入抵抗の変化を小さくでき、研磨層(クリーナ層)に対する針入量のバラツキを小さくして全てのテストプローブを均一にクリーニングする。また表面での付着物捕捉作用を増大させてテストの信頼性向上と製品の歩止まり向上を可能にする。

【解決手段】微細な研磨剤が混入されかつテストプローブ(16,18)の先端が進入可能な研磨層(42)と、この研磨層(42)の少なくとも一方の表面に積層され高分子ゲルから成る表面層(44)とを備え、テストプローブ(16,18)の先端を表面層(44)から研磨層(42)に進入させることによりクリーニングする。

(もっと読む)

ウエハ検査装置及びプローブカードのプリヒート方法

【課題】ウエハ検査装置の設置スペースを削減することができると共に設置コストを低減することができるウエハ検査装置を提供する。

【解決手段】本発明のウエハ検査装置10は、ウエハを一枚ずつ搬送するように第1の搬送領域S2に設けられた第1のウエハ搬送機構12と、第1の搬送領域の端部にあるアライメント領域S3内でウエハ保持体15を介して第1のウエハ搬送機構12によって搬送されるウエハWを検査位置にアライメントするアライメント機構14と、第1の搬送領域S2及びアライメント領域S3に沿う第2の搬送領域S4内でウエハ保持体15を介してウエハWを搬送する第2のウエハ搬送機構16と、第2の搬送領域に沿う検査領域S5に配列され且つウエハ保持体15を介して第2のウエハ搬送機構16によって搬送されるウエハWの電気的特性検査を行う複数の検査室17と、を備え、検査室17ではアライメント後のウエハの電気的特性検査を行う。

(もっと読む)

冷却装置の運転方法及び検査装置

【課題】検査装置に用いられる冷却装置の消費エネルギーを節減することができる冷却装置の運転方法を提供する。

【解決手段】冷却装置及び加熱装置を介して温度調節可能なウエハチャック上に半導体ウエハを載置し、制御装置の制御下で半導体ウエハの低温検査及び半導体ウエハの高温検査を行う際に、制御装置の制御下でウエハチャックを冷却する冷却装置を制御する方法であって、低温検査を行う時には制御装置を介して冷却装置を連続的に運転し、高温検査を行う時には、制御装置を介して高温検査の開始に合わせて冷却装置を少なくとも一回停止する。

(もっと読む)

プローブカード及びその製造方法

【課題】半導体チップに形成された複数の電極パッドに確実に接触させることが可能なプローブカードを提供すること。

【解決手段】プローブカード40の基板本体51には、第1の主面51aと第2の主面51bとの間を貫通する貫通孔52が形成されている。貫通孔52の第1の収容部52a内には弾性体56が形成され、第2の収容部52b内には、貫通電極54が形成されている。弾性体56の表面には配線55により貫通電極54と接続される配線57が形成されている。配線57の先端は、弾性体56の下面略中央に配置されている。そして、配線57の先端下面には、検査対象物10の電極パッド11と対応する位置に、その電極パッド11と電気的に接続される接触用バンプ41が形成されている。

(もっと読む)

電子部品検査装置用配線基板

【課題】設計に要する時間および製造期間を短縮することができ、且つ比較的少ない治具で容易且つ安価に製造できる電子部品検査装置用配線基板を提供する。

【解決手段】表面22および裏面23を有する絶縁材からなり、該表面22と裏面23との間を貫通する複数の第1ビア導体25と、該第1ビア導体25ごとの両端に個別に接続される表面側の第1端子26および外部との導通に用いる裏面側の外部端子27とを有するベース基板20と、該ベース基板20の表面22に実装され、少なくとも表面4側が絶縁材からなり、該表面4にプローブpを取り付けるための複数のプローブ用パッド6、およびベース基板20の第1端子26と導通するための複数の第2端子7を有する実装用基板2と、を備える電子品検査装置用配線基板1aであって、上記表面4の中心側のプローブ用パッド6と該表面4の周辺側の第2端子7との間を接続する表面配線8が実装用基板2の表面4に形成されている、電子品検査装置用配線基板1a。

(もっと読む)

半導体装置の製造方法および補強板

【課題】半導体基板の薄化工程および薄化後の工程において半導体基板を補強し、且つ補強したまま素子特性が取得できる半導体装置の製造方法および補強板を提供する。

【解決手段】一つの実施形態によれば、半導体装置の製造方法では、半導体基板11を接着剤42で覆い、補強板30を第1パッド16、17、18と第1貫通孔31、32、33が上下重なるように接合する。半導体基板11を第2の面11b側から所定の厚さになるまで除去し、所定の処理を施した後、電極膜19を形成する。第1貫通孔31、32、33に接着剤40の除去液43を注入して、第1パッド16、17、18を露出させる。第1パッド16、17、18に第1貫通孔31、32、33を通してプローブ45、46、47を当接し、プローブ45と電極膜19の間の電流を測定する。第1貫通孔31、32、33に除去液51を注入し、半導体基板11と補強板30を分離する。

(もっと読む)

プローブのクリーニング装置およびその装置を用いたプローブのクリーニング方法

【課題】半導体デバイスや集積回路などのテスト工程で使用されるプローブの先端に付着した異物を除去するクリーニング装置で、プローブ先端のスティックスリップ発生を防止した装置を提供する。

【解決手段】先端部が球面状あるいはその球面状の先端部の中途から直線で延伸する傾斜部が設けられたプローブ11を装着する鉛直方向駆動機構23と、クリーニングシート50を固定するステージ30、40の水平方向駆動機構32、42と制御装置60を備え、制御装置60によってクリーニングシート50へのプローブ11の押し込み量が連続的に所定値に増加するよう鉛直方向駆動機構23で、クリーニングシート50に対するプローブ先端部12の移動軌跡が閉ループとなるよう水平方向駆動機構32、42が駆動制御される。

(もっと読む)

プローブ支持板の製造方法、コンピュータ記憶媒体及びプローブ支持板

【課題】プローブ支持板を短期間かつ低コストで製造する。

【解決手段】プローブ支持板11の製造方法であって、複数の金属薄板20をそれぞれエッチングして、各金属薄板20にプローブ10を挿入させるための複数の貫通孔21を形成するエッチング工程と、その後、複数の金属薄板20の各貫通孔21が金属薄板20の厚み方向にそれぞれ連結されるように、複数の金属薄板20を積層し、当該複数の金属薄板20を接合する接合工程と、その後、各貫通孔の内側面21に絶縁膜22を形成する膜形成工程と、を有する。前記エッチング工程において、最上層と最下層との間に積層される中間層の金属薄板20cの貫通孔21cを、最上層と最下層の金属薄板20a、20bの貫通孔の径21a、21bより大きい径で形成する。

(もっと読む)

半導体素子試験方法および半導体素子試験装置

【課題】ウエハテストで仕様最大電圧の試験を行うときに、半導体素子の電極間の距離を広げる方法や高価なプローバを使用する方法を用いずに、高電圧印加時の空気放電を防止することができる半導体素子試験方法および半導体素子試験装置を提供する。

【解決手段】複数の半導体素子が作成されたウエハに対し、該半導体素子の電気的特性を検査する半導体素子試験方法であって、上記複数の半導体素子のうち検査対象の半導体素子の電極を、外部端子と電気的に接続させるステップ(S11)と、上記電極と上記外部端子とが電気的に接続された状態で、上記検査対象の半導体素子の表面に、供給部から電離性の低い液体または気体を供給するステップ(S12)と、上記表面が上記液体または気体で覆われた状態で、上記検査対象の半導体素子に、電圧印加部から上記外部端子を介して試験電圧を印加するステップ(S13)とを含む。

(もっと読む)

ウエハプローバ用ウエハ保持体及びそれを搭載したウエハプローバ

【課題】 高精度な温度分布の実現と共に、急速な昇温や冷却時あるいはプロービングによる押圧時にチャックトップの変形や破損がなく、チャックトップ平面度を維持することができ、繰り返し使用しても正確で高精度の測定を実現できるウエハ保持体及びそれを搭載したウエハプローバ装置を提供する。

【解決手段】 ウエハプローバ用ウエハ保持体1は、表面にチャックトップ導体層3を有し且つ加熱体4を備えるチャックトップ2と、チャックトップ2を支持する複数の支持棒5と、支持棒5が設置される底部基板6とからなり、支持棒5はチャックトップ1の裏面側を部分的に支持している。また、支持棒5のチャックトップ支持部合計面積は、チャックトップ2の裏面全面積の15%以下であることが好ましい。チャックトップ2は冷却モジュールを備えることができる。

(もっと読む)

電子デバイスをテストするためのシステムの動作周波数を増加させるための装置

【課題】DUTがテストされることができる周波数を増加させる。

【解決手段】テストシステムは、テストされる電子デバイス112の入力端子208,210と接触するプローブ110d,110e内を終端とする、通信チャネル220,222を備える。抵抗が、プローブの近くの通信チャネル220,222と接地の間に接続されている。抵抗は、端子の入力抵抗を減少させ、それによって入力端子208,210の立上がりおよび立下がり時間を減少させる。分路抵抗402,404が、各分岐内に設けられており、このことが、端子の入力抵抗を減少させ、それによって入力端子208,210の立上がりおよび立下がり時間を減少させる。分路抵抗402,404はまた、チャネルを戻る信号反射を減少、最小化、または除去するようにサイズ調整されてもよい。

(もっと読む)

半導体製造装置及び半導体装置の製造方法

【課題】半導体ウェハの表面と裏面が電気的に導通していない場合でも、インクの付着を検知する装置及び方法を提供する。

【解決手段】導電性の中芯5を持つインカー1により半導体ウェハ7上の特定箇所に導電性インク2を付着させる。半導体ウェハ7上のパッド8に端子6をプロービングさせる。中芯5と端子6との間に流れる電流を測定器9により測定する。導電性インク2を介して中芯5と端子6との間に流れる電流が測定器9により測定された場合に、半導体ウェハ7上に導電性インク2が正しく付着したと判定する。

(もっと読む)

フリップチップパッケージ用基板の電気検査方法

【課題】微細化したパッケージ基板の電気検査において微細なプローブを使用せず、コスト低減が可能な電気検査方法及び製造方法の提供。

【解決手段】半導体チップを接続する面の最外層の電極と半導体チップを接続しない面の最外層の電極が形成された段階のフリップチップパッケージ用基板の電気検査方法であって、少なくとも前記フリップチップパッケージ用基板の半導体チップとの接続を行う面に金属層を形成する工程と、電気検査工程とからなり、前記電気検査工程は、前記金属層の任意の位置にプローブを当て、同時に半導体チップを接続しない面の電極にプローブを当てて導通検査を実施することを特徴とするフリップチップパッケージ用基板の電気検査方法。

(もっと読む)

プローブカードの位置決め機構及び検査装置

【課題】検査装置のインサートリングまたはヘッドプレートに対してプローブカードを位置ズレすることなく所定の位置に正確に装着することができ、特にプローブカードを繰り返し使用する場合でも一度だけプローブアライメントを行えば、その後のプローブアライメントを省略することができるプローブカードの位置決め機構を提供する。

【解決手段】本発明の位置決め機構19は、プローブカード12の外周縁部に互いに周方向に所定間隔を空けて設けられた3箇所の位置決め用のピン19Aと、これらのピンに対応してインサートリング15の内周縁部15Aに互いに周方向に所定間隔を空けて設けられた位置決め用の孔19Bと、を備え、位置決め用の孔19Bは、その向きがプローブカード12の径方向と実質的に一致する長孔として形成され、且つ、長孔19Bの内周面全面がピン19Aの挿入方向に向けて徐々に縮小するテーパ面19B1として形成されている

(もっと読む)

半導体試験装置

【課題】テストプログラムの作成変更修正が効率よく行える半導体試験装置を提供すること。

【解決手段】所望の画面を選択するためのタブが設けられた画面を表示する表示部を有し、テストプログラムを作成変更修正するエディタと、このエディタで作成変更修正されたテストプログラムを解析する構文解析部と、この構文解析部の解析結果に基づき各種のマトリクス表示のGUI画面を編集作成するGUI画面編集部と、前記構文解析部の解析結果および前記GUI画面編集部で編集作成されたGUI画面に基づきデータ検索用一覧表を作成格納するインデクサとを具備し、前記インデクサのデータ検索用一覧表を介して、前記GUI画面におけるマトリクス表示の各交点を前記テストプログラムの構成要素にリンクさせることを特徴とする半導体試験装置である。

(もっと読む)

121 - 140 / 2,607

[ Back to top ]