Fターム[4M106BA01]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | プローバ (2,607)

Fターム[4M106BA01]に分類される特許

41 - 60 / 2,607

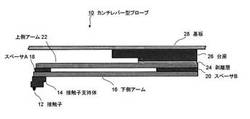

同一箇所から分離可能なカンチレバー型プローブ

【課題】シングルアーム構成及びダブルアーム構成のカンチレバー型プローブの交換をする際に、アーム部が引き剥がし易いプローブ構造を提供する。

【解決手段】接触子12と、一方の端部に前記接触子12が取り付けられ、他方の端部が固定された板材で構成されたアーム部とから成るプローブを備え、アーム部の固定は、基板に接合された台座26に、剥離層24を介して接合されていることを特徴とするプローブカードである。剥離層24は、台座26と基板28の接合部よりも狭い面積である。また、アーム部は、スペーサを介して下側アーム16と、下側アーム16の厚さと同等かより厚い上側アーム22の2つのアームを備えたダブルアーム構造とし、台座26に剥離層24を介して接合され、下側アーム16を上側アーム22より長くしたことを特徴とするプローブカードである。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性の双方をウエハレベルで測定することができ、特に静特性に使用される測定ラインに影響されることなく、パワーデバイスの動特性をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、複数のパワーデバイスが形成されたウエハWを載置する移動可能な載置台12と、載置台12の上方に配置された複数のプローブ14Aを有するプローブカード14と、載置台12の載置面とその外周面に形成された導体膜電極13と、導体膜電極13とテスタ17とを電気的に接続する測定ライン16と、を備え、載置台12上のパワーデバイスの電気的特性をウエハレベルで測定するプローブ装置であって、第2の測定ライン16には、導体膜電極13とテスタ17の間で測定ライン16の電路を開閉するスイッチ機構18を設けたものである。

(もっと読む)

半導体チップテスト方法、半導体チップテスト装置

【課題】高い信頼性を有する半導体チップテスト方法及び半導体チップテスト装置を提供する。

【解決手段】(a)所定の関連を有する所定枚数の半導体ウェハ上に形成された各半導体チップについて、ウェハ状態またはチップ状態でその電気的特性を検査し、良否判定する工程と、(b)前記所定枚数の半導体ウェハ上の前記半導体チップの前記判定結果から、前記判定結果がNGである前記半導体チップの割合を、前記半導体チップの前記半導体ウェハ上の位置を示すウェハアドレス毎に不良率として算出する工程と、(c)前記不良率が閾値以上と算出された前記ウェハアドレスに係る前記半導体チップについて、前記判定結果が良の場合に当該判定結果を否に更新する工程とを備える半導体チップテスト方法及び装置。

(もっと読む)

位置決め機構付ステージおよびその動作方法ならびに半導体装置の製造方法

【課題】半導体ウェハをステージ上に配置する際、確実に位置決め精度を向上させることができる技術を提供する。

【解決手段】本発明における位置決めガイドPAGがリング形状をしているため、半導体ウェハの外縁部全体にわたって位置決めガイドPAGで保持することができる。このことから、たとえ、半導体ウェハの外縁部の一部に割れやカケが存在していても、本発明における位置決めガイドPAGによれば、半導体ウェハを確実に保持することができる。

(もっと読む)

半導体検査装置、および半導体検査方法

【課題】本発明は、テストパターンを長く複雑なパターンにする必要がなく、スクリーニングで検出することができる回路パターンの不具合の割合を増やすことができる半導体検査装置、および半導体検査方法を提供する。

【解決手段】本発明は、半導体基板に形成した複数の半導体チップに対してスクリーニングを行なう半導体検査装置10である。半導体検査装置10は、ステージ2と、プローブ4と、テスタ部8と、光検出部5と、発光解析部6と、主制御部7と、異常判定部9とを備えている。光検出部5は、光学的なスクリーニングを行なうために、回路パターンに印加した電気信号に基づく発光を、半導体基板の他方の面側から検出する。異常判定部9は、テスタ部8で検出した出力信号に基づき、回路パターンの不具合を判断し、発光解析部6で解析した発光に基づき、回路パターンの不具合を判断して、半導体チップの異常を判定する。

(もっと読む)

検査用プローブ及びその製造方法

【課題】被検査体の電極への影響を抑えつつ効率的に被検査体の検査を行うことができる低コストの検査用プローブ及びその製造方法を提供する。

【解決手段】絶縁性の基板12と、基板12の縁部から外に延在されて並列に配置された弾性を有する複数の導電性の接触子13と、基板12に形成されて接触子13と導通する配線パターン14とを備え、被検査体の検査を行う際に接触子13の先端からなる接点15が被検査体の電極に接触される検査用プローブ11であって、接触子13及び配線パターン14が、MEMS技術によって基板12に形成され、接触子13の接点15における電極との接触箇所に、凸曲面状に突出する電極接触凸部16が形成されている。

(もっと読む)

プローブカード、半導体装置、半導体装置の試験方法、及び、半導体装置の製造方法

【課題】差動伝送方式を採用した半導体装置の試験で行われるTDRタイミング測定の校正精度の低減を抑制すること。

【解決手段】複数のプローブ針を有し、プローブ針を半導体装置の電極パッドと接続させて所定の試験を行うためのプローブカードであって、互いに異なる電極パッドP1及びP2に接続するよう配置され、対となっている差動信号入力用の第1及び第2のプローブ針1a及び2aと、互いに異なる電極パッドP1及びP2に接続するよう配置された第3及び第4のプローブ針1b乃至2b´と、第3及び第4のプローブ針1b乃至2b´各々と接続して、第3及び第4のプローブ針1b乃至2b´を導通させる配線3及び抵抗部材RTと、を有し、第3及び第4のプローブ針1b乃至2b´、配線3及び抵抗部材RTは電気的にフローティングな状態となっている。

(もっと読む)

スクリーニング方法、スクリーニング装置およびプログラム

【課題】半導体装置の特性がウエハ上の位置に応じて変動する場合においても、半導体装置の不良品を高い精度で検出できるようにすること。

【解決手段】スクリーニング方法は、ウエハに含まれる複数の半導体装置のそれぞれの電気的特性値を測定する工程と、前記ウエハ上における前記複数の半導体装置のそれぞれの位置情報を取得する工程と、前記複数の半導体装置の電気的特性値の変動のうちの前記ウエハ面上で相対的に緩やかに変動する成分を、前記複数の半導体装置のそれぞれの電気的特性値から差し引いて、前記複数の半導体装置のそれぞれの電気的特性値を補正する工程と、前記補正後の電気的特性値の分布を前記複数の半導体装置に対して生成する工程と、前記分布に基づいて、前記補正後の電気的特性値が外れ値となる半導体装置を前記複数の半導体装置の中から検出する工程と、を含む。

(もっと読む)

プローバにおけるウエハ上のチップ配列検出方法

【課題】プローバで、大チップのウエハでも、ウエハ上のチップ配列の検出が、オペレータの負担を軽減して行えるようにする配列検出方法を提供する。

【解決手段】ウエハW上に規則的に形成されたチップの動作を電気的に検査するため、テスタの各端子をチップの電極に接続するプローバにおいて、ウエハステージ上にロードされたウエハ上のチップの配列を検出する方法であって、ウエハの中心位置を検出し(S13)、ウエハアライメントカメラで、相対位置を変化させながらウエハの表面画像を複数回撮像し、撮像した画像を合成してウエハの中心位置から所定範囲の表面画像を生成し(S15)、所定範囲の全体が表示されるように合成ウエハ表面画像を表示し(S16)、指示されたストリートの交点を登録し(S17)、指示されたチップ内のアライメントマークを登録し(S19)、異なるチップのアライメントマークを検出して位置関係からチップの配列を算出する。

(もっと読む)

接続端子及び接続治具

【課題】円筒形状部が抵抗溶接による固定の前後においてほぼ円形形状を維持している接続端子を提供する。

【解決手段】対象点間を接続する接続治具に用いられる接続端子は、小径の導電部とそれを囲むように配置された大径の円筒形状部とを備え、小径の導電部の先端部が、大径の円筒形状部の先端部から突出し、小径の導電部の一部が、大径の円筒形状部の一部に接合されており、小径の導電部に接合された大径の円筒形状部の部分を少なくとも含む円筒形状部の軸線の周りの帯状部分の一部に切欠き部が形成されている。

(もっと読む)

試験器インタフェース接触要素及び支持ハードウエアを清浄化するための器具、装置、及び方法

【課題】試験器インタフェース接触要素及び支持ハードウエアを清浄化するための装置を提供する。

【解決手段】試験される半導体ウェーハ、個別化IC装置、又はパッケージ化IC装置にウェーハ探針器又はパッケージ装置ハンドラ内に清浄化媒体20を装着する段階を含み、清浄化媒体は、研磨性、粘着性、硬度のような所定の特性を有し、接触要素及びサポート構造体を清浄化する上面を有する。接触要素を清浄化媒体に接触させる段階を更に含み、それによってウェーハ探針器又はパッケージ装置ハンドラの通常の作動中にプローブ要素からあらゆるデブリが除去される。

(もっと読む)

半導体テスタおよび半導体試験装置

【課題】プローブと半導体ウェハとの接触精度を高める半導体テスタを提供する。

【解決手段】プローバ装置200のステージ210と機械的に接続する接続機構115と、プローバ装置200のプローブカードホルダ220と、プローバ装置200のステージを介さずに機械的に接続し、プローブカードホルダ220を固定する固定機構120とを備えた半導体テスタ100。固定機構120は、さらに、プローブカードホルダ220を半導体テスタ100方向に搬送する動作を行なうことができ、搬送する動作により、プローブカードホルダ220に搭載されたプローブカード500と電気的に接続するコネクタ112を備えるようにしてもよい。

(もっと読む)

膜抵抗値測定方法

【課題】成膜直後の基板面内における酸化物半導体膜の抵抗値を効率よく測定することができる膜抵抗値測定方法を提供する。

【解決手段】測定対象物Wを基板表面に成膜した酸化物半導体膜とし、成膜直後の酸化物半導体膜を局所的に加熱する工程と、この加熱した領域で抵抗値測定用プロープ6を用いて抵抗値を測定する工程とを含む。酸化物半導体膜として、例えばIn−Ga−Zn−O系材料からなる透明酸化物半導体膜を用いることができる。

(もっと読む)

電気特性取得評価方法

【課題】電気特性取得評価方法に関し、試料側にもプローブ側にも問題を発生させることなく安定な電気特性取得評価を行う。

【解決手段】積層体の表面側電極に対するコンタクトホール21を露出する工程と、前記露出したコンタクトホール21に導電性物質を埋め込んで凸状構造22を形成する工程と、前記凸状構造22を含む領域にカンチレバーを間欠接触測定方式で接触させて前記凸状構造22の位置を認識する工程と、前記凸状構造22の中心軸の方向に前記カンチレバーを押しつけて電気特性を取得する工程とを設ける。

(もっと読む)

半導体素子の検査処理方法

【課題】磁気センサ等の半導体素子の特性検査から梱包までの一連の作業をトレイを使用することなく効率的に行う。

【解決手段】各半導体素子10をダイシングテープ31上でマトリクス状に並べられた状態に分離する工程と、各半導体素子10をダイシングテープ31毎載置して水平方向及び垂直方向に移動しながらプローブに接触させて検査するプローブ検査工程と、プローブ検査工程を経た後の各半導体素子10をダイシングテープ31上から少なくとも1個ずつピックアップして搬送テーブル32上に搭載し、搬送テーブル32により順次搬送される半導体素子10の第1の主面10aを外観検査する第1の主面検査工程と、第1の主面検査工程を経た後の半導体素子10を把持して反転し、半導体素子10の第2の主面10bを外観検査する第2の主面検査工程と、第2の主面検査工程を経た後の半導体素子10を順次ピックアップして梱包する梱包工程とを備える。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の内部配線層の数を一定とした場合において、DUT部内に配設することが可能な特定電極パッドの数を導出することが可能な配線基板の製造技術を得、これによって、DUT部内に所定の数の特定電極パッドを配設する際に必要とされる内部配線層の最低数を導出することができ、配線基板を小型化及び簡略化する。

【解決手段】特定内部配線層の層数をA、各DUT部内に配設された複数の表面電極パッドの列数をN、及び各DUT部内に配設すべき特定表面電極パッドの個数をBとした場合において、特定表面電極パッドの個数Bは、

B<(X+1)×A

(Xは、1からNまでの自然数)

なる関係式を満足するようにする。

(もっと読む)

半導体装置の検査方法、検査プログラム及び半導体装置の検査装置

【課題】短時間で半導体装置の検査を行うことができる半導体装置の検査方法、検査プログラム及び半導体装置の検査装置を提供すること。

【解決手段】本発明は、記憶部2から半導体装置SD1の特性データDAT1を読み込む。次いで、ストローブ演算式212にNMOSトランジスタの閾値Vt1を代入することにより、半導体装置SD1に対するストローブ値STB1する。次いで、半導体装置SD1にテスト入力信号Dinを出力する。そして、ストローブ値STB1で指定されるタイミングで、半導体装置SD1から出力されるテスト出力信号Doutのパターンが期待値パターンEPと一致するかを判定する。

(もっと読む)

ウエハ搬送装置

【課題】複数の検査室によって共有することによりフットプリントを削減することができるウエハ搬送装置を提供する。

【解決手段】本発明のウエハ搬送装置10は、筐体Fを収納するウエハ収納室11と、ウエハ収納室11の下側に配置されたプリアライメント室12と、ウエハ収納室11及びプリアライメント室12に沿って上下方向に配置され且つウエハ収納室11とプリアライメント室12との間で半導体ウエハを搬送する第1のウエハ搬送機構13を有する第1のウエハ搬送室14と、第1のウエハ搬送室14とでプリアライメント室12を挟む位置に配置されアライメント室15と、第1のウエハ搬送室14、プリアライメント室12及びアライメント室15の配列方向に沿って移動すると共に上下方向に移動する第2のウエハ機構16を有する第2のウエハ搬送室17と、を備えている。

(もっと読む)

パワーデバイス用のプローブカード

【課題】プローブとテスタ間の測定ラインと載置台とテスタ間の測定ラインそれぞれの抵抗を格段に低減し、プローブ装置の実機として使用しても信頼性を十分に確保することができるパワーデバイス用のプローブカードを提供する。

【解決手段】本発明のプローブ装置10は、パワーデバイスSのエミッタ電極に電気的に接触する第1のプローブ11と、第1のプローブ11が接続されたブロック状の第1の接続端子12と、パワーデバイスDのゲート電極に電気的に接触する第2のプローブ13と、第2のプローブ13に接続されたブロック状の第2の接続端子14と、パワーデバイスDのコレクタ電極側に電気的に接触し得るコンタクトプレート15と、コンタクトプレート15に固定されたブロック状の第3の接続端子16と、を備え、第1、第2、第3の接続端子12、14、16は、それぞれが対応するテスタ側の接続端子に電気的に直に接触される。

(もっと読む)

41 - 60 / 2,607

[ Back to top ]