Fターム[4M112DA14]の内容

Fターム[4M112DA14]に分類される特許

1 - 20 / 98

振動式トランスデューサの製造方法

容量性トランスデューサとその製造及び動作方法

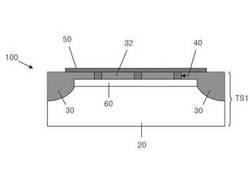

【課題】容量性トランスデューサとその製造及び動作方法を提供する。

【解決手段】第1ドーピング領域20と、該第1ドーピング領域20と反対の型のドーピング領域であり、第1振動部分32を含む第2ドーピング領域30と、該第1ドーピング領域と該第1振動部分32との間に備えられた、空間60と、を備えるトランスデューサ。第1及び第2ドーピング領域20,30は、一体である。第1振動部分は複数の貫通ホール40を含み、振動部分上に貫通ホール40を密封する物質膜50が備えられる。

(もっと読む)

半導体基板とその製造方法および半導体装置

【課題】圧力センサなどのデバイスの製造工程中に空洞内の上下のシリコン面の固着がない半導体基板およびその製造方法を提供する。また、精度良い小型のダイアグラムを有する半導体装置を提供する。

【解決手段】SON構造101のダイアフラム100を有するシリコン基板1およびその製造方法において、SON構造101を構成する空洞2内の下側のシリコン面3に凸状の島4を形成する。半導体基板の表面に深さの異なるホール群を形成し、高温アニール処理することにより一つの大きな空洞を形成する。

(もっと読む)

圧力検出素子の製造方法

【課題】温度変化率の増大を抑制することができる圧力検出素子の製造方法を提供する。

【解決手段】圧力検出素子の製造方法は、以下の工程を備えている。主表面1a側に凹部4を有する第1の基板1に、第1の基板1の凹部4を覆うように主表面1a側に積層された第2の基板2が接合される。積層方向から見て第2の基板2の凹部4と重なる部分に、第2の基板2の歪みを検出するための歪検出素子5が形成される。歪検出素子5に接するように電気配線7が形成される。電気配線7が形成された後に、歪検出素子5の電気配線7と接する箇所が還元されるように水素雰囲気で熱処理される。熱処理の終了時における水素分圧は0.4気圧以下である。

(もっと読む)

寄生容量を低減させたジャイロメータ

【課題】ジャイロメータは、基板と、基板の上に懸架された慣性質量部(2)であって、励振部(6)および検出部(8)を含む慣性質量部(2)と、前記慣性質量部(2)の平面内に含まれる、励振部(6)を少なくとも1つの方向(X)に移動させる手段と、前記質量部の平面の外側での前記検出部(8)の移動を検出する静電容量検出手段とを含む。

【解決手段】前記静電容量検出手段は、前記検出部(8、108)と共に可変コンデンサを形成するように、基板に面して位置する検出部(8)の上に配置された、少なくとも1つの懸架電極(16)を含み、前記電極(16)は、慣性質量部(2)を貫通する少なくとも1つの柱状体(22)によって、前記検出部(8)の上に保持される。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

静電容量型電気機械変換装置

【課題】溶融接合により作製される静電容量型電気機械変換装置において、接合面積などの境界条件が異なる箇所で生じる振動膜の初期変位のバラツキを低減して性能を高めることができる構成を有する装置を提供する。

【解決手段】静電容量型電気機械変換装置は、シリコン基板1と、振動膜7と、シリコン基板1の一方の表面と振動膜7との間に間隙3が形成されるように振動膜7を支持する振動膜支持部17と、で形成されるセル構造102を、少なくとも一つ以上含む素子101を有する。素子101の周囲に、振動膜支持部17と共通の層2に形成された溝103が配されている。

(もっと読む)

貼り合わせ基板及びその製造方法

【課題】中空構造等を作製するためのエッチング工程とガラス基板等他の部材の貼り付け工程を必要としない簡単な工程で、センサー等を作製するための貼り合わせ基板を製造する方法、及び構造強度の問題となる中空構造を形成しなくとも、センサー等の作製に用いることができる多孔質領域を有する貼り合わせ基板を提供する。

【解決手段】ベース基板1の貼り合わせ面に部分的に多孔質領域3を形成する工程と、ボンド基板4の貼り合わせ面に絶縁膜2を形成する工程と、絶縁膜2を介してベース基板1とボンド基板4を貼り合わせる工程と、貼り合わせられたボンド基板4を薄膜化して薄膜層を形成する工程とを有する。

(もっと読む)

センサーを製作するための方法

【課題】サイズが小さく、大量に効果的に生産できる高感度圧力センサを製造するための方法を提供する。

【解決手段】第1のデバイスウエハーをエッチングされた第2のデバイスウエハーに接合して架設された構造を作る、センサー10を製作するための方法が、開示され、その構造のたわみは、第1のデバイスウエハーのデバイス層110に埋め込まれた相互接続部400を通じてセンサー10の外面と電気的に連通する埋め込まれた感知素子310によって決定される。架設された構造は、封鎖物500によって封入される。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

半導体圧力センサ及びその製造方法

【課題】半導体圧力センサの小型化に伴う性能のばらつきを抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体圧力センサの製造方法は、ポリシリコンダイヤフラム6と、その下方の真空室となるべき空間13側に形成されたポリシリコンゲージ抵抗4bと、これらを内包し、犠牲層16と接するエッチング液導入孔15を有する絶縁膜群3,5,7とを含む積層構造を、犠牲層16上に形成する。そして、エッチング液を前記エッチング液導入孔15に通じて、犠牲層16をエッチングすることにより積層構造を真空室上で機能するダイヤフラム体11として形成するとともに、シリコン基板1における第1絶縁膜2の第1開口2a下の表面をエッチングすることにより真空室となるべき空間13と、当該空間13中に配置され、ダイヤフラム体11の中央付近に向かって突出するダイヤフラムストッパー12とを形成する。

(もっと読む)

電子装置、電子機器及び電子装置の製造方法

【課題】空洞内に位置する可動部を品質良く作動できる電子装置を提供する。

【解決手段】基板2上の側壁部23及び第1封止層30に覆われた空洞部33内に位置する可動部7bと、空洞部33内に設置され空洞部33内の気体を吸着する第1ゲッター部34及び第2ゲッター部35と、基板2と対向する場所に位置する第1封止層30及び第2封止層32と、を備え、第1封止層30は第1孔30a及び第2孔30bを有し、第2封止層32は第1孔30a及び第2孔30bを封止する。

(もっと読む)

MEMSトランスデューサの製造方法

【課題】MEMSトランスデューサの製造工程において、アニール処理によって生じる絶縁層の内部応力による基板の反りや破損を、新たに工程を増やすことなく防止する。

【解決手段】第一絶縁層と第一導電層と第二絶縁層と第二導電層とが形成された後に、第一導電層に到達するコンタクトホールを形成するとともに溝部H3を形成するために、第一絶縁層と第二絶縁層とをエッチングした後、第一導電層または第二導電層の応力を緩和するためのアニール処理を施す。

(もっと読む)

薄膜メンブレン構造体及び半導体式薄膜ガスセンサ

【課題】薄膜メンブレン構造体において、ヒータを含むセンサを搭載する際に、薄膜メンブレンの熱絶縁性をさらに向上させながら、薄膜メンブレンの保持性をさらに向上させることである。

【解決手段】薄膜メンブレン構造体10は、薄膜メンブレン20と、薄膜メンブレン20を保持する保持基板30とを備える。保持基板30は、薄膜メンブレン20の上下面のいずれか一方側の面を保持面として保持面の周縁部を保持する周壁部と、薄膜メンブレン20の周縁部の内側である内側部の少なくとも1箇所で薄膜メンブレンの保持面を保持する内側保持部と、周壁部と内側保持部とを接続しながら薄膜メンブレンの保持面との間に空隙31を有する接続部とを含む。

(もっと読む)

2軸加速度センサ

【課題】2方向の加速度を精度よく感知することができ、小型化及び製造コストの低減化を可能とする2軸加速度センサを提供することを目的とする。

【解決手段】本発明は、平板状の錘部、この錘部の側面を囲う枠部、上記錘部の側面と枠部の内面とを連結する1又は複数の梁部、及び上記梁部に付設される歪み感知手段を備える平板状の2軸加速度センサであって、上記梁部の厚さが幅より大きく、上記1又は複数の梁部が、厚さ方向と垂直な直交2方向の正負それぞれの加速度に対する撓みパターンの組合せが異なる少なくとも2つの変形領域を有し、上記歪み感知手段として、上記各変形領域の両端側かつその幅方向両側近傍に二対のピエゾ抵抗素子が配設されていることを特徴とする。

(もっと読む)

変換体モジュールとその製造方法

【課題】矩形の基板上に、変換体と矩形の半導体基板と有し、小型化と低コスト化可能な変換体モジュールを提供する。

【解決手段】矩形の形状を有する基板2と、鋭角の頂点を1つ以上含む多角形の形状を有する変換体3と、矩形の形状を有する半導体基板4とを備え、変換体3は、基板2の第1側辺と変換体3の一つの側辺とが実質的に平行となるように、基板2上に配置され、半導体基板4は、基板2の第1側辺と半導体基板4の1つの側辺とが実質的に平行となるように基板2に配置される。

(もっと読む)

固体撮像装置及びその製造方法並びに電子機器

【課題】固体撮像装置において、MEMS素子を固体撮像装置と同一のチップ上に設けて装置の実装面積を縮小して装置の小型化を実現する。

【解決手段】画素ごとに区分されたフォトダイオードがマトリクス状に配置された受光面を有する固体撮像素子部(R5)を有するデバイス基板10上に、MEMS(Micro Electro Mechanical Systems)素子(16a,16b,17a,17b,DF)を有する構成とする。

(もっと読む)

電気機械変換装置及びその作製方法

【課題】気密性の高い封止構造で密閉空隙を封止して信頼性を向上させた電気機械変換装置及びその作製方法を提供する。

【解決手段】電気機械変換装置は、犠牲層を除去後に封止を行って形成された密閉空隙13を挟んで対向して設けられた電極などの第1の電磁要素12と第2の電磁要素15を有する。封止部は、常温で流動性を持たない第1の封止材16の上に、硬化された常温で流動性を持つ第2の封止材17を重ねることで形成される。

(もっと読む)

半導体圧力センサ

【課題】ダイヤフラムの破壊耐圧を向上させることのできる半導体圧力センサを得ることを目的とする。

【解決手段】厚さ方向の一面に開口する凹部2が形成された第1半導体基板3と、第1半導体基板3の一面と相対して配置される第2半導体基板4と、第1半導体基板3と第2半導体基板4との間に介装され、凹部2と第2半導体基板4との間を連通する貫通穴5が形成された第1酸化シリコン膜6と、を備え、貫通穴5及び凹部2の開口と相対する側から見て、貫通穴5の縁部の少なくとも一部が、凹部2の開口縁部の内側に位置している。

(もっと読む)

半導体加速度センサ

【課題】構造的制限を設けることなく、X、Y、Z軸の検出感度の差を小さくし、且つ、ドリフトが小さく、3軸間の信号出力の変動を低減する半導体加速度センサを提供すること。

【解決手段】本発明によると、半導体基板に、枠部と、錘部と、前記枠部と前記錘部との間に配置される可撓部と、前記可撓部に第1の方向に配置される複数のピエゾ抵抗素子と、前記第1の方向と直交する第2の方向に配置される複数のピエゾ抵抗素子と、前記複数のピエゾ抵抗素子をそれぞれ含む複数のブリッジ回路とを有し、前記ブリッジ回路に電圧を印加する高電位端及び低電位端のうちの何れか一方と、前記ブリッジ回路との間に第1の抵抗体を有する少なくとも1つの前記ブリッジ回路を備えることを特徴とする半導体加速度センサが提供される。

(もっと読む)

1 - 20 / 98

[ Back to top ]