Fターム[4M118FA08]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 受光部の配置 (6,058) | リニア配列 (398)

Fターム[4M118FA08]に分類される特許

61 - 80 / 398

焦点検出装置

【課題】ブルーミングを抑制しながら、広いダイナミックレンジで焦点検出を行う。

【解決手段】AFモジュールの焦点検出部の基板表面に配置されるラインセンサを、複数のフォトダイオードおよびラインセンサ用画素信号読み出し回路によって構成し、余剰電荷を切替制御によって排出するアンチブルーミングゲート(ABG)をフォトダイオードの傍に設ける。そして、アンチブルーミングゲートの閾値電圧Vt、およびフォトダイオードの空乏化電圧VPD0を、最大照度時の発生電荷数Qmaxよりもアンチブルーミングゲート(ABG)を通って排出される流出電荷数LQの方が多く、かつ、最小照度時であって電荷蓄積容量(MEM)の飽和電荷量QMEMSだけフォトダイオードに電荷蓄積された状態で発生する電荷数Qminよりも流出電荷数LQが少なくなるように、規定する。

(もっと読む)

固体撮像素子の製造方法

【課題】工程数を抑えつつ、光の干渉を抑える段差形状を光の入射面に形成することができる固体撮像素子の製造方法を提供すること。

【解決手段】光電変換素子3が形成されたシリコン基板2の表面に層間絶縁膜4を形成し、層間絶縁膜の表面にパッド電極8を形成し、層間絶縁膜とパッド電極を覆う保護膜10を形成し、光電変換素子に対向する位置に形成された第1開口20aとパッド電極に対向する位置に形成された第2開口20bを有するように保護膜の表面にレジスト20をパターニングし、第1開口および第2開口を通して保護膜に対して等方性エッチングを行う。

(もっと読む)

固体撮像素子及びその製造方法と撮像装置

【課題】 簡便な方法で画素の光電変換部の上にある層間絶縁膜の厚さを低減することで、光電変換部として機能する半導体領域への集光効率を向上する固体撮像素子及びその製造方法と撮像装置を提供する。

【解決手段】 ゲート電極パターンと同じ層からなる導電パターンの一部が素子分離膜の上に配置されている固体撮像素子で、前記導電パターンのうち前記素子分離膜の上に配置されている部分の厚さを、前記ゲート絶縁膜の上に配置されている前記ゲート電極層の厚さより薄くすることで、層間絶縁膜の厚さを寄生容量を抑制する膜厚に維持して画素の光電変換部の上にある層間絶縁膜の厚さを低減する。

(もっと読む)

固体撮像装置、撮像装置、AD変換方法

【課題】画素共有の固体撮像装置において、処理時間を短縮できるようにする。

【解決手段】参照信号生成部27、コンパレータ322、計数処理部352による参照信号比較型のAD変換を行なう。その際に、複数の垂直信号線19介して供給される画素信号電圧Vxの何れを処理させるかと、各画素信号電圧VxのP相・D相の何れを処理させるかと、それらの処理順序を制御する。これによって、共有構成でない場合とは異なる信号処理タイミングで信号処理をすることができるようになる。たとえば、各処理対象信号の同じ意味を持つレベル同士の組合せの順でAD変換を行なうように制御することもできる。また、共有単位での加算のAD変換を行なうこともできる。また、共有単位での加算ができない部分については、できる部分とできない部分とに分けて処理することもできる。

(もっと読む)

高感度検出器装置

【課題】検出器装置の感度を向上させることを目的として、落下光を検出器の受光領域上で焦点を結ばせるために、球状の素子を備えたレンズアレイの形態の光偏向素子を用いることが知られている。このようなレンズアレイの製造は、特に製造数が少ない場合、製造コストが高い。新規の光偏向素子を用いることによって、検出器装置の感度の向上を容易に、かつ費用対効果が高い状態で実現する。

【解決手段】本検出器装置は、落下光が検出器の受光領域304上で偏向して角度を変える光入射面305bを有する光偏向素子305を備える。光偏向素子の光入射面305bは互いに傾斜しており、平坦な面として形成されている。本検出器装置は、顕微鏡、特にレーザ走査型顕微鏡において、特に、試料から放出される光を検出するのに適している。

(もっと読む)

選択可能な解像度を有するセンサアレイとその方法

【課題】選択可能な複数の解像度レベルにおいて作動可能なセンサアレイを提供することである。

【解決手段】センサアレイは、複数の画素と第1および第2ビデオラインと複数の中間回路を備え、中間回路はそれぞれ複数の画素におけるそれぞれの画素に電気的に接続され、第1および第2ビデオラインの両方に電気的に接続される。また、センサアレイの解像度を変更する方法において、アレイは第1および第2ビデオライン、複数の画素、および複数の中間回路を含み、方法は、各中間回路をそれぞれの画素および第1および第2ビデオラインに電気的に接続する工程と、第1モードにおいて、信号を1つの画素から複数の中間回路のそれぞれの中間回路を通って第1ビデオラインへ送信する工程と、第2モードにおいて、信号を1つの画素から複数中間回路のそれぞれの中間回路を通って第2ビデオラインに送信する工程を備える。

(もっと読む)

焦点検出装置およびイメージングセンサ

【課題】ラインセンサを搭載した焦点検出装置などのイメージングセンサにおいて、ラインセンサの製造工程を容易にする。

【解決手段】ラインセンサを横方向に沿って並べたラインセンサ群のラインセンサにおけるラインセンサ用画素信号読み出し回路130jに設けられた転送ゲート122A、122B、アンチブルーミングゲート(ABG)121A、121Bの配列方向と、ラインセンサを縦方向に沿って並べたラインセンサ群のラインセンサにおける画素信号読み出し回路の転送ゲート、アンチブルーミングゲートBの配列方向も、同じ方向Mに沿っている。

(もっと読む)

焦点検出装置

【課題】カメラなどに搭載される焦点検出装置において、被写体像の任意のエリアを精度よく焦点検出を行う。

【解決手段】一体型基板によって構成される焦点検出部において、ラインセンサのフォトダイオード対120Aj、120Bjに接続されるラインセンサ用画素信号読み出し回路130jに設けられた転送ゲート122A、122B、アンチブルーミングゲート(ABG)121A、121Bの配列方向と、対応する微小センサ部のモニタセンサ用画素信号読み出し回路144に設けられた転送ゲート152、アンチブルーミングゲート(ABG)151の配列方向を、同じ方向Mに定める。

(もっと読む)

固体撮像装置、撮像システム及び撮像素子の駆動方法

【課題】複数個の固体撮像素子を並べて配置したリニアセンサの読み出しが、簡単な制御で高速に行えるようにする。

【解決手段】複数の固体撮像素子10,20,・・と、各固体撮像素子にパルスを供給するタイミング制御部3とで構成される。各固体撮像素子は、受光部と、転送制御部13,23,・・と、出力回路12,22,・・とを有する。転送制御部は、素子選択用パルスの入力で、信号電荷を転送レジスタから読み出す制御を行うと共に、固体撮像素子の切換えタイミングパルスに同期して素子選択用パルスを遅延させて別の固体撮像素子に出力させる。タイミング制御部は、1つの固体撮像素子の転送制御部に、切換えタイミングパルスの整数倍の周期に対応した時間をあけて、素子選択用パルスを少なくとも2回出力させて、2系統以上の同時出力が行えるようにする。

(もっと読む)

電子装置、画像形成装置、および画像入力装置

【課題】導通信頼性の高い電子装置、およびそれを用いた、画像形成装置並びに画像入力装置を提供する。

【解決手段】電子装置は、基板102と、基板102の一表面上に形成された電子素子103と、電子素子103が形成された領域とは異なる領域に、所定間隔をあけて列状に配列され、第一の接続配線104を介して電子素子103と電気的に接続された、第一のパッド106と、電子素子103が形成された領域および第一のパッド106が形成された領域とは異なる領域に設けられ、第一のパッド106間を横切る第二の接続配線105を介して電子素子103と電気的に接続された、第二のパッド107と、を具備しており、第一のパッド106間において、第二の接続配線105の基板102とは反対側の表面が、第一のパッド106の基板102とは反対側の表面よりも基板102側に位置している。

(もっと読む)

イメージセンサおよび画像読取装置

【課題】イメージセンサの電荷の転送効率を改善することを目的とする。

【解決手段】光を透過する読出電極321、322、323のそれぞれに、あらかじめ決められた電荷が印加されると、画素310に蓄積された電荷がCCD素子331,332に転送される。読出電極321、322に対して、読み出しポテンシャルを画素ポテンシャルウェルの底のポテンシャルより低く、かつCCDポテンシャルウェルの底のポテンシャルより高くする電圧値をもつ電圧VHを印加し、読出電極323に対して、画素ポテンシャルウェルの底のポテンシャルより高いポテンシャルを形成する電圧値を持った電圧VLを印加することで、高低差があり、移動距離も短いポテンシャル勾配が形成される。

(もっと読む)

AD変換装置、固体撮像装置および電子情報機器

【課題】グレイコードカウンタの面積占有率の増大および、グレイコードカウンタで消費する電力の増大を抑える。

【解決手段】ランプ波形信号生成回路61からの参照信号としてのランプ波形信号61aと列毎のアナログ画素信号とをそれぞれ比較して両者が一致したときに、対応するデジタル画素値Dpvを出力するAD変換手段4において、最上位ビットから最下位より2番目のビットまでをnビットカウンタ62であるグレイコードカウンタのカウント値とし、最下位ビットは、基準クロックCKまたはその反転クロックCKBから生成されるグレイコードカウンタの最下位ビットとしてグレイコードを使用することにより、1ビット分だけAD変換の分解能を拡大することができる。

(もっと読む)

画像読取装置及びその制御方法

【課題】コストの増加を抑制しつつ色ずれを減少させる。

【解決手段】画像読取装置は、それぞれ発光スペクトラム特性が異なる光を原稿に対して順次照射する複数の光源と、第1の方向にアレイ状に配置され、該第1の方向に対してほぼ直交した第2の方向に対する感度特性を変更可能な受光素子と、前記複数の光源における照射すべき光源の切り替えに同期してそれぞれの前記受光素子の感度特性を変更する感度特性変更部とを備えている。

(もっと読む)

画像読取装置およびイメージセンサチップ

【課題】イメージセンサチップを長手方向に複数配列してなる1ラインのラインセンサにおいて、イメージセンサチップ間の光電変換素子の存在しない隙間部分に相当する欠損画素を補間する。

【解決手段】イメージセンサチップ1121の回路基板30の主走査方向における一方の端部に突出部31が形成され、回路基板30の主走査方向におけるもう一方の端部の、上記突出部31に対応する位置には後退部32が形成されており、イメージセンサチップ1121が主走査方向に複数直線状に並べられたときに、隣り合うイメージセンサチップ1121の突出部31と後退部32とは互いに嵌まり合う。当該突出部31上において、光電変換素子列40から副走査方向に所定距離離れた位置には、イメージセンサチップの繋ぎ目部分における画素欠陥領域の画素を補間するための補間用光電変換素子50が設けられている。

(もっと読む)

受発光素子及びその製造方法、並びに受発光素子を備えた光センサ装置

【課題】 ノイズの混入を抑制することができる受発光素子及びその製造方法、並びにその受発光素子を備える光センサ装置を提供する。

【解決手段】 本発明に係る受発光素子1は、半導体基板3と、半導体基板3の一方の主面3aに設けられた発光ダイオード5と、半導体基板3の前記一方の主面3aに、発光ダイオード5と離間して設けられたフォトダイオード7と、を備えている。半導体基板3の一方の主面3aにおいて発光ダイオード5とフォトダイオード7との間の位置には溝19が形成されている。フォトダイオード7は、半導体基板3の一方の主面3aにP型不純物を拡散して形成されたP型半導体領域7pと、P型半導体領域7pと離間して配置され、半導体基板3の前記一方の主面3aにN型不純物を拡散して形成されたN型半導体領域7nとを有している。P型半導体領域7p及びN型半導体領域7nの不純物濃度は、半導体基板3の不純物濃度より高くなっている。

(もっと読む)

受光デバイス及びその制御方法

【課題】外光による画素蓄積領域の飽和を防止し信号光のみ分離抽出できるようにすることで、信号光に対するダイナミックレンジを向上させる受光デバイス及びその制御方法を提供し、特殊プロセスを用いず安価で構造が単純な受光デバイスを提供する。

【解決手段】ウェル領域203の表面に電子保持領域204を有し、電子保持領域204に2つの独立した等価な第1、第2正孔保持領域205、206を備える。第1、第2正孔保持領域205、206上に絶縁層215を介して第1、第2制御電極207、208を有し、光に応じてウェル領域203に発生した電子正孔対を、第1、第2制御電極207、208の電圧操作によって、電子保持領域204及び第1、第2正孔保持領域205、206に電子及び正孔を分離し保持させる。第1、第2制御電極207、208に印加する電圧を反転させて電子と正孔を再結合し、残存する電子を信号光の受光出力として取り出す。

(もっと読む)

固体撮像素子、撮像装置

【課題】固体撮像素子のチップの大きさを低減することができ、かつ、信号電荷の転送を良好に行うことができる固体撮像素子を提供する。

【解決手段】光電変換が行われる受光部と、半導体基体11に形成された水平転送レジスタ4と、半導体層によって形成された水平転送電極14と、水平転送電極14の水平転送レジスタ4上の部分に電気的に接続され、金属層によって形成されたバスライン16,17と、水平転送電極14とバスライン16,17とを接続するコンタクト部15において、水平転送電極14とバスライン16,17との界面付近に形成され、水平転送電極14の半導体層の仕事関数及びバスライン16,17の金属層の仕事関数の間の大きさの仕事関数を有する、バリアメタル層21とを含む固体撮像素子を構成する。

(もっと読む)

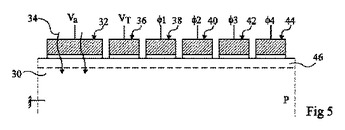

非常に低い光レベルでの画像化のための画像センサ

【解決手段】本発明は、画像センサのための基本装置に関しており、基本装置は、基準電圧でバイアスされ得る第1の導電型の半導体基板(30)の表面に形成された電荷光発生蓄積領域を備えており、電荷光発生蓄積領域は、電荷の転送(36)、増加(38,40,42)及び絶縁(44)のためのデバイスに関連付けられている。電荷光発生蓄積領域の上に、第1の電圧及び第2の電圧で交互にバイアスされるように適合された絶縁されたゲート(32)が取り付けられており、絶縁されたゲートは低吸収材料から形成されている。  (もっと読む)

(もっと読む)

半導体撮像装置

【課題】転送クロック間の位相ずれに応じて出力信号波形に歪が生じてしまうこと。

【解決手段】ラインセンサ100は、第1導電型のウェル領域12が形成された第2導電型の半導体基板10と、入射光に応じた電荷を生成する複数の画素20aがウェル領域12に形成された画素列20と、転送クロックに応じて電荷を転送する転送電極がウェル領域12上に配置されたCCDレジスタ部22と、転送電極によって転送された電荷に応じた電圧信号を出力する出力回路と、ウェル領域12及び出力回路に対して基準電位を供給する配線部(電極パッド36、37、接続配線25)と、ウェル領域12と配線部間の第1コンタクトを、出力回路と配線部間の第2コンタクトに対して接続する配線に含まれる抵抗領域52と、を備える。抵抗領域52は、ウェル領域12に対する不純物拡散により形成される。

(もっと読む)

イメージセンサおよびイメージセンサモジュール

【課題】センサチップからSTパルスの入力端子を削減できる密着イメージセンサを提供すること。

【解決手段】パルス入出力回路7は、当該センサチップの外部から時系列パルス6として入力されるライン同期パルス(STパルス)と出力開始タイミングパルス(TOUTパルス)とを識別し、識別したSTパルス11は当該センサチップの内部に入力するとともに外部へ出力し、識別したTOUTパルス12は当該センサチップの内部に入力し、前記外部へ出力したSTパルスに後続するパルスとして、当該センサチップの内部から出力されるTOUTパルス13を当該センサチップの外部へ出力する。外部には時系列パルス14が出力される。

(もっと読む)

61 - 80 / 398

[ Back to top ]