Fターム[4M119BB01]の内容

MRAM・スピンメモリ技術 (17,699) | 記憶素子の種類 (1,713) | TMR素子 (1,199)

Fターム[4M119BB01]に分類される特許

1,181 - 1,199 / 1,199

磁気セルを超高速制御するための方法及び装置

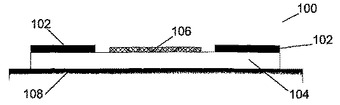

磁気素子の磁化を超高速で制御するための装置とその方法であって、装置(100)は表面弾性波発生手段(102)と、典型的には機能的及び部分的に構造的に前記SAW発生手段(102)内に設けられたトランスポートレイヤー(104)と、少なくとも1つの強磁性素子(106)とを備える。表面弾性波は発生された後、典型的には圧電材料より成るトランスポートレイヤー(104)内を伝播する。これにより、歪みがトランスポートレイヤー(104)及びトランスポートレイヤー(104)と接触した強磁性素子(106)内に発生する。この歪みは磁気弾性結合により強磁性素子(106)内に有効磁界を発生する。表面弾性波が強磁性共振(FMR)周波数に実質近い周波数を有する場合は、強磁性素子(106)は充分に吸収され、素子の磁化状態はFMR周波数で制御される。装置はRF磁気共振器、センサ、カメラ等に使用される。対応する方法は磁気要素及び磁気論理素子における超高速の読み出し及び切り換えに利用される。

(もっと読む)

(もっと読む)

他の種類の回路と共に集積されたMRAM装置

磁気抵抗ランダムアクセスメモリ(MRAM)(13)が、他の回路種(12)と共に埋め込まれている。演算装置のようなロジック(12)が、MRAM(13)と共に埋め込むのに特に適した回路種である。埋め込みを効率的に行うには、金属層(26)を他の回路(12)の相互接続部の一部として用い、更にMRAMセル(13)の一部として用いる。MRAMセル(13)は全て、プログラム線によって書き込まれる。プログラム線は、2本の線であり、交差して書き込むセルを規定する。このように、金属線(26)の共通使用があり、MRAMのプログラム線の一方に用いられ、更にロジック(12)の相互接続線の一方に用いられるので、設計が簡略化される。  (もっと読む)

(もっと読む)

磁気抵抗記憶素子の誤ったプログラミングを防止する方法および装置

本発明は、磁気抵抗記憶素子の近くで外部磁界を測定する磁界センサユニットと、測定された外部磁界が閾値を超えるときにプログラミング動作を一時的に禁止する手段とを備える磁気抵抗記憶素子のアレイを提供する。対応する方法がさらに提供される。  (もっと読む)

(もっと読む)

磁気メモリ用のデータ保持インジケータ

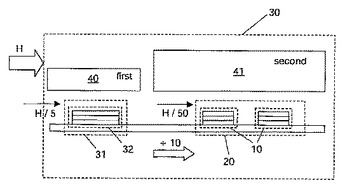

本発明は、少なくとも1つのデータ保持インジケータデバイス(50)が設けられた磁気抵抗メモリ素子(10)のアレイ(20)を提供する。少なくとも1つのデータ保持インジケータデバイス(50)は、それぞれプリセットされた磁化方向を有する第1の磁気素子(51)と、第2の磁気素子(52)とを備え、第1および第2の磁気素子(51,52)のプリセットされた磁化方向は、互いに異なっている。第1および第2の磁気素子(51,52)は、これらの磁化方向を、検出しきい値を超える外部から印加された磁界の磁界線と向きを揃えるのに適している。本発明によれば、少なくとも1つのデータ保持インジケータデバイス(50)のパラメータが、検出されるべき外部から印加された磁界の検出しきい値を設定するように選択される。少なくとも1つのデータ保持インジケータデバイス(50)は、アレイ(20)の磁気抵抗メモリ素子(10)の前記外部から印加された磁界への暴露を示す状態または出力を有する。  (もっと読む)

(もっと読む)

磁気メモリ用途のための応力支援による電流駆動式スイッチング

磁気メモリを提供するための方法及びシステム。本方法及びシステムは、複数の磁気素子を設けること、少なくとも1つの応力支援層を設けること、を含む。複数の磁気素子の各々は、スピン転移を用いて書き込まれるように構成されている。少なくとも1つの応力支援層は、書き込み時、複数の磁気素子の少なくとも1つの磁気素子に少なくとも1つの応力を及ぼすように構成されている。書き込み時、応力支援層によって磁気素子に及ぼされる応力により、スピン転移スイッチング電流が低減される。スイッチング電流が一旦オフになると、2つの磁化状態間のエネルギ障壁が変化しないことから、熱変動に対する磁気メモリの安定性が損なわれることはない。  (もっと読む)

(もっと読む)

磁界センサを有するMRAMチップの不均一シールド

本発明は、磁気抵抗メモリ素子のアレイと少なくとも一つの磁界センサ素子とを備える磁気抵抗メモリデバイスであって、前記磁気抵抗メモリ素子の前記アレイを、少なくとも一つの前記磁界センサ素子とは異なるように外部磁界からシールドするための部分シールド手段又は不均一シールド手段を備える磁気抵抗メモリデバイスを提供する。「異なるように」とは、5%の最小シールド差、好ましくは10%の最小シールド差が存在することを意味している。また、本発明は対応するシールド方法も提供する。  (もっと読む)

(もっと読む)

磁気抵抗メモリデバイスの書き込みの間の活性フィールド補償を実行するためのデバイス及び方法

本発明は、磁気抵抗メモリ素子(10)のアレイ(20)を提供する。アレイ(20)は、選択磁気抵抗メモリ素子(10)において書き込み磁場を生成するための電流又は電圧をもたらすための手段と、選択磁気抵抗メモリ素子(10)の近くにおける外部磁場を測定するための磁場センサユニット(50)と、書き込み動作の間に、測定された外部磁場を局部的に補償するための電流又は電圧を調整するための手段(52)とを有する。本発明は、対応する方法も提供する。

(もっと読む)

(もっと読む)

加工物上にニッケル鉄を無電解析出させるための組成物及びその析出方法

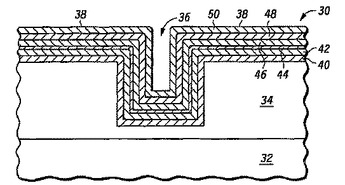

加工物30上にニッケル鉄を無電解析出させる方法及びその組成物を提供する。加工物30上にニッケル鉄を無電解析出させる際に用いられる析出液は、ニッケルイオン源、第一鉄源、錯化剤、還元剤及びpH調節剤を含む。その析出液は、アルカリ金属イオンを実質的には含まない。磁気エレクトロニクス装置で使用されるフラックス集中システムの作製方法は、加工物30を提供するステップと、加工物30上に絶縁材料層34を形成するステップとによって開始される。溝36が絶縁層34に形成され、バリア層40が溝内に析出される。ニッケル鉄クラッド層46がバリア層40上に析出される。ニッケル鉄クラッド層の析出後、溝付近の絶縁材料層34は、原子約1×1011個/cm2未満のアルカリ金属イオン濃度を有する。  (もっと読む)

(もっと読む)

ナノコンタクト磁気メモリデバイス

磁気メモリデバイスは、基板上に形成された複数のトランジスタ316、317と、トランジスタ上に形成された、多数の有効磁気抵抗素子318、319、強磁性記録層321、非磁性空間層323及び自由磁気読出し層322を含む共通磁気メモリブロック312とを備える。延長共通デジタル線315は共通磁気メモリブロック上に配置される。共通磁気メモリブロックは、それぞれの活性領域の各コンタクトを通してトランジスタの対応のソース/ドレイン電極と電気的に接続される。活性領域の強磁性記録層の特定の磁化状態は、加熱プロセスを実行し、かつ共通デジタル線及びビット線309、311又はワード線307から誘導される外部磁界を印加することにより変化させ得る。有効磁気抵抗素子の抵抗変化は、読出し中に磁気反応層の磁化状態を変化させることにより検出でき、小さいスイッチング磁界が必要である。 (もっと読む)

磁気メモリデバイス

磁気メモリデバイス(300)のメモリセル(310)は、自由層(311)と、キャップ層と、反強磁性層と、非磁気空間層を介して反強磁性結合された2つ以上の強磁性層を備える合成反強磁性層とを含む。該合成反強磁性層は反強磁性層によってピン止めされる。該反強磁性層および該合成反強磁性層は合成反強磁性ピン(SAFP)記録層を形成する。該SAFP記録層の磁化は、加熱プロセスと、ビットライン(320)およびワードライン(330)に沿って流れる電流から誘導された外部電界とを組み合わせることによって変更可能である。従って、該SAFP記録層の高い容積および異方性エネルギーゆえに、該SAFP記録層を導入した後に、高密度で、熱的安定性が高く、電力損失が少なく、かつ熱耐性が高いMRAMが達成可能である。 (もっと読む)

磁気トンネル接合装置およびその装置に対する書込み/読出し方法

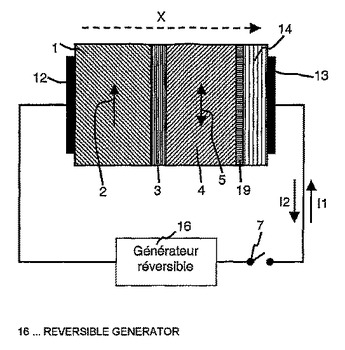

本発明の装置は、第1の電極(12)と、磁性基準層(1)と、トンネルバリア(3)と、磁性記憶層(4)と、第2の電極(13)とを連続的に備えている。記憶層(4)と第2の電極(13)との間には少なくとも1つの第1の断熱層が配置され、この第1の断熱層は、その熱伝導率が5W/m/℃未満である材料から形成されている。第1の電極(12)と基準層(1)との間に配置された層によって第2の断熱層を構成することができる。書込み段階は、記憶層(4)のトンネル接合部を通じて基準層(1)へと向かう電流(l1)の循環を含んでおり、一方、読出し段階は逆方向の電流循環を含んでいる。  (もっと読む)

(もっと読む)

磁界を形成する導体

本発明は、電流が電気導体を流れるときに回路構成の少なくともさらにもう1つの部分に作用する磁界を生成する少なくとも1つの電気導体(40)を有する集積回路構成を提供している。電気導体(40)は、この回路構成のこの少なくともさらにもう1つの部分に向かって方向付けられた第1の側を有し、導電材料の主要線(41)と、その第1の側に接続され、磁性材料から成る少なくとも1つの磁界形成ストリップ(42)を備える。磁界形成ストリップ(42)により、電気導体(40)上の磁界プロファイルの不均一性が、低下される。  (もっと読む)

(もっと読む)

電流によって誘起されたスピンモーメント移行をベースとした高速かつ低電力の磁気デバイス

本発明は、一般に、不揮発性メモリとして機能し得るようなメモリセルのための磁気的な分野に関するものである。より詳細には、本発明は、スピン分極電流を使用することによってメモリデバイス内の磁気領域の磁化方向を制御してスイッチングし得るような、高速でありかつ低消費電力の方法を開示している。磁気デバイスは、固定磁化方向を有したピン止めされた磁化層と;自由な磁化方向を有した自由磁化層と;固定磁化方向を有した読出磁化層と;を具備している。ピン止めされた磁化層と自由磁化層とは、非磁性層によって分離されており、自由磁化層と読出磁化層とは、他の磁性層によって分離されている。ピン止めされた磁化層の磁化方向と自由磁化層の磁化方向とは、一般に、同じ向きとはされない。非磁性層は、磁化層どうしの間の磁気的相互作用を最小化する。  (もっと読む)

(もっと読む)

スピン転移スイッチングを利用し且つ複数のビットを記憶する磁気メモリ素子

複数のビットを記憶可能な磁気素子を提供するための方法及びシステムを開示する。本方法及びシステムには、第1固定層、第1非磁性層、第1自由層、接続層、第2固定層、第2非磁性層及び第2自由層を設ける段階が含まれる。第1固定層は、強磁性体であり、第1方向に固定された第1固定層磁化を有する。第1非磁性層は、第1固定層と第1自由層との間にある。第1自由層は、強磁性体であり、第1自由層磁化を有する。第2固定層は、強磁性体であり、第2方向に固定された第2固定層磁化を有する。接続層は、第2固定層と第1自由層との間にある。第2非磁性層は、第2固定層と第2自由層との間にある。第2自由層は、強磁性体であり、第2自由層磁化を有する。磁気素子は、書き込み電流が磁気素子を通過する際のスピン転移により第1自由層磁化及び第2自由層磁化が方向を変更可能となるように構成される。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

複合磁気フリー層を有する磁気エレクトロニクス情報デバイス

磁気エレクトロニクス情報デバイス(12)は、2つの多層構造(24,26)及び該2つの多層構造の間に配置されたスペーサ層(28)を備えている。各多層構造は、2つの磁気副層(38,40及び44,46)と、該2つの磁気副層の間に配置されたスペーサ層(42,48)とを有している。2つの磁気副層の間に配置されたスペーサ層は、飽和領域によって定量化される反強磁性交換結合を提供する。2つの多層構造の間に配置されたスペーサ層は、前記第1飽和領域よりも小さい他の飽和領域によって定量化される第2反強磁性交換結合を提供する。  (もっと読む)

(もっと読む)

MRAMセルのための磁気異方性を誘導するための斜め堆積

表面を有する基板を提供するステップと、前記基板上に合成磁気モーメントベクトルを有する第1磁気領域(17)を堆積するステップと、前記第1磁気領域上に電気絶縁材料(16)を堆積するステップと、前記電気絶縁材料上に第2磁気領域(115)を堆積するステップを備えた磁気抵抗トンネル接合セルを製造する方法であって、前記第1磁気領域および第2磁気領域の一方の少なくとも一部分が、前記基板の表面に直交する方向に対して非ゼロの堆積角で該領域を堆積することによって形成されて誘導異方性を作る方法。  (もっと読む)

(もっと読む)

レーザ移動を用いて感熱基板上に移植した磁気ランダム・アクセス・メモリ(MRAM)デバイスおよびこれを製造する方法

【課題】 ポリマおよびプラスチック等の低温基板上に磁気メモリ・デバイスを製造する方法を提供する。

【解決手段】 低温基板上に磁気メモリ・デバイス(およびその結果として生じる構造)を形成する方法は、メモリ・デバイスを、分解可能な材料層で被覆された透明基板上に形成し、所定の高圧を生成させる急速加熱を施すステップと、メモリ・デバイスを低温基板に移動するステップと、を含む。

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1,181 - 1,199 / 1,199

[ Back to top ]