Fターム[5B005UU32]の内容

階層構造のメモリシステム (9,317) | メモリの構成 (535) | 多階層のメモリ構成 (167) | セカンドキャッシュ (142)

Fターム[5B005UU32]に分類される特許

81 - 100 / 142

マイクロプロセッサとレベル4キャッシュとを有するパッケージ

マイクロプロセッサを有するダイとレベル4キャッシュを有するダイとの間に設けられる集積回路を有するパッケージを備えた方法、装置及びシステム。  (もっと読む)

(もっと読む)

キャッシュシステム

【課題】 本発明は、実現が容易なノン・インクルーシブ方式のキャッシュシステムを提供することを目的とする。

【解決手段】 キャッシュシステムは、主記憶装置にアクセスするよう機能する処理装置と、処理装置に結合され主記憶装置よりも高速にアクセス可能な1次キャッシュと、1次キャッシュを介して処理装置に結合され主記憶装置よりも高速にアクセス可能な2次キャッシュを含み、1次キャッシュと2次キャッシュは、処理装置からのアクセスに応じて主記憶装置から第1のデータを読み出す際に1次キャッシュと2次キャッシュとの両方に第1のデータを登録し、処理装置からのアクセスに応じて2次キャッシュの第2のデータを無効化する必要が生じた際に1次キャッシュに存在する第2のデータを無効化することなく2次キャッシュの第2のデータを無効化する動作を実行するよう構成される。

(もっと読む)

少なくとも2つの処理ユニットと、及び少なくとも1つのメモリとを有する計算機システム内に形成される及び記憶装置、及びそれによる記憶方法

【課題】記憶装置、及び記憶方法を提供すること。

【解決手段】少なくとも2つの処理ユニットとデータ及び/又は指令のための少なくとも1つの第1のメモリ又はメモリ領域とを有する計算機システム内でデータ及び/又は指令を記憶する装置及び方法は、装置内に第2のメモリ又はメモリ領域が含まれており、その場合に装置がキャッシュメモリシステムとして形成されており、かつ少なくとも2つの分離されたポートを搭載しており、これらのポートを介して第2のメモリ又はメモリ領域の同一又は異なるメモリセルへの少なくとも2つの処理ユニットのアクセスが行われ、その場合に第1のメモリシステムからデータ及び/又は指令がブロック単位で一時記憶されることを特徴としている。

(もっと読む)

少なくとも2つの実行ユニットを有する計算機システムにおけるメモリアクセスを制御する方法および装置

【解決手段】少なくとも2つの実行ユニットを有する計算機システムにおけるメモリアクセスを制御する方法であって、実行ユニット当たりバッファメモリ領域、特にキャッシュメモリ領域が設けられており、さらに切替え手段と比較手段が設けられており、その場合にパフォーマンスモードと比較モードの間で切り替えられる、メモリアクセスを制御する方法において、パフォーマンスモードにおいて、各実行ユニットがそれぞれ対応づけられたバッファメモリ領域へアクセスし、比較モードにおいては2つの実行ユニットが予め定めることのできるバッファメモリ領域へアクセスし、その場合にバッファメモリ領域が構成可能であることを特徴とする、少なくとも2つの実行ユニットを有する計算機システムにおけるメモリアクセスを制御する方法が提供される。 (もっと読む)

クリティカルセクションをトランザクション的に実行することによるロックの回避

クリティカルセクションをトランザクション的に実行することでロックを回避するシステムは、以下のようにプログラムを修正する。(1)クリティカルセクションのトランザクション的実行中に、プログラムはまずクリティカルセクションに関連するロックが別の処理によって保持されているか否かを決定し、保持されている場合にはトランザクション的実行を打ち切る。(2)トランザクション的実行が別の処理からの干渉的データアクセスに遭遇することなく完了する場合には、プログラムはトランザクション的実行中に作成された変更をコミットし、クリティカルセクションの後のプログラムの通常の非トランザクション的実行を任意で再開する。(3)トランザクション的実行中に別の処理からの干渉的データアクセスに遭遇する場合には、プログラムはトランザクション的実行中に作成された変更を破棄し、クリティカルセクションの再実行を試みる。  (もっと読む)

(もっと読む)

キャッシュメモリの運用方法

【課題】キャッシュミスを低減し、かつメモリシステムの高性能化を図る。

【解決手段】中央制御部40が参照する下位メモリ素子48に記憶された大量の情報から取り出される第1情報が格納される第1補助記憶素子42、及び第1情報が含まれる第2情報が格納される第2補助記憶素子44を用意する。参照される情報が、第1補助記憶素子42または第2補助記憶素子44に存在するか、あるいは、参照される情報を含んでいない別の第1情報が第1補助記憶素子42に存在するか否かによって、前記下位メモリ素子48から第1情報または第2情報を選択的に取り出し、第1補助記憶素子42と第2補助記憶素子44とに選択的に格納する。

(もっと読む)

命令の型に応じて構成可能なキャッシュ・システム

プロセッサ(51)は、フェッチされたそれぞれの命令について命令の型を判定するデコード論理演算回路(54)、第1のレベルのキャッシュ(L1)、第1のレベルのキャッシュに結合された第2のレベルのキャッシュ(L2)、ならびに第1および第2のレベルのキャッシュに動作するように結合された制御論理演算回路を備える。制御論理演算回路は、好ましくは、第1の型の命令についてキャッシュ・ミスがあった場合にキャッシュ・ラインフィルが第1のレベルのキャッシュに対し実行されるようにするが、第2の型の命令については第1のレベルのキャッシュに対しラインフィルが実行されるのを禁止する。  (もっと読む)

(もっと読む)

ロジカルパーティショニングされた処理環境におけるリソース管理のための方法および装置

【課題】プロセシングシステムのロジカルパーティショニングの態様を、リソースの使用に関してリソース管理に結びつける。

【解決手段】マルチプロセシングシステム100のそれぞれのプロセッサ102を、複数のリソースグループへ論理的に区分けし、所定のアルゴリズムによる関数として、リソースグループ間のリソースを時間割り当てする方法および装置を提供する。リソースは、(i)プロセッサ102と入出力デバイス110との間の通信バンド幅の割り当て分、(ii)プロセッサ102によって使用される共有メモリ106内のスペースの割り当て分、および(iii)プロセッサ102によって使用されるキャッシュメモリラインのセット、のうち少なくとも一つを含む。

(もっと読む)

キャッシュライン境界を横切る命令におけるキャッシュミスの処理

プロセッサーのフェッチセクションは命令を取得するための命令キャッシュといくつかのステージのパイプラインを備える。命令は、キャッシュライン境界を横切ってもよい。パイプラインステージは2つのアドレスを処理し完全な境界を横切る命令を回復する。そのような処理の期間に、命令の第2の部分がキャッシュに存在しないなら、第1のラインに関するフェッチは無効とされ再循環される。この第1のパスに対して、そのデータのいずれかをプロセッサーの後段のステージに渡すことなく、命令の第2の部分のためのアドレスの処理は、より高いレベルのメモリからキャッシュに命令データをロードするためのプリフェッチ要求として取扱われる。第1のラインアドレスが再びフェッチステージを通過すると、第2のラインアドレスが通常の順番で続き、命令の両方の部分は、キャッシュからフェッチすることができ、通常の方法で結合することができる。  (もっと読む)

(もっと読む)

コンピュータシステム、及びメモリの不良救済方法

【課題】 メモリモジュールに搭載されたメモリの不良救済をコンピュータシステム上で実行する。

【解決手段】 コンピュータシステム1は、CPU2と、不良救済が可能であるように構成されたメモリ11が搭載されたメモリモジュール3とを備えている。CPU2は、二次キャッシュ2bを備えている。メモリ11の不良救済の実行が指示されると、救済プログラム15がCPU2の二次キャッシュ2bにロードされる。CPU2は、二次キャッシュ2bにロードされた救済プログラム15を実行して、メモリ11の不良救済を行う。

(もっと読む)

タグ付きキャッシュ状態に基づいて下位レベル・キャッシュへの参照なしに相互接続ファブリック上にリクエストを送出するためのデータ処理システム、キャッシュ・システム、および方法

【課題】キャッシュ・コヒーレント・データ処理システムの提供。

【解決手段】メモリ・アクセス・リクエストをマスタが受けると、キャッシュ階層の上位レベル・キャッシュの第1キャッシュ・ディレクトリをアクセスする。ターゲット・アドレスが有効アドレス・タグおよび第1無効コヒーレンシ状態を有するエントリと関連付けられていることに対応して、即座に相互接続ファブリック上にターゲット・アドレスを指定するリクエストを送出する。ターゲット・アドレスが第一キャッシュディレクトリにおいて第2無効コヒーレンシ状態を有するエントリと関連付けられていることに応答して、キャッシュ・コヒーレンシの下位レベル・キャッシュの第2キャッシュ・ディレクトリにおいてターゲット・アドレスと関連付けられたコヒーレンシ状態を決定した後、相互接続ファブリック上にターゲット・アドレスを指定するリクエストを送出する。

(もっと読む)

自己訂正コンピュータ

フォールトトレラント又は自己訂正式のコンピュータシステムが開示されている。このコンピュータシステムには、例えば宇宙放射線によって生じ得る障害に対する保護の種々のセットが設けられている。システムのより一層の信頼性は、誤りが検出されるのを待つのではなく、コンポーネントを定期的なスケジュールでスクラビングすることによって実現することができる。したがって、長期間にわたって検出されないままの誤りが広がって、さらにシステムを損傷させることがない。3つ又はそれより多くのプロセッサがパラレルに動作するように設けられ、これらのプロセッサからの信号を受信するようにコントローラが設けられ、投票論理を使用して多数決信号値を決定する。このようにしてコントローラは、プロセッサの1つからの信号が多数決信号と異なる場合に、誤りを検出することができる。このシステムにはまた、所定のマイルストンに到達した後にプロセッサを再同期化するためのスクラビングモジュールも設けられている。このマイルストンは所定の時間間隔又はユーザが定義する任意のイベントでよい。 (もっと読む)

画像形成装置

【課題】 文字、グラフィック、イメージなどの複数のオブジェクトで構成される電子文書の画像形成をソフトウェアで高速に形成することが出来るようになり、画像の表示や印刷などを高速に行うことが可能な画像形成装置の提供。

【解決手段】 CPUがアクセス可能な記憶手段と、前記記憶手段の動作設定をする設定手段と、画像データを入力する入力手段と、前記入力手段に入力された画像データに基づいて画像を形成する画像形成手段と、前記入力手段に入力された画像データを解析する解析手段とを有し、前記画像形成手段は、前記設定手段が前記解析手段の解析結果に基づいて前記動作設定をした後に画像を形成することを特徴とする画像形成装置。

(もっと読む)

ストリーム・レジスタを用いてスヌープ要求をフィルタする方法、装置及びコンピュータ・プログラム

【課題】キャッシュ・コヒーレントな多重プロセッサ・システムにおいて、共用バスを使う低効率のスヌープ要求システムに替わる効率の良い簡単なスヌープ方法及び装置を提供する。

【解決手段】複数のプロセッシング・ユニットを有するマルチプロセッサ・コンピューティング環境においてキャッシュ・コヒーレンシをサポートするための方法及び装置であって、各プロセッシング・ユニットは、それに付随するするローカル・キャッシュ・メモリを有する。スヌープ・フィルタ・デバイスは、各々の処理ユニットに関連付けられており、ストリーム・レジスタ・セット及び関連するストリーム・レジスタ対比ロジックの使用に基づいてフィルタリング方法を実行する少なくとも一つのスヌープ・フィルタ基本要素を含む。どの時点においても、複数のストリーム・レジスタ・セットのうち、少なくとも一つのストリーム・レジスタ・セットはアクチブであり、少なくとも一つのストリーム・セットは履歴と標識される。さらに、スヌープ・フィルタ・ブロックは、キャッシュ・ラップ検知ロジックと動作可能に結合され、これにより、キャッシュ・ラップ状態が検知されると、アクチブなストリーム・レジスタ・セットの内容は履歴ストリーム・レジスタ・セットに移し替えられ、少なくとも一つのアクチブなストリーム・レジスタ・セットの内容がリセットされる。各フィルタ基本要素は、ストリーム・レジスタ対比ロジックを実行し、受信したスヌープ要求をプロセッサに転送するかあるいは廃棄するかを判断する。

(もっと読む)

半導体集積回路

【課題】 キャッシュメモリ回路におけるリフィルに伴う読み込み動作、及び、ライトバック又はライトスルーに伴う書き込み動作によるペナルティーを抑えてシステム性能を向上させた半導体集積回路を提供する。

【解決手段】 この半導体集積回路は、第1のバスラインに接続されたプロセッサ部10と、第2のバスラインに接続され、プログラム及びデータを格納する主メモリ回路70と、第1のバスラインに接続され、プロセッサ部において用いられるデータの一部が書き込まれると共に、書き込まれたデータヘのアクセスが優先的に行われる第1のキャッシュメモリ回路20と、第1のバスラインに接続され、第1のキャッシュメモリ回路の記憶容量が不足した際に第1のキャシュメモリ回路にデータを上書きされることにより消去されるデータ及び第1のキャッシュメモリ回路から主メモリ回路に書き戻すデータが一時的に書き込まれると共に、書き込まれたデータへのアクセスが可能な第2のキャッシュメモリ回路30とを具備する。

(もっと読む)

マルチスレッドのコンピュータ処理を提供する装置および方法

簡潔に述べると、本発明の実施例に従うと、マルチスレッドされたコンピュータ処理を提供する装置および方法が提供される。本装置は、マルチバンク・キャッシュ・メモリ、命令プリデコード・ユニット、乗加算ユニット、コプロセッサおよび/または変換索引バッファ(TLB)を共有するために適合した第1および第2演算処理ユニットを含む。本方法は、少なくとも2つのトランザクション開始者間でマルチバンク・キャッシュ・メモリの共有使用を含む。  (もっと読む)

(もっと読む)

キャッシュメモリ及びプロセッサ

【課題】プロセッサ間でデータのコヒーレンシーを動作効率よく保つことができるキャッシュメモリ及びこのキャッシュメモリを備えたプロセッサを提供する。

【解決手段】複数のプロセッサによってキャッシュされたデータが保存されるデータメモリ207、データメモリ207におけるデータのアドレスを一括して管理するタグメモリ206、プロセッサによって供給を要求されたデータのアドレスをタグメモリ206によって管理されているアドレスと照合し、供給を要求されたデータがデータメモリ207から読出し可能であるか否か検出するヒット検出部208、ヒット検出部208によってデータが読出し可能であることが検出された場合、検出されたデータをプロセッサに供給するキャッシュ制御部103を備える。

(もっと読む)

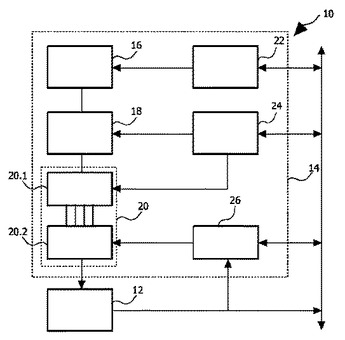

読み出し機能及びフェッチ機能を分けることによるデータ処理装置のメモリユニットの性能向上

本発明は、処理ユニット12及びメモリユニット14を有するデータ処理装置と、データ処理装置のメモリユニット14の動作の制御方法とに関する。メモリユニット14は、主要メモリ16と、処理装置12へ直接的に接続され、処理ユニット12による読出アクセスのために現在処理対象であるスライド検索範囲の全ての画素を保持するよう構成される低レベルキャッシュメモリ20.2と、低レベルキャッシュメモリとフレームメモリとの間に接続される高レベルキャッシュメモリ18と、高レベルキャッシュメモリと低レベルキャッシュメモリとの間に接続され、処理ユニットに従う走査方向及び走査順序に依存して画素ブロックの1つの検索範囲行又は1つの検索範囲列を保持するよう構成される第1のプレフェッチ・バッファ20.1とを有する。読出機能及びフェッチ機能はメモリユニット14で分離される。フェッチ機能はより高いキャッシュレベルに集められ、読出機能はより低いキャッシュレベルに集められる。このようにして、同時の読出及びフェッチは達成され、データ処理装置の性能が向上する。  (もっと読む)

(もっと読む)

キャッシュコヒーレンス装置

【課題】分散共有メモリ型のマルチプロセッサシステムにおいて、キャッシュコヒーレンシ維持を効率よく実現し、且つシステムの拡張性を損なうことのないキャッシュコヒーセンス装置の共通システムバス、更に、大規模なマルチプロセッサの利用が期待される基幹システムへの使用を考慮した信頼性の高い共有システムバス、更に、異なったバスとの接続を考慮し、既存のバス資産の有効活用を可能とする共有バスを提供する。

【解決手段】共有システムバスとして機能する第2共有バス12は、複数のプロセッサモジュールのバス接続ユニット32とバスアービタ(バス調停ユニット)とを結合して、複数のプロセッサモジュールの間でスプリット型パケット転送によりバスコマンドの転送を行い、バスコマンドに、アクセス要求元(ソースID)を示すソースフィールド、第1のアクセス要求先(第1宛先ID)を示す第1宛先フィールド、及び第2のアクセス要求先(第2宛先ID)を示す第2宛先フィールドの3つを備える。

(もっと読む)

メモリへのアクセスを制御するためのデータ処理装置および方法

【課題】処理ロジックのうちの種々の部分の間でデータを共用しなければならない場合、セキュアデータへのアクセスを規制すること

【解決手段】メイン処理ロジックは補助処理ロジックによってアクセスできる割り当てられたメモリとすべきメモリの一部を定めることができ、補助処理ロジックによる割り当てられたメモリへのアクセスを制御するためのメモリ管理ユニットが設けられる。

(もっと読む)

81 - 100 / 142

[ Back to top ]