Fターム[5B011LL13]の内容

電源 (19,167) | 節電(オートパワーオフを除く) (3,178) | 節電モードへの切替 (2,150) | CPUモードの切替 (566) | クロック周波数の変更 (312)

Fターム[5B011LL13]に分類される特許

61 - 80 / 312

印刷装置、印刷システム、及びドライバープログラム

【課題】動作周波数を真に最適化することで消費電力を低減させる印刷装置、印刷システム、及びプリンタードライバーの提供を目的とする。

【解決手段】本発明にかかる印刷装置は、印刷対象データーをもとに画像を形成する印刷装置であって、前記印刷対象データーを構成する各ページデーター単位の処理時間に基づいて設定される動作周波数をもとに、前記各ページデーター単位の動作周波数を可変にする周波数変更手段と、前記変更された動作周波数をもとに印刷処理を行なう印刷処理手段と、を有する。

(もっと読む)

半導体集積回路および電子情報機器

【課題】半導体集積回路において、スタンバイモードからの復帰時間を短くでき、スタンバイモードからの復帰のための不揮発性メモリなどの付加的な回路は不要で余分なコストが発生しないという利点を維持したまま、スタンバイモードにおける電源電圧をさらに下げることでリーク電流を抑えた低消費電力動作を実現する。

【解決手段】半導体集積回路100において、複数の内部回路のうちの主要なコア回路の動作モードを、通常動作モードとスタンバイモードとの間で切り替えるモード切替回路108と、該モード切替回路に該スタンバイモードを解除するよう指示するスタンバイ解除要因検出回路107とを備え、該モード切替回路108及び該スタンバイ解除要因検出回路107を、該スタンバイモードでのスタンバイ電圧により該システムクロックとは非同期で動作するよう構成した。

(もっと読む)

半導体装置

【課題】クロックや電源の制御を効率よく、且つ、確実に実行可能にして、消費電力を削減する。

【解決手段】本発明の半導体装置は、複数の回路ブロック2、12と、複数の回路ブロック2、12と電源9との間に設けられたスイッチ10と、複数の回路ブロック2、12に各別にクロック信号を出力する複数のクロック出力回路と、複数の回路ブロック2、12の中の少なくとも1個の回路ブロックへクロック信号が出力された時点で、スイッチ10をオンして有う複数の回路ブロック2、12の電源をすべてオンし、複数の回路ブロック2、12へのクロック信号がすべて停止された時点で、スイッチ10をオフして複数の回路ブロック2、12の電源をすべて遮断するように制御するブロック電源制御回路とを備えたものである。

(もっと読む)

電力制御装置

【課題】本発明は、ネットワークに接続されたコンピュータシステムにおいて、消費電力を削減する電力制御装置に関する。

【解決手段】第1の通信速度でネットワークに接続可能な第1のネットワーク機器と、上記第1の通信速度より早い第2の通信速度でネットワークに接続可能な第2のネットワーク機器とが接続されたネットワークシステムにおける電力制御装置であって、上記第2の通信速度のみに接続可能なハブを介して前記ネットワークに接続された上記第1、又は第2のネットワーク機器に配設され、受信パケットエラーを発生せずに正常通信を行うことができる範囲で、上記第1、又は第2のネットワーク機器のシステムクロックを最も低い周波数に自動設定することを特徴とする。

(もっと読む)

通信装置、通信装置の制御方法および情報処理システム

【課題】LANボードが動作中に省電力動作モードに移行することで生じる通信の遅延を抑止する。

【解決手段】ネットワークカード10は、スキャナー装置30が電力を通常に消費する通常状態、および電力を低減して消費する節電状態の何れの状態かを検出する状態検出部18と、自身が通常状態であり、スキャナー装置30が節電状態であることを状態検出部18が検出した場合、LAN50を介して指示される指示情報の有無に応じて、自身を節電状態に切り替えるか、否かを判断するモード移行判断部20と、モード移行判断部20の判断に基づき、自身を通常状態および節電状態の何れかに切り替えるモード切り替え部26とを備える。

(もっと読む)

データ・センタにおける電力消費の最適化

【課題】動的な作業負荷調整によってデータ・センタの電力消費を最適化するためのシステムおよび関連する方法を提供する。

【解決手段】データ・センタの現在の作業負荷配分が、最小の電力消費量で、容認可能なレベルのサービスを提供する最適作業負荷ソリューションに移行される。最適作業負荷ソリューションに対応する電力コストおよび移行コストの合計額は、それぞれの作業負荷ソリューション候補に対応する合計額全ての間の最低値である。電力コストは、各作業負荷ソリューション候補に対するデータ・センタの最高温度およびそれに伴う冷房コストに基づいて算定される。移行コストは、データ・センタの作業負荷配分を、現在の作業負荷配分から各作業負荷ソリューション候補に移行する間に生じるパフォーマンス劣化に基づいて算定される。

(もっと読む)

半導体装置及びデータ処理システム

【課題】中央処理装置が設定した低消費電力状態の解除に伴う電力消費と処理時間を短縮することができ、且つ、中央処理装置が既に設定した低消費電力状態の強制解除と復帰との関係の制御を容易に行うことができる半導体装置を提供する。

【解決手段】中央処理装置(41)自らに対して、そして被制御回路(12,22)に対して、電源及びクロックの停止と供給を制御する低消費電力のための制御機構に、所定の被制御回路から出力される電源及びクロックの停止を要求する信号(400)が要求する期間だけ、別の被制御回路に対して既に設定されている電源及びクロックの供給停止を強制解除する、強制解除制御回路(70)を採用し、強制解除に中央処理装置を介在させることを要さず、また、所定の被制御回路からの要求が終われば元の低消費電力状態に復帰されるようにする。

(もっと読む)

信号処理装置、信号処理方法およびプログラム

【課題】受け付けた信号の処理負荷に応じて最適な電力制御を行い、消費電力を抑える信号処理装置を提供する。

【解決手段】信号処理装置100は、信号を受け付ける受付部10と、受け付けられた信号を処理する集積回路31、41と、信号を受け付けたとき、当該信号を処理する集積回路に掛かると予想される負荷を示す負荷情報を取得する負荷情報取得部21と、取得された負荷情報に応じて、集積回路に供給される電源の電圧値またはクロック信号の周波数の少なくとも一方を可変に制御する供給制御部22と、を備える。

(もっと読む)

プロセッサ

【課題】プロセッサの演算量が小さい時、電源制御コントローラのクロック周波数を下げることで、電源制御コントローラの損失を低減し、電子機器のバッテリの寿命を伸ばすことができる電源システムを提供する。

【解決手段】プロセッサ1と、プロセッサ1に電力を供給するスイッチングレギュレータとしての電源制御コントローラ31およびVR35と、プロセッサ1のプロセッサコアの動作電圧とクロック周波数を可変する電圧指令発生器11およびクロック指令発生器16と、スイッチングレギュレータの入力直流電圧源としてのバッテリ34とを有する電源システムにおいて、プロセッサ1の演算量が小さい時、電源制御コントローラ31のクロック周波数を下げる。これにより、電源制御コントローラ31の損失を低減し、電子機器のバッテリ34の寿命を伸ばすことができる。

(もっと読む)

マルチプロセッサシステム

【課題】プロセッサが動作停止状態に移行した場合、キャッシュデータの一貫性を保持しつつ、キャッシュメモリの消費電力を削減できる。

【解決手段】第1及び第2のプロセッサ101、111と、共有メモリ123と、第1及び第2のキャッシュメモリ102、112と、第1及び第2のキャッシュメモリが記憶しているデータの一貫性を管理する一貫性管理回路120と、一貫性管理回路から第1及び第2のキャッシュメモリに対して、データ更新を要求する要求信号を伝達するための要求信号線SCOPと、第1及び第2のキャッシュメモリから一貫性管理回路に対して、データ更新が完了したことを通知する通知信号を伝達するための通知信号線SCCOREREADYと、要求信号と通知信号とに応じて、第1及び第2のキャッシュメモリへのクロック信号及び電源の供給を制御するキャッシュ電力制御回路103、113と、を備えるマルチプロセッサシステム。

(もっと読む)

電源システム

【課題】プロセッサの演算量が小さい時、電源制御コントローラのクロック周波数を下げることで、電源制御コントローラの損失を低減し、電子機器のバッテリの寿命を伸ばすことができる電源システムを提供する。

【解決手段】プロセッサ1と、プロセッサ1に電力を供給するスイッチングレギュレータとしての電源制御コントローラ31およびVR35と、プロセッサ1のプロセッサコアの動作電圧とクロック周波数を可変する電圧指令発生器11およびクロック指令発生器16と、スイッチングレギュレータの入力直流電圧源としてのバッテリ34とを有する電源システムにおいて、プロセッサ1の演算量が小さい時、電源制御コントローラ31のクロック周波数を下げる。これにより、電源制御コントローラ31の損失を低減し、電子機器のバッテリ34の寿命を伸ばすことができる。

(もっと読む)

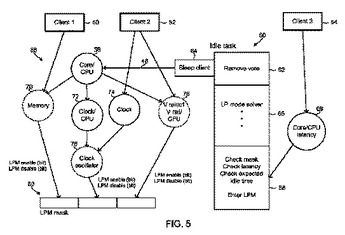

コンピューティングデバイスのための動的低電力モード実装

態様は、使用されていないリソースと、許容できるシステムレイテンシと、動的動作条件(たとえば、温度)と、予想アイドル時間と、特定のデバイスの固有の電気的特性とに応じて、確実に機能し続けながら、選択されたリソースを低電力モードにすることによって、コンピューティングデバイスまたはマイクロプロセッサが、最も多くのシステム電力節約を与える低電力モードを判断することを可能にする。態様は、プロセッサがアイドル状態に入ったときに、どの低電力モードが有効であるかを判断することと、現在のデバイス条件が与えられたときに予想される電力節約によって有効な低電力モードをランク付けすることと、レイテンシ要件を満たしながら、どの有効な低電力モードが最も大きい電力節約を与えるかを判断することと、各リソースが入るべき特定の低電力モードを選択することとによって、コンピューティングデバイス内の様々なリソースについて低電力モードのセットからなる最適な低電力構成を判断するための機構を提供する。  (もっと読む)

(もっと読む)

処理装置、処理方法、及び処理プログラム

【課題】将来的に処理装置が処理すべきプログラムについて要求される処理能力を考慮してクロック周波数を決定することができる、処理装置、処理方法、及び処理プログラムを提供すること。

【解決手段】処理装置1は、プログラムを構成する命令をクロック周波数のクロック信号に同期して処理する処理装置1であって、命令を処理する際に要求されるクロック周波数を特定する情報であって、プログラムに予め含まれる要求クロック周波数情報を取得する命令情報取得部31と、要求クロック周波数情報に基づき、命令を処理する際のクロック周波数を決定するクロック制御部32とを備える。

(もっと読む)

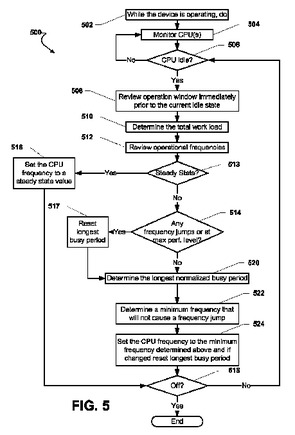

周波数変動を低減させて中央処理装置電力を制御するためのシステムおよび方法

中央処理装置内の電力を動的に制御する方法が開示され、アイドル状態に入ること、アイドル状態の直前のビジーサイクルを点検すること、および前のビジーサイクルに基づいて、次のビジーサイクルに関するCPU周波数を算出することを含むことが可能である。  (もっと読む)

(もっと読む)

保証された定常状態期限で中央処理装置電力を制御するためのシステムおよび方法

中央処理装置を動的に制御する方法が、開示される。この方法は、CPUがいつ定常状態に入るかを判定すること、CPUが定常状態に入ると、CPUに関する最適な周波数を計算すること、定常状態CPU利用率を保証すること、および定常状態CPU利用期限を保証することを含むことが可能である。 (もっと読む)

中央処理ユニットをリアルタイムで監視するシステムおよび方法

1つまたは複数の中央処理ユニットをリアルタイムで監視する方法を開示する。本方法は、1つまたは複数のCPUに関連する状態データをリアルタイムで監視するステップと、状態データをフィルタ処理するステップと、フィルタ処理された状態データに少なくとも部分的に基づいて、1つまたは複数のシステム設定を選択的に変更するステップと含み得る。  (もっと読む)

(もっと読む)

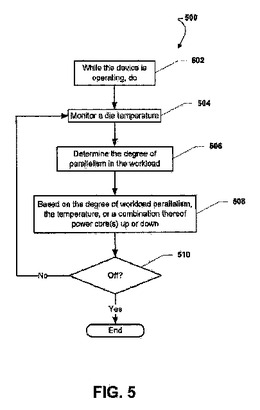

温度に基づいてマルチコア中央処理装置内の複数のコアを動的に制御するためのシステムおよび方法

マルチコア中央処理装置(CPU)内の電力を制御する方法が開示される。本方法は、ダイ温度を監視するステップと、CPUの作業負荷内の並列性の度合いを判定するステップと、並列性の度合い、ダイ温度、またはそれらの組合せに基づいて、前記CPUの1つまたは複数のコアの電源を上げるまたは落とすステップとを含みうる。  (もっと読む)

(もっと読む)

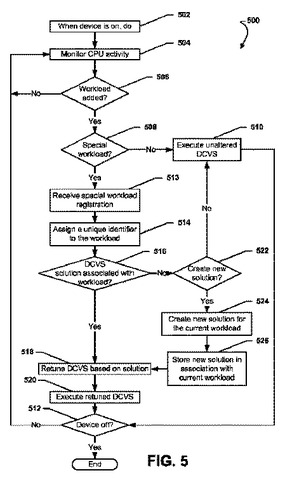

ワークロードの要求に基づいて動的なクロックおよび電圧切替えアルゴリズムを調整するシステムおよび方法

動的なクロックおよび電圧切替えアルゴリズムを調整する方法が開示されており、デフォルトの応答度を設定するステップと、ワークロードが追加された後、ワークロードが登録しているかどうかを決定するステップと、ワークロードが登録している場合、一意の識別子をワークロードに割り当てるステップと、ワークロードから必要な応答度を受信するステップとを含み得る。  (もっと読む)

(もっと読む)

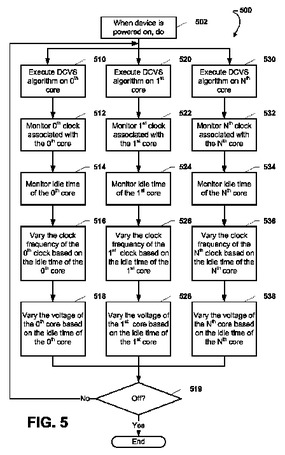

マルチコア中央処理装置内の複数のコアクロックを非同期で、独立に制御するためのシステムおよび方法

マルチコア中央処理装置内の複数のコアクロックを制御する方法が、開示され、さらに第0のコア上で第0のDCVS(動的クロックおよび電圧スケーリング)アルゴリズムを実行すること、および第1のコア上で第1のDCVSアルゴリズムを実行することを含むことが可能である。第0のDCVSアルゴリズムは、第0のコアに関連する第0のクロック周波数を独立に制御するように動作できることが可能であり、さらに第1のDCVSアルゴリズムは、第1のコアに関連する第1のクロック周波数を独立に制御するように動作できることが可能である。  (もっと読む)

(もっと読む)

プロセッサを動的に制御するシステムおよび方法

中央処理装置(CPU)内で動的なクロックおよび電圧スケーリング(DCVS)アルゴリズムを実行する方法が開示されており、CPUのアクティビティを監視するステップと、ワークロードがCPUのアクティビティに追加されたとき、ワークロードが特殊なワークロードに指定されるかどうかを決定するステップとを含み得る。  (もっと読む)

(もっと読む)

61 - 80 / 312

[ Back to top ]