Fターム[5B011LL13]の内容

電源 (19,167) | 節電(オートパワーオフを除く) (3,178) | 節電モードへの切替 (2,150) | CPUモードの切替 (566) | クロック周波数の変更 (312)

Fターム[5B011LL13]に分類される特許

121 - 140 / 312

モーションコントロールシステム

【課題】 モーションコントローラに搭載されたCPUの省電力モードを利用することで、低消費電力化を実現するモーションコントロールシステムとその制御方法を提供することを目的とする。

【解決手段】

モーションコントローラに、ステータスと応答時間の関係を設定した応答時間テーブルと、CPUを省電力モードへの切り替える最低プライオリティの省電力タスクを設け、上位PCからのコマンドの応答時間を、応答時間テーブルに沿って変化させることで、省電力タスクを起動しCPUを省電力モードへ切り替える。

(もっと読む)

マルチコアプロセッサ及びその制御方法

【課題】

一群のタスクに着目して、一群のタスクを処理する複数のプロセッサコアへ供給する電源電圧又は動作クロックの周波数を関連をもたせて制御する機能を備えることにより、低電力化を図ったマルチコアプロセッサの提供。

【解決手段】

複数のプロセッサコアと、タスクについての第1タスク群の識別番号と、タスク処理時間と、第1タスク群に含まれるタスクを実行する上限期間を記憶するレジスタと、第1タスク群に含まれるタスクの内、並列に処理される複数のタスクからなる第2タスク群を抽出し、第2タスク群を処理する第1処理時間を、第2タスク群を処理するプロセッサコアの消費電力に応じて第2処理時間として設定する設定回路と、タスク処理時間と、第2処理時間との比率に応じて、各タスクを処理するプロセッサコアへ供給する動作クロックの周波数又は電源電圧を変更する駆動回路と、を備えるマルチコアプロセッサが提供される。

(もっと読む)

プログラマブルコントローラにおいてI/O点数に応じたCPU駆動システム

【課題】I/O点数に応じてCPUでの信号処理速度を所望する速度に維持する一方で、同時に、必要以上の電力消費を抑制し得るプログラマブルコントローラを提供する。

【解決手段】本発明によるプログラマブルコントローラ1は、CPU3の動作クロックの周波数設定に用いる原クロックの周波数をI/O点数が一定数以下に減るとその減少に合わせて逓減し、また、一定数以上に増えるとその増加に合わせて逓倍して、CPU3の動作クロックの周波数を調整する。

(もっと読む)

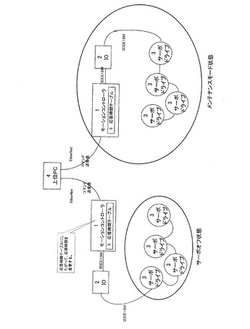

情報処理システムおよびそのCPUクロック周波数制御管理方法

【課題】

ネットワーク上で全ての情報装置を一括管理することで、各情報装置のCPUクロック周波数の一括制御を行うことを可能とし、さらに、スケジュール設定により夏季電力消費ピーク時等の電力消費の多い特定の時間帯でCPUの消費電力制御を行うことで消費電力を下げることが可能となるような情報処理システムおよびCPUクロック周波数制御管理方法を提供する。

【解決手段】

複数の管理端末装置と前記複数の管理端末装置を管理する管理装置とがネットワークを介して接続された情報処理システムにおいて、各管理端末装置は自装置のCPUのCPUクロック周波数を制御するCPUクロック制御手段を備え、前記管理装置は前記複数の管理端末装置のCPUクロック制御手段を介して各管理端末装置のCPUのCPUクロック周波数を一括制御するCPUクロック制御管理手段を備える。

(もっと読む)

演算制御装置、マイクロプロセッサ及び機器

【課題】プロセッサ内蔵する演算装置において、新メモリ登場などによりますます顕在化する、複数の演算装置間の待合せ時間における消費電力及び演算能力の浪費の削減と、演算装置のコンテキストスイッチ負荷の削減が課題である。

【解決手段】マイクロプロセッサと、マイクロプロセッサに接続されたメモリとを備える機器に備わる演算制御装置であって、マイクロプロセッサは、複数の演算部を備え、メモリは、複数の演算部が読み書き可能な共有記憶領域を含み、演算制御装置は、共有記憶領域への書き込みができるか否かを検出する書込検出部を備え、演算部が共有記憶領域に書き込みができない場合、共有記憶領域を監視し、演算部の稼動を停止することを特徴とする。

(もっと読む)

トリガー信号検出装置

【課題】消費電力を低減できるトリガー信号検出装置を提供する。

【解決手段】トリガー信号trigおよびクロックsysclkが入力されて内部クロックclkinを出力するクロックゲーティング回路CG1と、クロックゲーティング回路CG1から内部クロックclkinが入力されて所定時間だけ信号outputを出力するトリガー信号処理回路TG1と、トリガー信号trigに応答してカウントアップ動作を開始し、カウント値countを出力するカウンタC1と、カウンタC1から入力されるカウント値countが予め設定された値に到達すると信号AAを生成してトリガー信号処理回路TG1に出力し、信号outputの出力を停止させる時間設定回路TS1と、を備える。

(もっと読む)

アイドル状態検出回路、半導体集積回路、アイドル状態検出方法

【課題】プロセッサのアイドル状態を正確に検出する。

【解決手段】比較部102は、プロセッサ11によって参照されたアドレスとロードアドレス記憶部101に記憶された前回のロードアドレスとを比較する。比較部104は、プロセッサ11によってロードされたデータとロードデータ記憶部103に記憶されたデータとを比較する。比較部106は、サイクルカウンタ105のカウント値と規定サイクル数CKXとを比較する。制御部107は、プロセッサ11が同一のアドレスから同一のデータをロードしていることを検出すると、ループ回数記憶部108に記憶されたループ回数をインクリメントする。比較部109は、ループ回数記憶部108に記憶されたループ回数が規定ループ回数LPXよりも多い場合にアイドル状態通知信号S109をアサートする。

(もっと読む)

アクティブ電力管理

複数のアクティブ周期中にソフトウェアを実行するプロセッサのクロック周波数を制御する方法であって、前記方法は、各周期に対して、高周波数動作インターバル及び低周波数動作インターバルを有する前記周期に対する実行プロファイルを定義する少なくとも1つのパラメータを電力管理アプリケーションに供給する段階と、前記電力管理アプリケーションが、前記プロファイルに基づいて、高周波数動作インターバル及び低周波数動作インターバルに対して所定のクロック周波数を決定する段階と、前記プロセッサが、前記周期に対する動作サイクル要求を、周期の開始時に、前記電力管理アプリケーションに供給する段階と、前記電力管理アプリケーションが、前記低周波数インターバル長を、前記動作サイクル要求に基づいて、各周期に対して、決定する段階と、前記電力管理アプリケーションによって決定した前記所定のクロック周波数に基づいて、各インターバル内で前記クロック周波数を制御する段階とを有することを特徴とする方法。  (もっと読む)

(もっと読む)

プロセッサシステムの動作方法およびプロセッサシステム

【課題】 性能を劣化させずに省電力化する。

【解決手段】 プロセッサシステムは、周期的にメイン処理を実施し、かつ、周期内に発生する割り込み処理に対して、予め算出された復帰制約時間内に処理を開始するプロセッサ部と、周期毎に割り込み処理の発生履歴を保持する履歴記憶部と、プロセッサ部の動作モードを選択するモード制御部と有している。例えば、プロセッサ部は、通常モードと、省電力化のための複数の省電力モードとを有している。そして、例えば、モード制御部は、メイン処理および割り込み処理のいずれも実施されない期間では、発生履歴に基づいて検出される未実施の割り込み処理の復帰制約時間と、各省電力モードから通常モードに復帰するまでの復帰時間と、周期の残り時間とに基づいて、プロセッサ部の動作モードを、通常モードおよび複数の省電力モードから選択する。

(もっと読む)

半導体集積回路

【課題】主電源とバックアップ電源とを切り換える切換回路を内蔵しないリアルタイムクロック用の半導体集積回路において、バックアップモードにおける消費電力を低減する。

【解決手段】この半導体集積回路は、外部の主電源による第1の電源電圧又は外部のバックアップ電源による第2の電源電圧が選択的に供給されて動作する半導体集積回路であって、第1又は第2の電源電圧に基づいて第3の電源電圧を生成する定電圧回路と、第3の電源電圧が供給されて原振クロック信号を生成する発振回路と、原振クロック信号を分周し、分周されたクロック信号に基づいて計時情報を管理するロジック回路と、第1の電源電圧が供給されているか否かを表す信号に従って、第1の電源電圧が供給されていないときに、定電圧回路から出力される第3の電源電圧の値又は定電圧回路の動作期間を減少させる制御回路とを具備する。

(もっと読む)

半導体装置の作製方法

【課題】分周回路において消費電流を削減することを課題とする。特に、多段の分周回路において消費電流を削減すること課題とする。

【解決手段】多段の分周回路100では、初段ほど入力される信号の周波数が高く、後段ほど入力される信号の周波数は低くなる。よって、高い周波数の信号が入力される分周回路に対応する基本セル(D1)から優先的に配置し、配線接続を行う。つまり、高い周波数の信号が入力される配線を、より低い周波数の信号が入力される配線と比較して、配線長が短く、他の配線との交差が少なくなるように、即ち配線の寄生容量、寄生抵抗が小さくなるように、多段の分周回路に対応する複数の基本セルをレイアウトする。

(もっと読む)

認識可能な電力管理を実現する方法

CPUレベル電力管理の技術によって、企業サービス利用の異なる構成と、電力使用を相関させるための統合された環境及び計算パワーモニタリングにより生成されるデータセンタの包括的な動的モデルに基づき電力管理アプローチを統合することによって、データセンタにおける全体的な電力使用の効率性を向上させるシステム及び方法。  (もっと読む)

(もっと読む)

画面表示制御装置およびこの画面表示制御装置の制御用プログラム

【課題】必要なときにのみクロックアップすることにより、画像メモリからの画像データの読出しを阻害することなく、画像メモリへの画像データの書込みを確実に行うとともに、コストダウンを図ることのできる技術を提供する。

【解決手段】画像データ書込要求信号と画像データ読出要求信号との受付けが重複したときにのみ、RAM制御部765は、高速モードの高クロックを生成するように、クロック切換部764に対してクロック切換信号を出力するため、必要なときにのみクロックを切換えてクロックアップすることにより、VRAM766からの画像データの読出しを阻害することなく、VRAM766への画像データの書込みを確実に行うことができる。また、必要なときのみクロックアップすることで、放射電磁波などを低減できるとともに省電力を図ることができるためコストダウンを図ることができる。

(もっと読む)

情報処理装置

【課題】複数のプロセッサコアが搭載された情報処理装置において性能電力比の向上を実現する。

【解決手段】例えば、64個のプロセッサコアPE0〜PE63や、オンチップメモリON_MEMや、これらに共通に接続されるバスBSなどを備えた構成において、PE0〜PE63を低電源電圧VDDL、低周波数クロック(CLKL)で動作させ、バスBSを高電源電圧VDDH、高周波数クロックCLKHで動作させる。PE0〜PE63のそれぞれは、BSとの間の電源電圧差および周波数差を吸収するため、バスインタフェースBSIFおよび分周器DIVを備える。DIVは、CLKHからCLKLを生成し、BSIFは、レベルシフト機能、データ幅変換機能、およびBSとの間のハンドシェイク機能などを備える。

(もっと読む)

動的再構成支援プログラム、動的再構成支援装置および動的再構成支援方法

【課題】動的再構成回路によって実行させるタスクの内容にかかわらず、バッテリの負荷の少ない再構成処理を実現する。

【解決手段】動的再構成支援処理部100では、動的再構成回路110−2におけるPEの書き換え処理を、図表130のように、次のタスクが開始されるまでのデッドライン時間に応じて分割する。そして、分割したPEをデッドライン時間までに順番に実行させることによって一度に実行される書き換え処理量を分散する。また、PEの分割時に現在のバッテリ残量と、消費電力を参照して、PEの書き換え処理に要する電力値のピーク変化がより平準化するように調整することもできる。

(もっと読む)

電源制御システム、および電源制御方法

【課題】情報処理装置に不具合が生じることなく、しかも、電源装置の電力変換効率を常に高く維持することができる電源制御システム、および電源制御方法を提供する。

【解決手段】必要電力算出装置3は、周波数制御部23により生成された周波数情報が示す動作周波数でCPU21が動作するためにブレードサーバ2a〜2dにおいて必要となる必要電力を算出し、電源制御装置5は、算出された必要電力を電源装置4がブレードサーバ2a〜2dに対して供給しようとする場合に、電源装置4の電力変換効率が最も高くなるように、電源装置4を制御し、電源装置4は、算出された必要電力をブレードサーバ2a〜2dに対して供給することにより、ブレードサーバ2a〜2dにおいて使用すべき電力を上昇させ、周波数制御部23は、周波数情報が示す動作周波数をCPU21に対して割り当てることにより、CPU21の動作周波数を上昇させる。

(もっと読む)

電子装置

【課題】省電力動作が可能な電子装置を提供する。

【解決手段】電子装置は、抵抗器に流れる電流値に応じて、所定の電力を消費する第1のモード、または、前記第1のモードにおいてより少ない電力を消費する第2のモードを設定する制御回路と、前記電流値に応じて、クロック信号を生成する信号生成回路と、前記第1のモードまたは第2のモードで動作し、前記クロック信号に応じた性能で電力を消費する電子回路と、前記モード設定を受けて、前記第1のモードにおいて、前記抵抗器を、前記電子回路が、所定の電力を消費する値とし、前記第2のモードにおいて、前記抵抗器を、前記電子回路が、第1のモードにおいてより少ない電力を消費する値とする抵抗値変更回路とを有する。

(もっと読む)

ワイマックス状態駆動の電力節約のための方法及びシステム

メディアアクセスコントロール(MAC)層状態に従ってデバイス処理器のクロック周波数及び又は電圧を動的調整することで無線通信のためのモバイル装置内のバッテリー電力を節約するための方法及び装置が提供される。多くの量のデータトラフィックを伴う通常動作状態のためのより高いクロック周波数及び又はより高い電圧と、他のMAC層状態(例えば取得、ネットワークエントリー、及びスリープ/アイドル状態)のためのより低い周波数及び又はより低い電圧と、を使用することにより、バッテリー電力が節約されることができる、それにより、バッテリー充電サイクルの中で装置が動作する時間を引き延ばすことができる。 (もっと読む)

ミクロアーキテクチャのバンド幅スロットリングによるプロセッサ電力消費制御及び電圧降下

方法、装置及びシステムが開示される。一実施形態において、方法は、第1電圧をプロセッサに供給するステップを有する。方法は、更に、プロセッサが第1電圧で拡張プロセッサ休止状態において機能することを可能にするステップを有する。第1電圧は、拡張プロセッサ休止状態に係る最低適合電圧を下回る電圧である。方法は、プロセッサで実行される命令の最大スループットレートを減じることによって、プロセッサが第1電圧で拡張プロセッサ休止状態からのウェイク時に命令を実行することを可能にするステップを有する。  (もっと読む)

(もっと読む)

記憶制御装置

【課題】通信ポート単位で消費電力を低減させることができる記憶制御装置を提案する。

【解決手段】記憶制御装置は、複数の通信ポート18を有し、これらの通信ポートを介して接続可能なホスト装置2との通信を制御するホスト通信制御部10と、複数の記憶装置との通信を制御する記憶装置通信制御部16と、ホスト装置と記憶装置との間で送受信されるデータを、ホスト通信制御部10と記憶装置通信制御部16との間で転送させる複数のDMA111と、DMA111で転送されるデータを一時的に記憶する複数のキャッシュメモリ12と、一の通信ポートのホスト装置との接続状況および一の通信ポートに入出力されるデータ量に基づいて、一の通信ポートに対して予め対応付けられているDMA111およびキャッシュメモリ12を停止させる省電力制御部110と、を有する。

(もっと読む)

121 - 140 / 312

[ Back to top ]