Fターム[5B018GA04]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | 誤動作防止、障害防止、データ消失防止 (1,341)

Fターム[5B018GA04]に分類される特許

61 - 80 / 1,341

電子機器

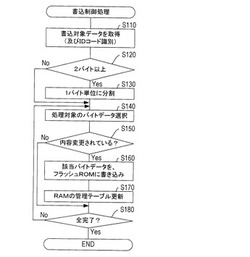

【課題】フラッシュROMに対し、効率的にデータを書込可能な技術を提供する。

【解決手段】電子制御装置のMPUは、フラッシュROM13への書込対象データを、1バイト単位のデータ(バイトデータ)に分割し(S130)、この書込対象データを構成するバイトデータの夫々を、順に処理対象データに選択する(S140)。そして、処理対象データと、フラッシュROMが記憶する当該処理対象データに対応するバイトデータとを比較し(S150)、処理対象データが、フラッシュROMが記憶するものから内容変更されたものである場合には(S150でYes)、これをフラッシュROMに追記する形式で書き込む(S160)。一方、処理対象データがフラッシュROMが記憶するものから内容変更されたものでなければ(S150でNo)、この処理対象データのフラッシュROMへの書込については行わないようにする。

(もっと読む)

電子機器

【課題】不揮発性メモリにおける記憶ブロック間のデータ消去回数のばらつきを抑える。

【解決手段】電子制御装置は、フラッシュROMを備える。フラッシュROMは、複数の記憶ブロックを備え、記憶ブロック単位でのデータ消去が可能な周知のメモリである。電子制御装置のMPUは、フラッシュROMの記憶ブロック群を、書込頻度が低いデータ記憶用の低頻度ブロック群と、書込頻度が高いデータ記憶用の高頻度ブロック群とにグループ化する。そして、高頻度ブロックのデータ消去回数に基づき、データ消去回数が100の倍数となる度、低頻度ブロックを、記憶ブロック一つ分ずらすようにして、高頻度ブロックと入れ替える。この動作によって、フラッシュROM内の記憶ブロック群を再グループ化する。一般的に高頻度ブロックのデータ消去回数のほうが低頻度ブロックよりも多くなるが、再グループ化により記憶ブロック間のデータ消去回数のばらつきは抑えられる。

(もっと読む)

コンピュータ、その制御方法及びプログラム

【課題】MBRとバックアップセクタデータを検証し、正常にリードできない又は不正であるときに、自動的に復旧し起動処理を実行する。

【解決手段】シャットダウンを検知した場合に、MBRとバックアップMBRのリードを行い、MBRのデータとバックアップMBRのデータとが同一でないときにMBRをバックアップMBRにコピーするか、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーするかする。コンピュータの電源をオンした場合に、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーする。

(もっと読む)

フラッシュメモリ装置

【課題】フラッシュメモリ装置において、メンテナンス中にリセットが発生した場合であっても、より確実に真の最新値を読み出すことにある。

【解決手段】第2のブロックB2への最新値のコピーが完了した後に、第1のブロックB1におけるブロック管理値を未使用状態とするとともに、第1のブロックB1のデータを消去するメンテナンスが実行される。このように、メンテナンス実行時には、第1のブロックB1のブロック管理値は、「$FFF0」から「$FFFF」とされる。メンテナンス中に電源がオフ状態となるリセットが発生した場合には、ブロック管理値における「$0」の桁が、16進法における「1」〜「E」となる可能性がある。このように、ブロック管理値が1桁の「1」〜「E」と、3桁の「F」とで構成される場合には、その値を有するブロックからの最新値の読み出しが規制される。

(もっと読む)

記録媒体、光伝送モジュール、データ保存方法及びメモリ管理装置

【課題】不揮発メモリへ書き込み中に電源等が断たれた場合であっても、より最新のデータ情報を利用可能な記録媒体を提供する。

【解決手段】データ保存方法は、書込み要求されたデータと揮発性ユーザデータ領域のアドレスのデータとを比較し、データの変更があるか否かを判定するデータ変更判定ステップ(S11)と、データ変更判定ステップにおいて肯定的な判定の場合に、揮発性ユーザデータ領域の対応するアドレスに書込みを行う揮発性領域書込みステップ(S12)と、パリティビットを生成し、変更の内容を第1不揮発性バッファ領域にデータ毎に保存すると共に、保存先を示すアドレスを逐次変更する第1変更内容保存ステップ(S13,S14)と、第1不揮発性バッファ領域へ保存量が所定量に達した場合に、揮発性ユーザデータ領域のデータを第2不揮発性ユーザデータ領域にデータ毎に複製保存する第1複製保存ステップ(S16)と、を備える。

(もっと読む)

印刷装置及びその制御方法

【課題】印刷データのリード速度が低下することを抑制すると共に、リードエラーを回復可能な半導体不揮発性記憶素子を搭載した印刷装置及びその制御方法を提供する。

【解決手段】装置全般の制御を司る制御部210は、高い処理スピードが要求される処理動作を実行することを検知する。制御部210は、データを記憶すると共にデータのリード時にリフレッシュする機能を持つ記憶部制御部221を備えた記憶部220からデータをリードする時にリフレッシュ動作を停止させるためのリフレッシュ停止手段を備える。制御部210は、高い処理スピードが要求される処理動作の際にリフレッシュ動作を停止させた場合に、高い処理スピードが要求される処理動作の終了後にリフレッシュ動作を許可するためのリフレッシュ許可手段を備える。

(もっと読む)

制御装置、記憶装置、制御方法

【課題】不揮発性メモリのデータ信頼性向上と読出アクセス時間の高速化及び安定化

【解決手段】不揮発性メモリに記憶されたデータについて、近い将来リフレッシュが必要となるか否か、つまりリフレッシュ機会が近接しているか否かを推測する。この推測にはアクセス時のビットエラー数などを記憶した評価用情報を用いる。そしてリフレッシュ機会が近接していると判定されるデータについて、そのデータをオリジナルデータとして、オリジナルデータと同一のクローンデータを、不揮発性メモリ内に生成する。その場合、アクセス実行の際にオリジナルデータとクローンデータのいずれか一方がアクセス対象となるように、管理情報を更新する。

(もっと読む)

画像処理装置、リフレッシュ方法およびプログラム

【課題】画像処理装置に設けられた不揮発性メモリに対して、比較的に簡素な構成で適切にリフレッシュを行うことができるようにする。

【解決手段】画像処理装置は、自装置で用いられるデータを保存する不揮発性メモリと、自装置の動作状況を認識する認識手段101と、認識手段101が認識した動作状況をと、記憶部に予め記憶された自装置の動作状況ごとの温度変化を示す動作温度情報とを用いて、不揮発性メモリのリフレッシュの要否を判定する判定手段102と、リフレッシュが必要であると判定手段102が判定した場合、不揮発性メモリをリフレッシュするリフレッシュ手段103と、を備える。

(もっと読む)

RAM値保証装置およびRAM値保証プログラム

【課題】RAMの記憶容量を抑制しながらRAMの記憶値を保証できるようにしたRAM値保証装置およびRAM値保証プログラムを提供する。

【解決手段】CPUは、OSによりプログラムカウンタ6の示すアドレスを監視し、非保証プログラム領域9から保証プログラム領域10にプログラムカウンタ6のアドレスが遷移することを確認すると、保証RAM領域12のデータとバックアップRAM領域13のデータとを比較し、当該データが異なっているときには保証RAM領域12のデータをバックアップRAM領域13のデータで更新する。CPU8はOSによりプログラムカウンタ6の示すアドレスを監視し、更新許可領域10aから更新許可領域10bにプログラムカウンタ6のアドレスが遷移することを確認すると、その遷移直前にRAM_A群バックアップ13aの更新を許可し、RAM_A群バックアップ13aのデータをRAM_A群12aのデータで更新し、更新処理後にRAM_A群バックアップ13aの更新を禁止する。

(もっと読む)

フラッシュメモリ装置

【課題】フラッシュメモリ装置において、ブロック間で最新値をコピーしている間にリセットが発生した場合であっても、真の最新値を認識することにある。

【解決手段】ブロック管理値をアクティブ状態とする際に、ブロック管理値がブロック毎に異なるとともに順に大きくなるように設定される。例えば、ブロック管理値として第1のブロックB1には「$1111」が、第2のブロックB2には「$1112」が記憶される。このため、たとえ、アクティブ状態であるブロックが複数存在する場合であっても、ブロック管理値が大きいブロックの最新値を読み出すことで、真の最新値を読み出すことができる。

(もっと読む)

記録再生装置

【課題】フラッシュメモリの劣化をより迅速に検出できる。

【解決手段】速度導出部180は、SSD136に対するデータの読み書き速度を導出する。速度保持部138は、速度導出部が導出した読み書き速度を保持する。劣化判定部182は、任意の時点のSSDに対するデータの読み書き速度の、速度保持部に保持されている任意の時点より前の読み書き速度に対する変化率を導出し、導出された変化率が所定の閾値以下となると、SSDが劣化していると判定する。報知部184は、劣化判定部が、SSDが劣化していると判定した場合、その旨報知する。

(もっと読む)

データ記憶装置

【課題】フラッシュメモリなどのEEPROMにおいて、データ変化を防止する専用の記憶容量を設けなくても、データ変化及びデータ消失の抑制を可能とし、かつ、それに必要な処理能力を抑制することが可能な技術を提供することを目的とする。

【解決手段】監視記録装置56は、CPU1と、フラッシュメモリ2と、RAM3と、CPU1の使用率を計数する使用率計数部16とを備える。CPU1は、フラッシュメモリ2から記憶データを読み出してRAM3に記憶した後、再びRAM3からフラッシュメモリ2の元アドレスに書き戻す上書き処理を行う。CPU1は、この上書き処理を、使用率計数部16で計数された使用率が所定のしきい値よりも低い場合に実行する。上書き処理は他の処理によるフラッシュメモリ2への読み書きが禁止される排他処理とともに実行され、CPU1は、上書き処理を他の処理と時分割で実行する。

(もっと読む)

記憶装置のデータ保護装置

【課題】キャッシュ領域に転送済みのデータが消失することを防止することが可能な記憶装置のデータ保護装置を提供すること。

【解決手段】制御装置10に備わった、データが格納される不揮発性データ記憶領域14と、不揮発性データ記憶領域14に格納されるデータを一時的に保存するキャッシュ領域15とを有する記憶装置13のデータ保護装置であって、入力電源から供給される電源の電圧を所定の電圧に変換する内部電源装置11と、入力電源から供給される電源の電圧を監視し該電圧の低下を検出した時に電圧低下信号を出力する電源監視回路12と、電圧低下信号を受信したときキャッシュ領域15に保存されたデータを不揮発性データ領域14に書き込む書き込み指令を出力する中央演算処理回路16と、前記書き込み指令が出力されたとき、キャッシュ領域15に保存されたデータを不揮発性データ記憶領域14に書き込むようにした記憶装置のデータ保護装置。

(もっと読む)

記憶装置、ホスト装置、回路基板、液体容器及びシステム

【課題】アクノリッジを送受信し、且つ、書き込み処理時間を短縮することができる記憶装置、ホスト装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、バスBSを介して接続されるホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータが書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130とを含む。制御部110は、バスBSに接続される複数の記憶装置100のうちのm(mは1以上の整数)個の記憶装置100に対するホスト装置400によるデータの書き込み期間の終了後に、ホスト装置400からのID情報を受信し、且つ、自身の記憶部120にホスト装置400からのデータが正常に書き込まれている場合に、ホスト装置400に対してアクノリッジを返信する。

(もっと読む)

不揮発性メモリへのデータ保存方法および制御装置

【課題】書き換え保証回数内で書き換え頻度を変更し、不揮発性メモリでのデータ記憶の信頼性を向上することができる不揮発性メモリへの保存方法を提供する。

【解決手段】複数のデータを保存し、電気的に上記データの書き換えが可能で、各データの書き込み範囲より大きい所定範囲の単一ブロックを一括でしか消去できない不揮発性メモリ4へのデータの書き換えを行う制御装置100は、複数のデータが、書き換え頻度の高いデータと、書き換え頻度の低いデータとからなり、不揮発性メモリ4の書き換え回数をカウントするカウント部10と、カウント部10にてカウントされた書き換え回数が所定値以上であるか否かを判断する判断部11と、判断部11にて所定値以上と判断されると書き換え頻度の高いデータの書き換え頻度を変更する設定部12とを備える。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

計測装置、電力量メータ及び書き込み方法

【課題】アドレス管理用領域を確保しなくても、不揮発性メモリの書き換え回数を均一化して利用効率を高めることができる計測装置を提供することを目的とする。

【解決手段】単調増加または単調減少するカウンタデータを、上位桁データと中位桁データと下位桁データとに分割するデータ分割部121と、分割された中位桁データを、不揮発性メモリ103の第1の記憶領域に書き込むための第1アドレスを算出し、中位桁データと第2の記憶領域の数である配置数との剰余計算を行うことにより上位桁データ及び下位桁データを、不揮発性メモリ103の複数の第2の記憶領域のいずれかに書き込むための第2アドレスを算出するアドレス算出部122と、算出された第1アドレスに対応する第1の記憶領域に中位桁データを書き込み、算出された第2アドレスに対応する第2の記憶領域に、上位桁データ及び下位桁データを書き込むデータ書き込み部123とを備える。

(もっと読む)

半導体装置、不揮発性メモリ装置の制御方法

【課題】長寿命化などを実現できる半導体装置を提供する。

【解決手段】本半導体装置(メモリモジュールMM0)の制御回路(SC0)は、データ書込みの要求に対し、上書き可能な不揮発性メモリ装置(NVM)へのデータ書込みの際、上書き要求であっても上書き動作せずに、データの書込と消去のサイズを同じにして、メモリ(NVM)のアドレスを連続的に割当てて使用し、メモリ(NVM)の使用のバラツキを抑え平準化する仕組みにより、長寿命化などを実現する。制御回路(SC0)は、(a)第1のアドレスのデータの消去動作、またはフラグ値を無効に設定する動作と、(b)第1のアドレスとは別の第2のアドレスに対するデータの書込動作、またはフラグ値を有効に設定する動作との2種類の動作のセットによりデータ書込みを実現する。

(もっと読む)

フラッシュメモリ保持データのバックアップ通知システム、その方法およびプログラム

【課題】

端末装置に搭載されたフラッシュメモリについて、メーカが保証する消去回数よりも多く使用することができ、また、端末装置のユーザにバックアップをする必要がある旨を確実に通知できるようにする。

【解決手段】

ネットワークを介して相互に通信可能な端末装置とサーバ装置とを備えるシステムであって、端末装置はフラッシュメモリのリフレッシュを実施する場合にフラッシュメモリ特性情報をサーバ装置へ送信して、サーバ装置は予め設定されたフラッシュメモリ特性情報を基準として、端末装置から送信されたフラッシュメモリ特性情報を比較し、フラッシュメモリの使用限界を予測し、フラッシュメモリの寿命が近いと判断した場合に寿命が近い旨の通知を端末装置へ送信する。

(もっと読む)

半導体メモリシステム

【課題】プログラムを並列化したときに消費電流のピーク期間の重なりを防止する。

【解決手段】実施形態に係わる半導体メモリシステムにおいて、複数の半導体メモリ1の各々は、連続する複数の動作を含む内部シーケンスを実行すると共に各動作の終了後に待機期間を有し、待機期間中に次の動作の開始を予告する2ビット以上の予告信号STAをメモリコントローラ28へ通知すると共に、メモリコントローラ28から内部シーケンスの再開命令を受けたときに次の動作を開始する。メモリコントローラ28は、複数の動作の各々について、動作期間及び消費電流のピーク期間に関する管理テーブルを備え、複数の半導体メモリ1のうち所定の半導体メモリから予告信号STAを受けたとき、管理テーブルに基づいて、所定の半導体メモリに対して再開命令を通知する。

(もっと読む)

61 - 80 / 1,341

[ Back to top ]