Fターム[5B018GA04]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | 誤動作防止、障害防止、データ消失防止 (1,341)

Fターム[5B018GA04]に分類される特許

21 - 40 / 1,341

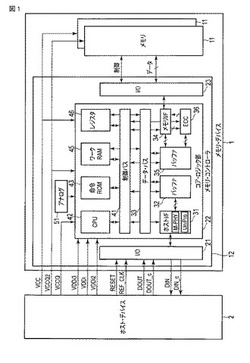

メモリデバイス

【課題】高品質なメモリデバイスを提供する。

【解決手段】メモリデバイスは、不揮発性のメモリ11と、コマンド格納部と、記憶部46と、管理部と、を備えている。コマンド格納部は、コマンドを格納する。記憶部46は、バックグランド処理の種類とその優先順位とが設定され、必要とされているバックグランド処理の情報が設定され、ホストデバイス2によって、バックグランド処理の許可または不許可が設定される。管理部は、コマンド格納部にコマンドが格納されていないと判定すると、記憶部46を参照してホストデバイス2がバックグランド処理を行うことを許可しているか否かを判定し、許可されていない場合、記憶部46に設定されたバックグランド処理の情報と優先順位とを参照して、メモリ11の未使用のブロックの数と、必要とされているバックグランド処理の優先順位及び数とに基づいてバックグランド処理の重要度を記憶部46に設定する。

(もっと読む)

メモリ管理装置

【課題】RAMのデータを保存するEEPROMの異常を検出する。

【解決手段】制御装置1は、EEPROM4を管理するメモリ管理装置を提供する。電源オフに応答して、RAM3のデータがEEPROM4に複写される。RAM3の書込結果領域31aには、EEPROM4への書込処理が正常終了したか否かが書込まれる。電源オンの後に、RAM3のデータに異常があると、EEPROM4に退避してあるデータに基づいてRAM3のデータが復元される。EEPROM4への書込処理の異常終了が所定回数継続すると、EEPROM4の故障を判定する。さらに、制御装置1は、EEPROM4への書込処理の前に、書込結果領域31aを初期化する。これにより、EEPROM4への書込処理の途中で電源が遮断され、制御装置1が再起動された場合でも、そのことを書込結果領域31aに基づいて判定できる。

(もっと読む)

不揮発性メモリを有するシステムの非正常シャットダウンの取り扱い

【課題】不揮発性メモリ(NVM)を有するシステムのための非正常シャットダウンを取り扱うためのシステム及び方法を提供する。

【解決手段】ある実施形態では、このシステムは、非正常のシャットダウン事象の後に論理的−物理的マッピングをより効率的に再構成するためにインデックスページから得た情報からレバレッジすることができる。他の実施形態では、このシステムは、NVMに記憶されたコンテクスト情報からレバレッジすることにより論理的−物理的マッピングを再構成することができる。更に別の実施形態では、コンテクスト情報は、非正常のシャットダウンの後に論理的−物理的マッピングを再構成するためにインデックスページに関連して使用することができる。

(もっと読む)

電子制御装置

【課題】フラッシュメモリへの書込み対象データに対する書込み抑制をより効率よく行うことが可能な電子制御装置を提供する。

【解決手段】データを特定するデータIDと、そのデータの、演算部の演算によって得られる値であるデータ値とを記憶するフラッシュメモリと、データID毎に対応した代表値IDが定められ、その代表値ID毎に予め定められた代表値を記憶する代表値記憶部と、データID毎に、対応するデータ値と代表値うちのいずれを該データIDに対応する値として使用するかを表すデータ管理情報を記憶するデータ管理情報記憶部と、データ書込部がデータを書き込む際に、書き込むデータ値と代表値とが同一のときには、データ管理情報を、データIDに対応する値として代表値を使用する代表値使用状態を表すものとするとともに、データ書込部によるフラッシュメモリへの該データIDに対応するデータ値の書き込みを抑止する書込制御部と、を備える。

(もっと読む)

記憶装置、記憶装置の制御方法およびコントローラ

【課題】容量の小さなバックアップ電源を使用して電源断時の不揮発化処理を可能とする。

【解決手段】電源断が発生する前の通常時に、少なくとも1つの消去済みフリーブロックが予備のブロックとして常に確保されているように不揮発性メモリに消去済みフリーブロックを作成し、電源断が発生した場合、予備のブロックを使用して不揮発化が完了していないデータおよび該データに関する論物変換情報を不揮発性メモリに書き込む不揮発化処理を実行する。

(もっと読む)

情報処理装置および情報処理方法

【課題】複数の半導体メモリをストレージとして用いる場合のトータル的な応答性の向上を図ることのできる情報処理装置を提供する。

【解決手段】この情報処理装置は、複数の半導体メモリそれぞれの物理的特性を評価して、評価結果に見合った用途属性を、少なくとも一部の半導体メモリに割り当てる割当部と、データのライト命令に対して当該データのライト先として最適な用途属性の前記半導体メモリを判定する判定部とを具備する。複数の半導体メモリの物理的特性に個体差がある場合に、その半導体メモリの物理的特性が活かされるようにデータのライト先が判定部にて判定される。これにより、複数の半導体メモリを1つのストレージとして用いた場合のストレージのトータル的な応答性の向上を期待できる。

(もっと読む)

ストレージコントローラ、ストレージ装置及びライトキャッシング方法

【課題】バックアップ電源の疲弊度に合ったライトキャッシュサイズを設定可能とする。

【解決手段】実施形態によれば、データバッファはホスト装置から転送されるデータを格納する。放電容量検出手段は主電源から供給される電力によって充電されるバックアップ電源の放電容量を検出する。時間算出手段は検出された放電容量に基づき、バックアップ電源からの電力供給によりライトキャッシング可能な第1の時間を算出し、且つデータバッファに格納されているメディアに未書き込みのデータをメディアにライトするのに要する第2の時間を算出する。判別手段は第1の時間と第2の時間とに基づき、第1の時間内に未書き込みデータをメディアにライト可能であるかを判別し、ライト可能なら、ホストにライト完了のレスポンスを送信する。メディアコントローラは、ライト完了のレスポンスが送信された後、データバッファ内の未書き込みデータをメディアにライトする。

(もっと読む)

電子制御装置

【課題】2つのマイコンを備えた電子制御装置にて、電源オフ要求の発生後に、各マイコンが不揮発性メモリへのデータ書き込みを確実に実施可能にする。

【解決手段】メインマイコン(以下、メイン)は、車両のIGスイッチのオフを検知すると、サブマイコン(以下、サブ)へ処理移行命令を出力する(A)。サブは、処理移行命令を受け取るとシャットダウン処理に移行し、メインに移行完了通知を出力する(B)。そしてサブは、シャットダウン処理の中でサブ側のフラッシュメモリにデータを書き込む。一方メインは、上記移行完了通知を受け取ると、シャットダウン処理へ移行し(C)、そのシャットダウン処理の中でメイン側のフラッシュメモリにデータを書き込む。更に、サブは、シャットダウン処理が完了するとメインに処理完了通知を出力し(D)、メインは、自分側のシャットダウン処理が完了し且つ上記処理完了通知を受け取ると、電源遮断の処理を行う(E)。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】省エネ復帰時間を短縮しながらハングアップすることなく確実に復帰させることを目的とする。

【解決手段】省エネモード中の電源を監視して(100)、閾値以上の電圧が検出された場合には、省エネ復帰から通常復帰に切り換えて、メモリに記憶された展開情報を利用せずに、メモリを初期化して新たに情報を展開して復帰する通常復帰が行われるように制御し(104〜112)、閾値以上の電圧が検出されない場合にはメモリに記憶された展開情報を利用する省エネ復帰が行われるように制御する(104)。

(もっと読む)

情報記憶装置および情報記憶方法

【課題】記憶部に半導体メモリを利用する情報記憶装置において、情報の記憶に利用できない記憶領域の発生を抑制すること。

【解決手段】本実施形態にかかる情報記憶装置は、半導体メモリと、管理手段と、を具備して構成される。この半導体メモリは、情報を記憶するための記憶領域を有する。また、管理手段は、半導体メモリの記憶領域のうちリードエラーの発生する回数が2以上となった記憶領域を情報の記憶の利用から除外するように管理する。

(もっと読む)

情報処理装置、情報処理方法、及び情報処理プログラム

【課題】よりセキュリティを向上しつつ、正常でないBIOSによる起動を抑止すること。

【解決手段】本発明にかかる情報処理装置9は、BIOS(Basic Input/Output System)910が予め格納されたBIOS記憶部91と、正常なBIOS910のデータと予め任意の値に定められた付加データとを含む合成データの誤り検出符号920を予め格納する符号記憶部92と、BIOS記憶部91に格納されたBIOS910を起動するときに、BIOS910のデータと付加データとを含む合成データの誤り検出符号を生成し、生成した誤り検出符号と符号記憶部92に格納された誤り検出符号920とを比較して、それらの誤り検出符号が一致しなかった場合、BIOS910の起動を抑止する管理部93とを備える。

(もっと読む)

情報処理装置および方法、並びに記録媒体

【課題】データの記録方式などが用途に応じて最適になるようにする。

【解決手段】記録媒体に記録されるデータの特性であって、当該データの保持期間を表す寿命値および当該データを読み出したときに発生すると想定されるエラーの割合を表すエラーレートを含む特性に基づいて、前記記録媒体により構成される論理デバイスの記録領域を複数生成するとともに、前記記録領域のそれぞれに適用される記録方式を決定する記録方式決定部と、前記決定された記録方式に基づいて、前記論理デバイスの記録領域のそれぞれを初期化する論理デバイス初期化部とを備える。

(もっと読む)

メモリ電圧制御装置およびメモリ電圧制御方法

【課題】メモリを低電圧で制御して省電力制御を図ることおよびエラーの発生を防止することを改善できるメモリ電圧制御装置およびメモリ電圧制御方法を提供する。

【解決手段】メモリ電圧制御装置10およびメモリ電圧制御方法は、デバイス13,14と、デバイス13,14の異常を検出する電気機器11と、を備え、電気機器11は、デバイス13,14の異常を検出した時に、デバイス13,14に対して動的または静的に駆動電圧を昇圧する制御を行う。

(もっと読む)

メモリシステム

【課題】高品質なメモリシステムを提供する。

【解決手段】メモリシステム1は、データ保持可能な不揮発性の半導体記憶部2と、半導体記憶部2の温度を計測する温度計測部9a、9bと、半導体記憶部2の温度を変化させる温度可変部8と、ホスト機器11から受信したデータを半導体記憶部2に転送する転送部、温度計測部9a、9bからの温度情報を記憶する温度記憶部、及び温度記憶部に記憶された温度情報に基づいて、温度可変部8を制御する温度制御部を具備する制御回路5と、を具備する。

(もっと読む)

情報処理装置、画像形成装置およびプログラム

【課題】プログラムの誤動作の発生を抑制する。

【解決手段】動作制御部は、プログラムを実行するCPUと、プログラムを格納するとともにプログラムの実行に伴って発生するデータを格納するメインメモリ512とを有している。メインメモリ512は、読み書き可能であって、電源を供給しなくても、記憶している情報を保持することが可能なMRAM61と、電源を供給しないと、記憶している情報を保持することができないDRAM62とを備えており、MRAM61の一部領域にはプログラム等が格納されるROM領域A1が設けられ、MRAM61の残りの領域およびDRAM62のすべての領域にはデータ等が格納されるRAM領域A2が設けられる。CPUがリセットされると、ROM領域A1の記憶内容をそのままとする一方でRAM領域A2の記憶内容を消去し、ROM領域A1から読み出したプログラムを実行する。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

電源回路、その電源回路を有するフラッシュメモリシステム、及び電源供給方法

【課題】フラッシュメモリと該フラッシュメモリに対するアクセスを制御するメモリコントローラに動作電圧を供給する電源回路が有する電圧調整回路の出力側の充電手段の充電電圧を規定時間内に下げる。

【解決手段】フラッシュメモリと該フラッシュメモリに対するアクセスを制御するメモリコントローラに動作電圧を供給する電源回路は、外部から供給される入力電圧によって充電される充電手段である入力充電手段と、入力電圧と入力充電手段の充電電圧のいずれか高い方の電圧を動作電圧に調整して出力する電圧調整手段と、動作電圧によって充電される充電手段である出力充電手段と、入力電圧と充電電圧のいずれか高い方の電圧が設定値より低くなったときに出力充電手段に充電されている電荷を放電させる放電手段とを備える。

(もっと読む)

ICチップ、ICチップにおける処理方法、及びICチップ用処理プログラム

【課題】処理中断によりトランザクションが行われた場合であっても、処理時間制約が厳しい方のインターフェイスを用いた処理を正常に行うことが可能なICチップ、ICチップにおける処理方法、及びICチップ用処理プログラムを提供する。

【解決手段】ICチップは複数のインターフェイスに対応した処理手段と、データを記憶するデータ記憶領域と前記データをバックアップするためのバックアップ領域と、を有する不揮発性メモリと、第1の前記インターフェイスを用いた処理により受信されたデータを前記データ記憶領域に書き込む際に前記データ記憶領域に記憶されているデータを前記バックアップ領域にバックアップし、前記第1の前記インターフェイスを用いた処理が中断された場合には、前記バックアップ領域にバックアップされている前記データを前記記憶領域に書き戻す処理を行う制御手段と、を備える。

(もっと読む)

半導体集積回路、半導体装置およびリモートコントローラ

【課題】マイクロコンピュータがストップ状態であり、キャパシタによって電源電圧がマイクロコンピュータに供給されている場合、マイクロコンピュータのストップ状態を維持する。

【解決手段】検出回路(3)は、外部キャパシタ(C1)を放電させる外部キャパシタ放電回路(30A)と、電源電圧を保持する内部キャパシタ(C2)と、内部キャパシタを放電させる内部キャパシタ放電回路(30)と、比較器(32)と、出力回路(33)とを有する。比較器は、放電後の外部キャパシタの第1電圧(VC1)を、放電後の内部キャパシタの第2電圧(VC2)と比較する。比較の結果、出力回路は、第1電圧が第2電圧よりも低い場合、マイクロコンピュータが外部キャパシタから電源電圧の供給を受けていることを示す検出信号(S2)を出力する。割り込み回路(4)は、その検出信号を受けた場合、割り込み信号(SI)を出力しない。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

21 - 40 / 1,341

[ Back to top ]