Fターム[5B046BA05]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049) | 割付、配置、ネスティング (289)

Fターム[5B046BA05]に分類される特許

81 - 100 / 289

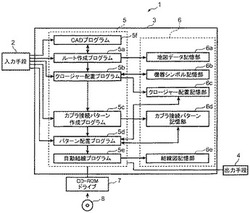

光ケーブルの芯線自動接続プログラムおよび芯線自動接続システム

【課題】クロージャー内の芯線接続を効率的で自動的に行う光ケーブルの芯線自動接続プログラムを提供する。

【解決手段】光ケーブル敷設の地図を記憶する地図データ記憶部6aと、上記地図を画面上に出力する出力手段4と、上記地図上に光ケーブルの敷設ルートを作図する入力手段2と、光ケーブルを接続する接続機器、カプラ等のシンボルを記憶する機器シンボル記憶部6bと、カプラ接続パターンを記憶するカプラ接続パターン記憶部6dと、カプラ接続パターンを上記画面上に表示させ、入力手段を介しルート上に接続機器を配置すると共に、表示されているカプラ接続パターンのカプラを接続機器に対して割り付けた際に、自動結線処理プログラム5eを用い、カプラ接続パターンに従い、光ケーブル敷設ルート始点側の接続機器からその接続機器内に配置されたカプラシンボルに光ケーブルの芯線を接続する接続処理部3を備える。

(もっと読む)

半導体集積回路装置の設計方法およびプログラム

【課題】階層化レイアウト処理の簡略化を図ることにより、半導体集積回路装置のレイアウト設計にかかる期間を大幅に短縮する。

【解決手段】トップTPに属する回路とブロックBKの信号端子D1との間に信号配線Aの接続が必要となるが、ブロックBK内のほかの配線、また、他のブロックに接続されるトップTPの配線の混雑具合により、既に決められているブロックの信号端子位置に信号配線Aが接続できない、または大きく迂回が必要など最適とはいえない場合がある。そこで、ブロックBKの信号端子D1の位置情報に影響されることなく信号配線Aを接続できるように、信号配線Aの接続処理以前に信号端子の位置情報を削除する。また、トップTPの回路をブロックBKの境界より内側に配置し、信号配線Aが最適に接続できる場合もあるので、信号端子の位置情報と同じくブロックBK境界の位置情報も削除する。

(もっと読む)

半導体集積回路装置およびその設計方法

【課題】オフリーク電流を抑制でき、動作速度および駆動力に優れた半導体集積回路装置およびそのような半導体集積回路装置の設計方法を提供する。

【解決手段】スタンダードセルを配置して動作タイミングおよび消費電力の少なくともいずれかを解析し、得られた解析結果に基づいて特性の改善が望まれるスタンダードセルを着目セルとして特定し、ウェル近接効果の影響を考慮して前記着目セル周辺の空き領域の配置および形状を最適化し、最適化された空き領域のうち、ウェル近接効果を利用できる空き領域を特定し、特定された空き領域のレイアウト、または特定された空き領域および前記着目セルのレイアウトを、所望の特性に応じてウェル近接効果の影響が変動するように変更する。

(もっと読む)

三次元集積回路の設計装置、三次元集積回路の設計方法およびプログラム

【課題】論理モジュールチップとメモリアレイチップとから成る三次元集積回路を高性能に実現する設計装置を提供する。

【解決手段】設計装置100は、論理モジュールに関する論理モジュール情報を入力する入力部101と、論理モジュール情報に基づいて、メモリブロックの構成を示すメモリブロック構成情報を生成するメモリブロック構成部103と、論理モジュール情報に基づいて論理モジュールを論理モジュールチップ上に配置する論理モジュール配置部102と、メモリブロック構成部103により生成されたメモリブロック構成情報に基づいて、メモリアレイチップに実装される複数のメモリエレメントにメモリブロックを割り当てるメモリブロック割当部104と、論理モジュールの配置とメモリブロックの割当とを設計結果として出力する出力部105と、を備える。

(もっと読む)

回路基板設計装置、回路基板設計方法および回路基板設計プログラム

【課題】 本発明は回路基板の設計に関し、より詳細には回路基板に部品を配置する回路基板設計装置、回路基板設計方法および回路基板設計プログラムに関するものである。

【解決手段】 本発明の回路基板設計装置は、ボディ形状情報とピン領域情報とを格納した部品情報DBと、部品の配置情報を格納した配置情報DBと、配置対象部品の近傍の部品を抽出する近傍部品抽出手段と、配置対象部品のピン領域に最も近い距離にある近傍部品のピン領域を抽出する干渉対象抽出手段と、配置対象部品の投影領域を算出し、投影領域と近傍部品のピン領域との干渉をチェックする第1の干渉チェック手段と、近傍部品の投影領域を算出し、投影領域と配置対象部品のピン領域との干渉をチェックする第2の干渉チェック手段と、第1と第2の干渉チェック手段で干渉がない場合に配置可とする配置判定手段、を備えるよう構成する。

(もっと読む)

建物の壁構造設計支援システム

【課題】制震壁の配置決定を自動で行い設計者の作業負荷を軽減する。

【解決手段】間取り図データ中の制震壁の設置適合領域を判定する領域判定手段と、間取り図中で必要な数の制震壁を配置する位置を探索して、その位置情報を自動的に取得する探索手段とを備える。間取り図の図心を原点とし、壁線に平行なX軸とY軸とからなる直交座標を設定して、最外周線に近い場所から壁線を辿って制震壁の配置を決めるので、各制震壁の間の距離をできるだけ離すように自動配置できる。また、第1象限、第3象限、第2象限、第4象限という順番で制震壁の配置を決めるので、全ての制震壁を原点に対して可能な限り対称な位置に配置することができる。

(もっと読む)

レイアウト設計方法

【課題】バンプによるスタック実装のためのチップ重ね合わせ配置を自動的に行うことのできるレイアウト設計方法を提供する。

【解決手段】LSI1のフロアプラン上にレイアウト済みのLSI2に配設されているバンプセルのミラー反転イメージをして、フロアプラン上でのバンプセルの配置位置座標を算出し、その配置位置座標にLSI2のバンプセルの接続先となるLSI1のバンプセルを配置し、そのバンプセルの配置位置に応じて、LSI1の機能セルの配置および配線を行う。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】セットアップタイミングの制約に違反しているデータパス内のセルを含むROW領域の消費電力値が低くなるようにセルを再配置して電圧降下の抑制化を図ること。

【解決手段】設計支援装置500は、セットアップタイミングの制約に違反しているデータパス内のセルを抽出部504により抽出し、データパス内のセルを含むROW領域を第1の特定部505により第1のROW領域に特定し、第1のROW領域内のセルから、データパス内のセルを除くセルを第1の決定部506により第1のセルに決定し、データパス内のセルを含まない第2のROW領域を第2の特定部509により特定し、第2のROW領域内のセルを第2の決定部509により第2のセルに決定し、第2のセルの消費電力値が第1のセルの消費電力値未満の場合、第1のセルと第2のセルの配置位置を置換部511により置換する。

(もっと読む)

半導体集積回路の設計方法及び回路設計装置

【課題】 本発明の課題は、配線混雑を防止しながらセルの配置領域の拡大を抑制することことを目的とする。

【解決手段】 上記課題は、配置アルゴリズムによって決定された配置領域と、該配置領域に配置される論理セル群を仮想的に配置する仮想的配置手順と、前記仮想的配置手順の結果に基づいて、該配置領域内に設定幅以下となる論理セルの集中箇所を検出する集中箇所検出手順と、前記集中箇所の配線指数を算出する配線指数算出手順と、前記配線指数が制限値以下の場合に、隣接制約に基づいて論理セル群の再配置を仮想的に行う隣接制約再配置手順と、前記隣接制約再配置手順による結果に基づいて実際に前記配置領域に前記論理セル群を配置する実配置手順とをコンピュータが実行することを特徴とする半導体集積回路の設計方法により達成される。

(もっと読む)

設計支援装置および設計支援プログラムおよび記録媒体

【課題】 プリント基板の設計工程を効率化して、電子機器の設計期間を可及的に短縮することができる設計支援装置を提供する。

【解決手段】 設計支援装置は、プリント基板を搭載するために前記プリント基板に対して要求される制約条件が異なる複数の電子機器に、前記プリント基板を共通して搭載するためのプリント基板に関する設計データが記憶される設計データ記憶手段と、前記複数の電子機器毎の各制約条件を、それぞれデータ化した制約条件データが記憶される制約条件データ記憶手段と、前記制約条件データ記憶手段に記憶される複数の制約条件データから共通する共通制約条件データを生成する共通制約条件データ生成手段と、前記プリント基板の設計データと前記共通制約条件データとに基づいて、該プリント基板の設計データが全ての制約条件を満足しているか否かを判定する判定手段とを備える。

(もっと読む)

プリント基板設計支援プログラム、方法及び装置

【課題】プリント基板の設計システム上で、どのパスコンがどのIC・電源端子に、どの程度の度合いで電流供給をするのかを明確に判定できるようにする。

【解決手段】外部記憶情報抽出部21でプリント基板のレイアウト情報を取得する。電源配線経路探索部22aで、レイアウト情報から半導体集積回路の電源端子を特定するとともに、電源端子に接続される部品端子及び配線により構成される電源配線経路を取得する。配線経路インダクタンス算出部22bで、電源配線経路に含まれる電源端子とバイパスコンデンサの端子との間の配線インダクタンスを算出する。IC・電源端子−パスコンペア設定部22cで、算出した配線インダクタンスを付与して、電源端子とバイパスコンデンサとのペアを設定し、保持する。これにより、配線インダクタンスに基づいて、パスコンの電流供給の関係を明確にすることができる。

(もっと読む)

レイアウト支援プログラム、レイアウト支援装置およびレイアウト支援方法

【課題】レイアウト済みのセルのタイミング関係を崩すことなく所望のセルを追加配置可能なレイアウトを行う。

【解決手段】あらたなセル(追加セル)を追加する際に、配置可能な空き領域が無い場合には、レイアウト済みのセルの中から、最も信号伝搬のタイミングに影響しないセルを、あらたなセルを配置するための空き領域を用意するための移動対象セルとして選択する。選択されたセルを移動させた空き領域にあらたなセルを配置することによって、追加セルの挿入に伴うタイミング調整を不要もしくは必要最低限に留めることができる。

(もっと読む)

半導体装置のレイアウト設計装置、方法及びプログラム

【課題】電源分離処理を行うと、チップサイズが増大する課題があった。

【解決手段】セルデータ格納部と、分離処理部とを具備する半導体装置のレイアウト設計装置によって解決できる。セルデータ格納部は、複数のセルが隣接して連続する構造を有する半導体装置における各セルのセルデータを格納する。分離処理部は、セルデータを処理し、複数のセルに亘って設けられるメタル配線を、半導体装置の設計基準に従って、セル間で分離する。分離処理部は、延伸・短縮部と、反転部とを備える。延伸・短縮部は、セルデータのそれぞれについて、メタル配線の一部であって、各セルのセル枠内に配置されるべきメタル部分の一端を延伸すると共に、他端を、一端を延伸した方向と同じ方向に短縮する。反転部は、延伸・短縮部によって、延伸され及び短縮されたメタル部分を有する任意のセルを、延伸された一端と、短縮された他端とが入れ替わるように、ミラー反転する。

(もっと読む)

例外的条件の管理及び表示を含むソーラーコレクタ自動設置設計

実施形態は、設置現場の表示を生成及び編集し、様々なデータオブジェクトを生成し、オブジェクトを、付随する特性及びレイアウト制限を伴う予め規定された"構造"の様々な種類として分類するシステム及び方法を含んでもよい。分類の一部として、又は分類に追加して、ある実施形態は、これらのオブジェクトに固有の特性又は付随する特性を生成、関連付け及び編集するシステム及び方法を含んでもよい。設計エンジンは、上記の構造に設計規則を適用して、1以上のソーラーコレクタ設置設計の代替案を生成してもよく、物理レイアウトのスクリーン表示及び/又は紙表示、又は、1以上の設計代替案の配置を生成することを含む。ある実施形態では、構造の分類及びユーザー入力の提供、レイアウトの生成及びレイアウトの修正のプロセスを含む、設計プロセスに関するメタデータが生成されてもよい。メタデータは、プロジェクト状態情報又は設計における例外的条件についての情報を含んでもよい。例外的条件に対応する例外のリストが生成されてもよく、設計者は、これらの例外とのインタラクションを様々な態様で行ってもよく、例えば、例外リストから項目を消去するべく規則に従う、又は、規則の適用を無効とすることによって、行ってもよい。例外は、その他のユーザーの動作を邪魔しない態様であってもよい。 (もっと読む)

異種設計設定を規定する機能を含むソーラーコレクタ自動設置設計

実施形態は、設置現場の表示を生成及び編集し、様々なデータオブジェクトを生成し、オブジェクトを、付随する特性及びレイアウト制限を伴う予め規定された"構造"の様々な種類として分類するシステム及び方法を含んでもよい。分類の一部として、又は分類に追加して、ある実施形態は、これらのオブジェクトに固有の特性又は付随する特性を生成、関連付け及び編集するシステム及び方法を含んでもよい。設計エンジンは、上記の構造に設計規則を適用して、1以上のソーラーコレクタ設置設計の代替案を生成してもよく、物理レイアウトのスクリーン表示及び/又は紙表示、又は、1以上の設計代替案の配置を生成することを含む。実施形態はまた、1以上の設計アパーチャを規定する段階を含み、設計アパーチャのそれぞれは、ユーザーが規定した設計設定の個別のセットに従ってソーラーコレクタがレイアウトされる境界に対応していてもよい。個別のアパーチャは、ユーザーが規定した設計設定に従って、コレクタレイアウトの異種の領域を提供してもよい。 (もっと読む)

半導体レイアウトシステム、方法、及び、プログラム

【課題】並行する回路ブロック間配線のリピータ挿入位置の重なりを抑制できる半導体レイアウトシステムを提供する。

【解決手段】配線情報記憶部201は、配線の始点座標及び終点座標を含む回路ブロック間配線の配線情報を記憶する。グループ化処理部21は、リピータ挿入対象の回路ブロック間配線のうちで、始点座標のX方向の座標又はY方向の座標の差が所定距離以内で、かつ、互いに並行して延びる配線部分を有する回路ブロック間配線をグループ化する。リピータ挿入基点決定部22は、同じグループに所属する回路ブロック間配線について、始点座標からの距離が相互に異なる位置の座標をリピータ挿入基点に決定する。リピータ挿入処理部23は、リピータ挿入基点を基点に、リピータ挿入対象の回路ブロック間配線に挿入するリピータセルの位置を決定する。

(もっと読む)

バージョン管理を含むソーラーコレクタ自動設置設計

実施形態は、設置現場の表示を生成及び編集し、様々なデータオブジェクトを生成し、オブジェクトを、付随する特性及びレイアウト制限を伴う予め規定された"構造"の様々な種類として分類するシステム及び方法を含んでもよい。分類の一部として、又は分類に追加して、ある実施形態は、これらのオブジェクトに固有の特性又は付随する特性を生成、関連付け及び編集するシステム及び方法を含んでもよい。設計エンジンは、上記の構造に設計規則を適用して、1以上のソーラーコレクタ設置設計の代替案を生成してもよく、物理レイアウトのスクリーン表示及び/又は紙表示、又は、1以上の設計代替案の配置を生成することを含む。ある実施形態は、特定の設置現場に対するソーラーコレクタレイアウト設計の複数のバージョンを表示、生成及び編集すること提供してもよい。複数のバージョンを使用することにより、代替レイアウト、代替構造分類、及び代替設計選択肢に対応するコスト及び性能のデータを分析することが可能になる。バージョン間の比較を複数の次元にわたって表示することを提供するバージョン概要情報を提供してもよい。 (もっと読む)

LSIのセル配置位置情報変更プログラム及び方法

【課題】レジスティブネットワーク方式を用いて品質のよい配置結果を得られるようにすること。

【解決手段】コンピュータに、チップ上に設けられる複数のセルそれぞれの配置位置を示す情報と、前記複数のセルにおけるセル間の接続関係を示す情報とに基づいて、前記複数のセルそれぞれに対して前記複数のセルそれぞれに対応する前記配置位置から引力が生じるとして、レジスティブネットワーク方式により前記複数のセルの再配置位置を求める処理を実行させる。

(もっと読む)

集積回路設計装置、設計方法およびプログラム

【課題】 スキャンパスの端子位置として、スキャンパス総配線長を短縮するための最適な配置位置を得られない。

【解決手段】 レイアウト情報を参照して各マクロのスキャンイン端子およびスキャンアウト端子の仮配置位置の決定を行い、当該決定に基づいてレイアウト情報を更新し、スキャンイン外部端子および複数のマクロについて、更新されたレイアウト情報とスキャンパス接続情報とを参照して、スキャンイン外部端子を始点に順次最も近い距離に配置されているマクロを接続するようにスキャンパス接続情報を更新し、更新されたレイアウト情報と更新されたスキャンパス接続情報とを参照して、スキャンパス総配線長が最も短くなるようにスキャンパス接続順の決定を行い、当該決定に基づいて更新されたスキャンパス接続情報をさらに更新するスキャンパス付替部とを有する。

(もっと読む)

半導体集積回路のレイアウト設計装置および半導体集積回路のレイアウト設計方法、制御プログラム、可読記録媒体、半導体集積回路

【課題】大規模特殊マクロセルのコーナー部近辺の配線を更に高密度に行い、チップサイズを更に縮小しかつチップコストをも低減する。

【解決手段】大規模特殊マクロセル2〜4とスタンダードセルを含む半導体集積回路において、大規模特殊マクロセル2〜4のコーナー部近辺(コーナー領域)の配線を、水平配線および垂直配線をコンタクトを設けることなく同一層で効率よく平行に配置した水平・垂直配線乗換え専用セル5を用いることにより、大規模マクロセル2〜4のコーナー部近辺の配線を更に高密度に行う。

(もっと読む)

81 - 100 / 289

[ Back to top ]