Fターム[5B046BA05]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049) | 割付、配置、ネスティング (289)

Fターム[5B046BA05]に分類される特許

121 - 140 / 289

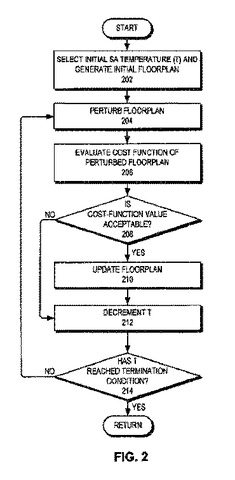

3DICのためのフロアプランニングを容易にするための方法およびシステム

本発明の一つの実施形態は、3次元集積回路(3D IC)に対するフロアプランニングを容易にするシステムを提供する。動作中に、上記されたシステムは、複数の回路ブロックを受容する。上記のシステムは、マルチレイヤダイ構造の少なくとも1つのレイヤにおいてブロックを配置し、時間変動するパラメータの初期値を設定する。次いで、上記システムは、時間変動するパラメータが所定の値に達するまで、ブロック配列を反復して摂動する。  (もっと読む)

(もっと読む)

順序セルを接近配置する方法及び装置

【課題】集積回路ネットリストの順序セルの接近配置に関連した方法及び装置を提供する。

【解決手段】予備配置が受け取られ、その予備配置に基づいて、その後の配置の際に、改善された電力及び/又はタイミングを受ける順序セルのグループが識別される。別の例では、その後の配置の際に、改善された電力及び/又はタイミングを受ける順序セルのグループの識別が受け取られ、そしてその識別されたグループの順序セルの接近配置が行われる。更に別の例では、順序セルのグループの接近構成が受け取られ、接近配置が失敗した場合に、順序セルのグループが解散され、その解散されたグループの順序セルの配置が行われる。

(もっと読む)

集積回路設計方法及び集積回路設計装置

【課題】処理負荷の増大を抑えながら、所定のマクロブロック周辺において複数の配線の影響を確実に低減できる集積回路設計方法及び集積回路設計装置を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより大きく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

集積回路設計方法、集積回路設計装置、集積回路及び電子機器

【課題】処理負荷の増大を抑えながら、これまで配線が混雑していた領域でも確実にセルや配線を配置できる集積回路設計方法等を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより小さく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

動的アレイアーキテクチャにおけるセル位相整合及び配置の方法及びその実施

半導体チップは、レイアウト特徴部が第1の仮想格子に従って配置される第1のチップレベルと、レイアウト特徴部が第2の仮想格子に従って配置される第2のチップレベルとを有する論理ブロック区域を含むように定められる。第1の仮想格子と第2の仮想格子の間には、有理空間的関係が存在する。論理ブロック区域内には、複数のセルが配置される。複数のセルの各々は、複数のセル位相のうちの適切な1つに従って定められる。複数のセル位相のうちの適切な1つは、所定の配置セルの第1及び第2のチップレベル内のレイアウト特徴部を所定の配置セルに位置決めされた第1及び第2の仮想格子と整合させる。 (もっと読む)

半導体集積回路の設計方法と設計装置並びにプログラム

【課題】スタンダードセルの設計方式を用いて、品質の高いレイアウトを、短時間で作成することを可能とする設計方法と装置の提供。

【解決手段】

回路図情報(11)を入力し、回路図情報に対してセルの相対的な配置順序を自動的に決定し(12)、前記回路図情報に付与された配置順序に従ってセルを相対的な位置関係に自動配置する(13)。

(もっと読む)

半導体集積回路並びにその設計方法及び設計プログラム

【課題】IRDropやEMIの低減等が可能な半導体集積回路の設計方法等を提供する。

【解決手段】この半導体集積回路の設計方法は、複数のリーフセルを複数のグループにグループ分けするステップと、複数のグループの各々に対して、クロック信号の入り口としての代表セルを設けるステップと、複数のグループの各々に対して、代表セルとリーフセルの各々との間のクロック信号の遅延が略同等になるように、代表セル及びリーフセルをグループ配置領域内に配置するステップと、複数のグループをレイアウト領域内に配置するステップと、複数のグループにクロック信号を供給するためのクロックルートセルと複数のグループ内の代表セルとの間にクロックツリーシンセシスを行うステップと、を含む。

(もっと読む)

半導体集積回路の設計方法

【課題】チップ内におけるIRドロップの最大値とばらつきを低減できる半導体集積回路の設計方法を提供する。

【解決手段】本発明の半導体集積回路の設計方法は、複数のセルの接続関係を示すネットリストに基づいて、セットアップタイミング条件を満たすように複数のセルをセル配置領域に仮配置するステップと、セル配置領域を複数に分ける複数のパワーリージョンを生成するステップと、各セルごとの消費電流を示したセルパワーファイルを用いて各パワーリージョンごとの消費電流を算出するステップと、セットアップタイミング条件の違反にはならない範囲で、各パワーリージョンの消費電流を参照して、仮配置されたセルの配置位置を調整するステップとを有する。

(もっと読む)

トランジスタ自動配置装置、方法及びプログラム

【課題】レイアウト面積を削減することができるトランジスタ自動配置装置を提供すること。

【解決手段】トランジスタ自動配置装置30は、生成手段31と配置手段32とを備える。生成手段31は、回路接続情報に基づいて互いに隣接するように配置された第1及び第2のハードマクロ・トランジスタの拡散領域の電位が等しい場合には、第1のハードマクロ・トランジスタにおける不要な拡散領域及び/又は不要なコンタクトを削除した第1のプログラマブル・トランジスタを生成するとともに、第2のハードマクロ・トランジスタにおける不要な拡散領域及び/又は不要なコンタクトを削除した第2のプログラマブル・トランジスタを生成する。配置手段32は、第1及び第2のプログラマブル・トランジスタを回路接続情報に基づいて配置する。

(もっと読む)

マザーボードの端子配置方法

【課題】複数の電気信号が入出力される装置内において、入出力端子間または、信号間で発生するクロストークの影響で信号にノイズが発生する。その際に、送信した信号波形に対して、受信側で劣化した波形が再生される、または正常な波形を再生できないといった課題がある

【解決手段】そこで本発明は基板上で仮配置された信号端子において、隣接する信号端子間の信号強度差の総和値を算出し、仮配置ごとに算出される総和値の中で最小となる総和値を得た仮配置を本配置として決定することを特徴とする信号端子の配置方法を提供する。

(もっと読む)

半導体集積回路の設計方法、半導体集積回路の設計プログラム、及び半導体集積回路の設計支援装置

【課題】多くの種類のキャパシタセルを準備せずに、ノイズ低減に必要な容量を半導体集積回路に追加する。

【解決手段】本発明による半導体集積回路の設計支援装置は、DRC部と、修正部とを具備する。DRC部は、キャパシタセルにおける内部配線のレイアウト情報と、設計対象の半導体集積回路における信号配線のレイアウト情報とを参照してデザインルールチェック(DRC)を行う。修正部は、DRC部がエラーと判定した場合、内部配線のレイアウト情報を半導体集積回路における信号配線のレイアウト情報に統合する。又、修正部は、統合されたレイアウト情報から、内部配線におけるエラー箇所を削除する。

(もっと読む)

車両用制御ユニット設計支援装置及び方法

【課題】 コストを考慮しつつ制御ユニットのレイアウトを決定する。

【解決手段】 制御ユニットそれぞれを複数の搭載位置のいずれかに配置するレイアウトを決定するための車両用制御ユニット設計支援装置であって、各制御ユニットについて搭載可能な搭載位置の情報を記憶した搭載可能位置記憶手段と、各搭載位置について該搭載位置に制御ユニットを搭載したときに発生するコストを記憶したコスト記憶手段と、搭載可能位置記憶手段が記憶する搭載可能位置に基づいて可能なレイアウトを抽出するレイアウト抽出手段と、各レイアウトについて該レイアウトにしたがって複数の制御ユニットそれぞれを対応する搭載位置に搭載することにより発生する総コストを、コスト記憶手段が記憶するコストに基づいて算出する総コスト算出手段と、総コスト算出手段が算出した総コストの順位に基づいてレイアウト抽出手段が抽出したレイアウトを順序付けて表示する表示手段とを有する。

(もっと読む)

分岐角度設計支援装置、分岐角度設計支援方法、及び、分岐角度設計支援プログラム

【課題】ワイヤハーネスの組み付け性及び耐久品質を向上する。

【解決手段】ワイヤハーネスにおける分岐点の分岐角度の設計を支援する分岐角度設計支援装置であって、ワイヤハーネスの経路を示す経路情報を取得する経路情報取得手段11aと、ワイヤハーネスの回路を示す回路情報を取得する回路情報取得手段11bと、複数の電線の各々の端末に基づいて前記取得した経路情報と前記回路情報とを関連付け、該関連付けた情報から平面レイアウトにおける前記複数の電線の各々の電線経路を計算する電線経路計算手段11cと、前記計算した複数の電線経路に基づいて前記ワイヤハーネスの分岐点における前記電線の各々の流れを表示するための分岐点情報を作成する分岐点情報作成手段11dと、前記作成した分岐点情報を、前記分岐角度の設計を支援するために出力する分岐点情報出力手段11eと、を有する。

(もっと読む)

配線レイアウト装置、配線レイアウト方法及び配線レイアウトプログラム

【課題】従来のレイアウト方法では、ノイズ低減させながら配線の収容性を向上させることができなかった。

【解決手段】本発明の配線レイアウト装置は、情報格納部20と、実配線トラックを設定する実配線トラック設定部11と、回路素子を配置する素子配置部12と、隣接する実配線トラックの間に仮想配線トラックを設定する仮想配線トラック設定部13と、第1の配線が接続される回路素子の端子を隣接する仮想配線トラック上に移動させる端子配置変更部14と、実配線トラック上の端子間を実配線トラックに沿って第2の配線で接続し、仮想配線トラック上の端子間を仮想配線トラックに沿って第1の配線で接続する配線部16と、第1の配線と第2の配線とが隣接して配置される隣接区間の長さを計算する隣接配線区間長算出部18と、隣接区間の長さが短くなる側の実配線トラック上に片側隣接禁止配線を移動させる配線形状変更部19と、を有する。

(もっと読む)

部品配置配線装置、部品配置配線方法及び部品配置配線プログラム

【課題】最適な配置と配線設計を協調的に行い、現実的な時間で最適解を探索する。

【解決手段】部品配置配線装置は、設計条件を受け付ける条件入力手段と、部品を無作為に配置すると共に、設計条件に基づいて配線する無作為配置配線手段と、部品を計算された釣り合い位置に基づいて、部品の配置を決定する位置計算配置手段と、配置が決定された部品に対し、配線の交差の解消を行うと共に、部品をクラスター化する交差解消部品クラスター化手段と、全ての部品がクラスター化されたか否かを判定する部品判定手段とを備える。部品判定手段は、まだクラスター化されていない部品が残っている場合には、まだクラスター化されていない部品に対し、位置計算配置手段と交差解消部品クラスター化手段とによって配置配線とクラスター化を行い、全ての部品がクラスター化された場合には、配置配線を終了することを特徴とする。

(もっと読む)

半導体装置、容量値算出方法

【課題】デカップリング容量が占める領域が最適化された半導体装置を提供すること。

【解決手段】半導体装置21は、第1電源線LHと第2電源線LLとの間に接続されたインスタンス32a〜32cと、第1電源線LHと第2電源線LLとの間に接続されたデカップリング容量33とを有する。インスタンス32a〜32cには、信号が伝播される配線LSが接続されている。デカップリング容量33の容量値は、配線LSにおける入力信号の変化から出力信号の変化までの期間に依存する許容遅延変動量と、第1電源線LHと第2電源線LLとの間の電圧に依存する許容電圧変動量に基づく容量値である。

(もっと読む)

部品配置設計支援装置及び方法

【課題】部品が高密度に実装されている場合において、部品を好適に配置するための指針を与える部品配置設計支援方法を提供する。

【解決手段】互いの距離に制限が課された複数の部品を配置するための指針を与える部品配置設計支援方法であって、(a)第1の部品からの距離について制限が課された第2の部品の配置可能領域を決定する工程(ステップS11)と、(b)前記配置可能領域に第3の部品が含まれるか否かを判定する工程(ステップS12)と、(c)第3の部品が含まれると判定された場合には、第3の部品の配置を変更するための指針を与える工程(ステップS13)と、を含む。

(もっと読む)

リピータ回路、リピータ回路設計装置、リピータ回路設計プログラムおよびリピータ回路設計方法

【課題】複数の電源電圧条件下であっても適切な遅延をおこなうリピータ回路を提供する。

【解決手段】リピータ回路100は、複数の電源電圧条件下で利用される設計対象回路に搭載され、電源電圧条件ごとに前記設計対象回路を流れる信号の伝送タイミングを遅延させるリピータが挿入された複数の伝送路110、120と、設計対象回路を動作させる電源電圧条件に応じて、前記複数の伝送路の中からいずれか一つの伝送路を選択して当該伝送路に前記信号を伝送させる伝送制御部130とを備える。

(もっと読む)

ソフトマクロを用いたレイアウト設計方法、ソフトマクロのデータ構造及びソフトマクロライブラリの作成方法

【課題】チップの面積増大を抑制し、また、チップレイアウト時のタイミング収束のために繰り返しレイアウトする回数と設計工数を削減する。

【解決手段】相対的な位置が決まっている複数の相対配置位置決定済セル(43)(44)を示す相対配置位置決定済セル情報(31)と、相対的な位置を示す相対位置情報(32)と、複数の相対配置位置決定済セル(43)(44)に対応して配置位置が決まっている配線(45)を示す配置位置決定済配線情報(33)(34)とを有するソフトマクロ(14)を構成する。そして、ネットリスト(11)に基づいて、ICチップにおける配置位置と配線とを決定するときに、相対配置位置決定済セル(43)(44)と配線(45)のレイアウトを変更しないソフトマクロ(14)を構成する。

(もっと読む)

集積回路設計装置

【課題】集積回路を設計するための集積回路設計装置に関し、集積回路の設計を効率よく行える集積回路設計装置を提供することを目的とする。

【解決手段】本発明は、チップ領域を分割した領域である複数の実装ブロック毎に、実装ブロックを分割した仮想配置領域であるコートを入力手段により設計者から設定し、配置することにより集積回路の設計を行う集積回路設計装置であって、コートをいずれかの実装ブロックに配置するブロック配置処理部と、論理回路を機能毎にまとめたブロックである機能ブロックを、実装ブロック上に配置されたコート上に配置する領域割付処理部と、実装ブロックにおけるコートの配置状態を評価するブロック評価処理部とを有し、評価処理部は、機能ブロックの面積が実装ブロックに配置されたコートの面積に占める割合を算出し、算出された機能ブロックとコートとの面積の割合をコート毎に図形により表示する。

(もっと読む)

121 - 140 / 289

[ Back to top ]