Fターム[5B046BA06]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049) | ルート探索、配線 (682)

Fターム[5B046BA06]に分類される特許

1 - 20 / 682

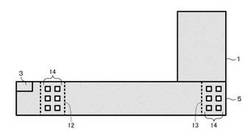

ダミーパターンの設計方法

【課題】金属配線パターンの寄生抵抗を低減可能なダミーパターンの設計方法を提供する。

【解決手段】切り欠きパターン2を一及び逆方向に各所定値Δx1だけ縮小して縮小図形4を生成した後、各所定値Δx1だけ拡大してダミーパターン5を生成し、その外形を抽出して矩形図形6を生成した後、各所定値Δx1だけ縮小して縮小図形7を生成し、ダミーパターン5から縮小図形7を論理減算して切り欠き図形8及び矩形図形9を生成し、切り欠き図形8を抽出してダミーパターン5から論理減算して矩形図形10を生成した後、各所定値Δx1だけ縮小して縮小図形11を生成し、矩形図形10から縮小図形11を論理減算して第1,第2のビア配置領域12,13を生成し、各ビア配置領域12,13にビア14をそれぞれ配置する。

(もっと読む)

設計支援装置

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

配線設計支援装置,配線設計支援プログラムおよび配線設計支援方法

【課題】配線設計に際し配線や配線容量の検討を高速かつ厳密に行なえるようにする。

【解決手段】配線経路生成部11が、2つの部品の各部品端子から各部品外部へ引出線を配線する処理に先立ち、2つの部品間で複数の信号線が配線される配線領域を概略的に示す配線経路を生成し表示部40に表示させる。配線経路生成部11によって配線経路が生成されると、詳細配線生成部12が、配線経路と配線規則とに基づき、各信号線を配線経路に沿って配線した詳細配線を生成し配線経路とともに表示部40に表示させる。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

設計データの補正方法、設計データの補正方法のプログラムを含む記憶媒体、及び、フォトマスクの製造方法

【課題】半導体デバイスの設計データの補正の効率化を図る。

【解決手段】本実施形態の設計データの補正方法は、半導体デバイスの配線レイアウトを示す第1の設計データに対して、変換差予測点が設定された第1のラインパターンとそれに隣接する第2のラインパターンとの開口角モデルを作成するステップ(ステップST1)と、開口角モデルに基づいて第1及び第2のラインパターンのライン幅及び間隔の少なくとも一方を補正し、前記第1の設計データを、補正された前記第1及び第2のラインパターンを含む第2の設計データに補正するステップ(ST2,ST3,ST4)と、を含む。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリーにおけるクロックスキューの調整において、精度の確保とデューティ保持とを両立させる。

【解決手段】レイアウト装置(10)において、MOSトランジスタ1段で形成された第1セルと、MOSトランジスタ複数段で形成された第2セルとがライブラリ化されたテーブルを設ける。また、上記レイアウト装置には、上記第1セルと上記第2セルとの組み合わせによるコンビネーションチェーンを上記クロックツリーに挿入することで、上記クロックツリーにおける異なるクロック系統間のクロックスキューを調整可能な演算処理部(12)を設ける。上記コンビネーションチェーンによってクロックスキューの調整を行うことで、個々の第1セルでの遅延誤差が伝播されるのを抑制し、遅延計算における遅延誤差の低減を図る。また、第1セルはMOSトランジスタ1段で形成され、そこで論理反転されるため、デューティ保持の観点で有利とされる。

(もっと読む)

解析プログラム、解析方法、および解析装置

【課題】解析対象回路全体のリーク電流解析にかかる計算量を減らした関数を提供すること。

【解決手段】変動関数L1は、解析対象回路100内に含まれるセルごとの、定数aおよび第1の重み係数bとセルに固有のリーク電流のばらつきを表す第1の確率変数αとによって表現される正規分布から得られる平均値と、解析対象回路100内のセル群で共通のリーク電流のばらつきを表す第2の確率変数βと第2の重み係数cとの乗算結果と、により表現されている。変動関数L1では、第1の確率変数αがないため、第1の確率変数αの値を所定回数乱数で発生させる分の計算量が削減される。解析装置は、変動関数L1に、セルごとに取得した定数aの値、第1の重み係数bの値、および第2の重み係数cの値を与えることで、第2の確率変数βの値により変動する解析対象回路100のリーク電流量の変動関数を生成する。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

配線の接続確認システム

【課題】大規模なシステムであっても、システムの設計者以外が単線単位で接続ルートを容易に特定できる配線の接続確認方法を提供する。

【解決手段】末端装置と、中継装置を介してケーブルにより接続され、かつ、ケーブルはコネクタを介して末端装置と、中継装置に接続されている配線構造における配線に対して、接続テーブルデータベースから読み出したコネクタとケーブルとの、及び、コネクタと、末端装置、及び、中継装置のいずれかとの、接続情報に基づき、指定された確認対象要素から接続情報を順次辿ることにより、その接続端までの接続ルートを特定する。

(もっと読む)

部品選択装置,方法及びプログラム

【課題】 部品選択装置において,標準部品から,設計対象の接続関係に最適な部品を抽出,及び抽出した部品の合致評価に関する情報を出力することを目的とする。

【解決手段】 部品選択装置1は,部品毎に端子間の内部接続関係を示す部品内部情報から分岐部品テーブル21を生成する分岐部品テーブル作成部11,設計対象の部品間の接続関係を示す配線情報から回路テーブル23を生成する回路テーブル作成部15と,部品内部情報の内部接続関係と前記配線情報の接続関係とを比較し,部品内部情報の内部接続情報が配線情報の接続関係と一致する部品を抽出する適合判定部17と,適合判定処理による合致評価情報6を出力する結果出力部19とを備える。

(もっと読む)

3次元コンピュータ設計支援プログラム、コンピュータ読取可能な記録媒体、3次元コンピュータ設計支援システム及び3次元コンピュータ設計支援方法

【課題】3次元CAD上にてフレキシブルフラットケーブルを適切に設計可能にする。

【解決手段】3次元コンピュータ設計支援プログラムCPRは、コンピュータによって、3次元仮想空間上にて配線設計されたフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲を演算する。また、この導体部が接続される終点側コネクタの向きを取得する。そして、終点側コネクタの向きが設計されたフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲内にある場合は接続可能と判定する。一方、終点側コネクタの向きがフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲内にない場合は接続不能と判定する。

(もっと読む)

局所優先方向アーキテクチャ、ツール、及び機器

【課題】「局所優先方向」配線モデルを使用してネットをルーティングするための機器を提供する。

【解決手段】本発明の一部の実施形態は、1つ又はそれよりも多くのEDAツール(プレーシング、ルーティングなどのような)と共に使用される「局所優先方向(LPD)」配線モデルを提供する。LPD配線モデルは、少なくとも1つの配線層が、各々が特定の配線層とは異なる優先方向を有する一組の領域を有することを可能にするものである。更に、各領域は、その組における少なくとも1つの他の領域の局所優先方向とは異なる局所優先方向を有する。更に、少なくとも2つの領域は、2つの異なる多角形形状を有し、その組における領域は、その組における別の領域を取り囲むことはない。

(もっと読む)

レイアウトパタン生成装置及びプログラム

【課題】デザインルールチェックの妥当性を正しく確認するために用いるレイアウトパタンを簡易に生成することができるようにする。

【解決手段】図形入力部24によって、半導体装置のレイアウトパタンについて予め定められた作図基準を満足するように生成されたOKパタンの入力を受け付ける。基準位置指定部28によって、OKパタンに対して、作図基準を満足している部分を基準箇所として指定する入力を受け付ける。検証パタン生成部34によって、OKパタンの基準箇所に対して、所定の変更を加えることにより、作図基準を満足しないNGパタンを生成する。

(もっと読む)

配線支援方法及び装置

【課題】配線すべき複数の信号線を、ユーザの指定する目的に従って適切にグループ化する。

【解決手段】配線すべき複数の信号線を複数のグループに分けるための方法は、ユーザから、複数の信号線のグループ化の条件の指定を受け付けるステップと、指定された、グループ化の条件と、データ格納部に格納されている、複数の信号線の始点端子群と終点端子群との配置パターンとに基づいて、複数の信号線のグループ化の処理を切り替えて実施する実施ステップとを含む。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

半導体集積回路の設計装置、及び半導体集積回路の設計方法

【課題】チップサイズを縮小することができる、半導体集積回路の設計装置、及び半導体集積回路の設計方法を提供する

【解決手段】下位階層の機能ブロック4に配置された複数のセル間を接続する第一の配線を設計する下位階層配線設計部311と、上位階層の機能ブロック間を接続する第二の配線を設計する上位階層配線設計部312とを備えており、下位階層配線設計部311は、機能ブロック4を複数の小領域4aに分割し、小領域4aごとに機能ブロック4内配線に必要となる必要配線層数Lnを算出して、最下部の配線層から必要配線層数Ln枚の配線層を配線可能領域として同領域内に第一の配線を配置し、上位階層配線設計部312は、第一の配線における配線可能領域以外の機能ブロック4の配線層に第二の配線を配置する。

(もっと読む)

集積回路の配線方法、集積回路の配線プログラム及びそれを記憶した記憶媒体

【課題】 要求性能を満たすとともに、消費電力を削減することができる配線方法を提供すること。

【解決手段】 本発明の実施形態による集積回路の配線方法は、所定の動作周波数を満たすように第1の配線を求め、前記所定の動作周波数と前記第1の配線のクリティカルパスとを用いて最大迂回配線長を算出し、集積回路の配線を複数の群に分けた場合に、配線群に含まれる前記第1の配線を、前記第1の配線を含む他の配線群内の配線を用いて迂回させることで第2の配線を求め、前記第2の配線と前記第1の配線との差分が前記最大迂回配線長以下ならば、前記第2の配線によって前記第1の配線を更新し、前記第2の配線と前記第1の配線の差分が前記最大迂回配線長よりも大きければ、前記第1の配線を更新しないことを特徴としている。

(もっと読む)

プリント基板設計支援装置およびプリント基板設計支援プログラム

【課題】プリント基板の実装設計において、部品および配線の要求特性を満たすように配線幅と配線長を決定し、必要な機能および性能を満たすプリント基板の、最適な設計を可能にする。

【解決手段】対象の回路の要求特性を満たすように、回路を構成する部品および配線の特性を考慮して、配線幅と配線長を決定する手段を備えるプリント基板設計支援装置により、達成できる。

(もっと読む)

1 - 20 / 682

[ Back to top ]