Fターム[5B057CH02]の内容

画像処理 (340,757) | 処理部 処理装置、処理システム (15,018) | 演算器 (6,373) | マルチプロセサ (674)

Fターム[5B057CH02]の下位に属するFターム

Fターム[5B057CH02]に分類される特許

41 - 60 / 245

画像処理装置、画像処理方法及びプログラム

【課題】複数の演算部から構成される制御部を用いて複数の処理を実行する画像処理装置において、演算部の処理待機時間を削減し、処理効率の向上を図ること。

【解決手段】複数のコアを有し、ページ記述言語データを解析してバンド単位の中間データを生成する解析処理、中間データに基づいてビットマップデータを生成する描画処理、を複数のコアに割り当てて実行する制御部を備えた画像処理装置において、複数のコアのうち少なくともいずれか一つは、解析処理及び描画処理が実行可能であり、当該コアは、解析処理又は描画処理のうちいずれか一方の処理の実行中に、当該実行中の処理が一時的に停止するイベントが発生した場合、他方の処理を実行する。

(もっと読む)

多重プロセッサを用いて状態情報を失わずにビデオ及び/又はグラフィクスデータを処理するための方法、システム及び装置

【解決手段】

方法、システム及び装置は、第1のグラフィクス処理回路及び第2のグラフィクス処理回路の組み合わせを用いるビデオ及び/又はグラフィクスデータの処理であって第1及び第2のグラフィクス処理回路の間で処理を転送する間に状態情報を喪失することのない処理を提供する。処理されるべきビデオ及び/又はグラフィクスデータは、例えば、ホストプロセッサ等のプロセッサ上で実行中のアプリケーションによって供給され得る。1つの例においては、装置は複数の単一命令多重データ(SIMD)実行ユニットを含む少なくとも1つのGPUを含む。GPUはネイティブ機能コードモジュールを実行するように動作する。装置はまた、第1のGPU上の複数のSIMD実行ユニットと同じプログラミングモデルを有する複数のSIMD実行ユニットを含む少なくとも第2のGPUを含む。更に、第1及び第2のGPUは同じネイティブ機能コードモジュールを実行するように動作する。ネイティブ機能コードモジュールは、現在の動作モードから所望の動作モードへの移行が望ましい(例えば一方のGPUは停止され他方のGPUは開始される)旨のホストプロセッサ等の第1のプロセッサからの通知に応答して、少なくとも第1のGPUに少なくとも第2のGPUのための状態情報を提供させる。第2のGPUは、第1のGPUによって提供される状態情報を取得すると共に同じネイティブ機能コードモジュールを介して状態情報を用いて第1のGPUが中止した処理を継続するように動作する。第1のプロセッサは、少なくとも第1の及び少なくとも第2のGPUに動作可能に結合される。

(もっと読む)

画像処理装置、画像処理方法、コンピュータープログラム

【課題】画像処理に関する技術を提供する。

【解決手段】表示画像に対応する画像データを、表示画像を縦横それぞれ複数に分割した各部分画像に対応する画像データ毎に処理する画像処理装置であって、部分画像に対応する画像データを入力する入力部と、各部分画像に対応して設けられ、部分画像に対応する画像データを受け取り、画像処理を行う複数の画像処理部と、複数の画像処理部が処理した各部分画像に対応する画像データを、並列的に、走査方向に沿って順次入力することによって、表示画像に対応する画像データを入力する画像合成入力部と、順次入力される部分画像の画像データを順次記憶する記憶部と、表示画像の走査方向に沿って存在する複数の部分画像にそれぞれ対応する画像データを、まとめて1つの単位ブロックとして扱い、記憶部に順次記憶される画像データを、各単位ブロック毎に、並列的に所定の走査方向に順次出力する画像合成出力部とを備える。

(もっと読む)

車載画像処理装置

【課題】人や車両など種類が多く且つそれらを組み合わせたシーンに対応する処理を複数の処理ユニットに適切に行わせることができる車載画像処理装置を提供すること。

【解決手段】車載画像処理装置は、複数の処理ユニット40によって画像処理された処理結果に基づいて、各処理ユニット40の次回に実行する画像処理の種類と優先度を示すタグ情報を生成し、前回の画像処理時に生成されたタグ情報を用いて各処理ユニット40で画像処理を行わせるか否かを判定する。

(もっと読む)

画像読取装置

【課題】二つの読取センサにより並行して読み取られた原稿の両面の画像についての画像処理を1つの画像処理回路で高速に行うことができる画像読取装置を提供する。

【解決手段】画像読取部200では、主走査方向に沿ったライン単位で読み取られた原稿の各面についての画像データが順次メモリ領域に記憶される。そして、デジタル画像処理回路280では、処理面判定回路282により原稿の表面と裏面のうちの一方が処理面として選択されると共に、画像読出部281により処理面に対応するメモリ領域からライン単位で画像データが読み出される。また、セレクタ285a〜285eにより処理面に応じた画像処理パラメータが選択され、選択された画像パラメータを用いて、読み出された画像データに対し各種画像処理が実行される。

(もっと読む)

信号処理装置、信号処理システム、遊技機

【課題】インタラクティブな遊技機、ゲーム機などの画像展開と音声再生、役物の動作とのタイミング等を総合的に制御できる信号処理装置を提供する。

【解決手段】グラフィックス用ロジック6と音声用ロジック7とを同じ統合化LSI5に搭載して命令体系を連携する。前記グラフィックス用ロジック6は、上位CPU10の命令を解読する命令解読部20と、画像デコード部22とを備え、音声用ロジック7における音声デコード部21は命令解読部20を介した命令により動作する。

(もっと読む)

画像処理デバイス排他制御装置、制御方法、プログラム及び記録媒体

【課題】画像処理デバイス制御において不整合が起きない排他制御を行う装置を提供する。

【解決手段】1以上のタスクで画像データに対して画像処理を行う画像処理デバイスへのアクセス要求が競合する場合の画像処理デバイス制御であって、1以上のタスクからアクセスされる、デジタル画像データに対して画像処理を行う画像処理デバイスと、画像処理デバイスへのアクセスを制御する画像処理デバイス制御手段と、1スレッドを実行するタスク単位で、複数のタスクを非同期で実行するCPUと、1以上のタスクで前記画像処理デバイス制御手段による画像処理デバイスアクセス要求が競合する場合に、前記画像処理デバイスごとに画像処理デバイスアクセスの競合を防止する排他制御手段と、を有する。

(もっと読む)

パターン評価システム、パターン評価方法および半導体装置の製造方法

【課題】評価対象パターンの画像を高速で処理するとともに、コンピュータ資源の効率を向上させる。

【解決手段】CD−SEM300により撮像された評価対象パターンの一連の画像Img1〜Imgnを一枚当たりTiの時間で取り込む画像取込装置10と、一連の画像Img1〜Imgnを一枚当たりTpの時間で処理して評価対象パターンの評価結果を出力するクラスタノードCN1〜CNMと、クラスタノードCN1〜CNMが接続されてこれらを制御するメインノードMNを備える分散コンピューティングシステム1において、時間TiおよびTpを測定して一連の画像Img1〜Imgnの取得時間とその処理時間とが一致するように、クラスタノードCN1〜CNm(m≦M)を推定して一連の画像処理に割り当てる。

(もっと読む)

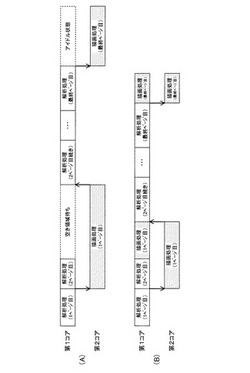

画像形成装置、印刷データ生成装置、プログラム、及び印刷データ生成方法

【課題】複数の演算部を用いてPDLデータから印刷データを生成する際の処理速度を向上させる。

【解決手段】本発明に係る画像形成装置は、PDLデータを受信する受信部と、複数の演算部を有し、前記複数の演算部のそれぞれがページ単位で処理を行うタスク又はバンド単位で処理を行うタスクを実行することにより、前記PDLデータに基づいて印刷データを生成する画像処理部と、前記PDLデータを解析して印刷ページ数を取得し、当該取得された印刷ページ数に応じて、前記ページ単位で処理を行うタスクと前記バンド単位で処理を行うタスクのそれぞれに割り当てる前記演算部の数を動的に設定する制御部と、前記生成された印刷データに基づき印刷媒体に画像を形成する印刷部と、を備える。

(もっと読む)

画像処理装置

【課題】複数のプロセッサ要素を1次元に結合してなる分散メモリ型プロセッサアレイを備えた画像処理装置により、1行の画素数がプロセッサ要素数より多い画像を処理する場合の効率向上を図る。

【解決手段】画像処理プロセッサ100は、複数個のプロセッサ要素をリング状に1次元に結合してなる分散メモリ型プロセッサアレイ120を備え、処理対象の画像の1行の画素数がプロセッサ要素数より大きいときに、該画像を折り畳んでプロセッサ要素のローカルメモリに格納する。各プロセッサ要素のメモリアクセス制御部は、ローカルメモリアクセスにより画像の所定の行に含まれる画素に対する読出要求があった際に、ローカルメモリに格納された、上記所定の行の全ての画素をローカルメモリから読み出すことが可能である。なお、ローカルメモリアクセスは、プロセッサアレイ120内部に生じるメモリアクセスである。

(もっと読む)

画像処理装置及び画像処理方法

【課題】画像データに対してより効率的に複数の画像処理をマルチコアCPUまたはGPUが施す技術を提供する。

【解決手段】入力される画像フレームを複数のブロックに分割し、この分割したブロックごとに一つ以上の画像処理を記述する画像データ形式に基づいて動作するマルチコアCPUとGPUのいずれか又は双方から成るプロセッサを備え、前記プロセッサは前記画像データ形式に基づく画像処理を並列して実施することを特徴とする画像処理装置。

(もっと読む)

画像処理及び画像解析用フレームワーク

【課題】バーチャル鏡検法デジタル画像(「バーチャルスライド」)を処理及び解析するシステムと方法を提供する。

【解決手段】システムは、複数の画像処理及び画像解析用ルーチンに対するアクセスを維持又は有するアルゴリズムサーバーを備える。アルゴリズムサーバーは、更に、複数のバーチャルスライドに対するアクセスを有する。アルゴリズムサーバーは、識別されたバーチャルスライド上で選択されたルーチンを実行すると共に、結果データを供給する。バーチャルスライドは、ネットワークを介して遠隔的又は局所的にアクセスすることができる。同様に、画像処理ルーチンは、局所記憶装置から又はネットワークを介して又はその両方により得ることができる。好都合に、ある共通サブルーチンが、他の局所的又は遠隔的に得られたルーチンに含まれるように局所的に記憶される。画像処理及び画像解析へのアクセスはモニタープロセスにより制限される。

(もっと読む)

イメージプロセッサ及びそれを含む電子装置及びイメージプロセッシング方法

【課題】多様な解像度のマルチメディアソースに対するイメージプロセッシング能力を向上させることができるイメージプロセッサを提供する。

【解決手段】イメージプロセッサ100は、ローテーションブロック120と、ラインバッファブロック130と、スケーリングブロック140と、を含む。前記ローテーションブロックは、ローテーション情報に基づいて生成されるアドレスに基づいて、再配列されたソースイメージのピクセルデータをメモリから受信して出力することができる。前記ラインバッファブロックは、前記ローテーションブロックから出力される再配列されたピクセルデータを臨時に保存することができる。前記スケーリングブロックは、前記ラインバッファブロックから出力される再配列されたピクセルデータを水平及び垂直方向にスケーリングすることができる。

(もっと読む)

イメージのハーフトーン化の方法

イメージのハーフトーン化の方法に関し、第1の数のビットで付与された少なくとも1つの入力明度が各ピクセルに割り当てられる、第1のピクセル配列の形でイメージを表現するソースファイル(18)が、電子的に処理され、第2の数のビットで付与された少なくとも1つの出力明度が第2のピクセル配列の各ピクセルに割り当てられる第2のピクセル配列の形で出力ファイル(20)を計算し、前記第2の数は第1の数未満であり、処理はグラフィックスプロセッシングユニット(GPU)(16)で行われる。  (もっと読む)

(もっと読む)

画像データ処理装置

【課題】複数の演算処理回路のいずれかが演算処理を待機する場合に比べて、処理に要する時間を短縮することを目的とする。

【解決手段】ローカルホスト装置44は、順序が後の演算処理を実行する動的再構成可能プロセッサが当該演算処理を実行する間に、順序が先の演算処理を実行する動的再構成可能プロセッサが新たに与えられた画像データに対する演算処理を実行するよう各動的再構成可能プロセッサを制御し、いずれかの動的再構成可能プロセッサに対して新たに与えられる画像データが途絶えたときに、新たに与えられる画像データが途絶えた当該動的再構成可能プロセッサと、他の動的再構成可能プロセッサとが演算処理を分担して実行するよう、動的再構成可能プロセッサ30−1〜30−mを制御する。

(もっと読む)

画像処理装置

【課題】画像処理の順序を変更するための回路の規模や消費電力を低減する。

【解決手段】それぞれ処理順番を変更可能な画像処理を行う複数の画像処理部を含む第1処理部(12)と、処理順番が固定されている画像処理を行う画像処理部を含む第2処理部(11,13)と、上記第1処理部に属する複数の画像処理部間の入出力経路の切替を行うことで、上記第1処理部内での処理順番を変更可能な入出力切替部(104)を設ける。上記のように入出力切替部での入出力経路切替により処理順番の変更を行えるのが中間処理部に限定されているため、画像処理装置における全ての画像処理部における処理順番を入出力切替部で切替可能とするのに比べて、入出力切替部の回路規模を小さくすることができ、それにより、画像処理の順序を変更するための回路の規模や消費電力を低減することができる。

(もっと読む)

アクティブなプロセッサの数を変更することを容易にする資源管理

【解決手段】

資源を管理する方法が提供される。方法は、近々の移行に応答するプロセッサに関連する資源を識別することと、識別された資源をGPUに関連するメモリから又はGPUに関連するメモリへ複製することと、を含む。

(もっと読む)

汎用使用のための処理ユニット内部メモリ

【解決手段】

汎用使用のための内部メモリを有するグラフィクス処理ユニット(GPU)及びそのアプリケーションがここに開示される。そのようなGPUは、第1の内部メモリと、第1の内部メモリに結合される実行ユニットと、第1の内部メモリを他の処理ユニットの第2の内部メモリに結合するように構成されるインタフェースと、を含む。第1の内部メモリは積層ダイナミックランダムアクセスメモリ(DRAM)又は埋め込みDRAMを備えていてよい。インタフェースは第1の内部メモリをディスプレイデバイスに結合するように更に構成されていてよい。GPUは第1の内部メモリを中央処理ユニットに結合するように構成される別のインタフェースを含んでいてもよい。またGPUはソフトウエアにおいて具現化され且つ/又はコンピューティングシステム内に含まれていてよい。

(もっと読む)

SIMD型マイクロプロセッサ

【課題】隣接する画素データとの演算を必要とする処理を行う際に、簡単な構成で従来よりも少ないマシンサイクルで実行することができるSIMD型マイクロプロセッサを提供する。

【解決手段】PE部2で条件付き命令を実行する際に、条件として隣接するPEのZ1レジスタ12を参照するための論理回路13を設けることで、隣接する左右のZ1レジスタ12を参照することが可能となる。

(もっと読む)

画像処理装置

【課題】複数の制御ブロックで処理ブロックを共有する構成の画像処理装置において、特に、それぞれの制御ブロックのクロックドメインが異なる場合における画像処理時間を短縮することができる画像処理装置を提供すること。

【解決手段】CPU100からの信号に基づいて生成される第1の書き込みパルスとシーケンサ200から発行される第2の書き込みパルスとの何れかを選択する切り替え回路を処理ブロック内に設ける。シーケンサ200はCPU100とは独立した任意のタイミングで第2の書き込みパルスを処理ブロックに対して発行する。第1の書き込みパルスと第2の書き込みパルスとが競合した場合に切り替え回路はまず第1の書き込みパルスを選択し、その後に第2の書き込みパルスを選択して、選択した書き込みパルスをレジスタに入力する。

(もっと読む)

41 - 60 / 245

[ Back to top ]