Fターム[5B057CH02]の内容

画像処理 (340,757) | 処理部 処理装置、処理システム (15,018) | 演算器 (6,373) | マルチプロセサ (674)

Fターム[5B057CH02]の下位に属するFターム

Fターム[5B057CH02]に分類される特許

61 - 80 / 245

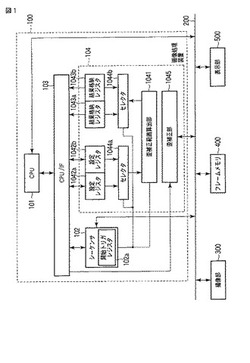

画像処理装置

【課題】複数の制御ブロックが独立に共通の画像処理ブロックを制御可能になされた画像処理装置において、画像処理時間を短縮することが可能な画像処理装置を提供すること。

【解決手段】CPU101と画像処理部104との通信専用のレジスタである設定レジスタ1042a、結果格納レジスタ1043aと、シーケンサ102と画像処理部104との通信専用のレジスタである設定レジスタ1042b、結果格納レジスタ1043bを画像処理装置100に持たせる。そして、CPU101が歪補正範囲算出部1041を制御していない期間中にシーケンサ102が歪補正範囲算出部1041を使用するとともに、シーケンサ102が歪補正範囲算出部1041を制御していない期間中にCPU101は歪補正範囲算出部1041を使用する。

(もっと読む)

外観検査装置

【課題】複数のプロセッサの処理能力を効率良く活用してダイ比較検査,セル比較検査,セルダイ混合比較検査を実施可能な外観検査装置を提供する。

【解決手段】検査対象基板の回路パターンの複数の画像データを分割して切り出し、分配する条件を画像処理装置に設定する全体制御コンピュータと、画像処理装置に設定された前記条件に従って画像データを切り出し、複数のプロセッサへ分配する画像分配処理部とを備え、該プロセッサは前記分配された画像データについて欠陥検出処理を行う。

(もっと読む)

情報処理装置

【課題】複数のグラフィックコントローラを備え、使用状態に応じて動的に表示制御処理を行うグラフィックコントローラを切り替える動作モードと、各グラフィックコントローラを単独で利用することにより各グラフィックコントローラの機能をより多く利用可能とする動作モードとを利用することができる情報処理装置を提供する。

【解決手段】本発明に係る情報処理装置は、表示制御処理を行うiGPUと、iGPUより表示制御処理能力が高く消費電力が多いdGPUと、iGPUとdGPUとを動的に切り替えて表示制御処理を行う動的切替動作モードで表示制御を行うかiGPUおよびdGPUのいずれか一方のみで表示制御処理を行う単独動作モードで表示制御を行うかを判定する動作モード判定部54と、単独動作モードで表示制御を行うと判定されると、iGPUおよびdGPUのいずれが表示制御処理を行うかを判定する単独動作モード判定部56と、などを備えたものである。

(もっと読む)

並列計算装置

【課題】実効効率の高い並列計算装置を提供する。

【解決手段】並列計算装置は、並列して演算処理を行う複数の演算プロセッサー(PE)2と、PE2のそれぞれに制御命令を供給する命令実行制御プロセッサー(PE−I)3とを備える。PE2において記憶部11Aは、複数のデータ又は複数の演算結果を保持する。サブプロセッサーSPE2Aにおける演算部ALUl2Aは、記憶部11Aから読み出したデータに演算処理を施し、その結果を記憶部llAに供給する。サブプロセッサーSPE2Aは、複数の該サブプロセッサーSPE2Aのうち少なくとも2つのサブプロセッサーが同じ構造を有するサブ演算プロセッサーグループSPE2Gを形成する。PE−I3における交換部31は、サブ演算プロセッサーグループSPE2Gに含まれるサブプロセッサーSPE2A〜2Cに供給する制御信号を交換して供給する。

(もっと読む)

データ処理装置、データ処理方法およびプログラム

【課題】 リングバス上のデータを動作基準信号(クロック)毎に次のモジュールに転送しながらリングバス上を周回させ、単一あるいは複数のモジュールで単一あるいは複数ストリーム処理を行うシステムにおいて、特定の処理モジュールにおけるリングバスの占有率を考慮していなかった。

【解決手段】 各処理モジュールの処理コアから出力したデータを格納しているパケットで、出力した処理モジュール以外の処理モジュールに処理されていない可能性のあるパケットの個数を推定し、この推定に基づいて処理コアからの出力を制御する。

(もっと読む)

リングバスを用いたデータ処理装置、データ処理方法およびプログラム

【課題】 リングバスに接続されたデータ処理装置において、複数のデータ処理ストリームを投入した場合や、処理回路内部でデータ量が増減してしまうケースが存在する際に発生し得る、デッドロックや、リングバスの実効効率の低下を軽減する必要がある。

【解決手段】 リングバスの動作速度を、データ処理にかかる動作速度よりも早くすることにより、リングバスを周回するデータによるデータ出力抑制の機会を減らし、処理効率の低下を抑制する。

(もっと読む)

画像処理装置及びその制御方法

【課題】それぞれ複数種類の回路構成のいずれかに再構成可能な複数の回路構成部を有する画像処理装置において、複数の画素データにおけるある属性の画素データの出現頻度、及びある属性から他の属性に切り替えられる切替回数に応じて最適な種類の回路構成を固定して、切替時間に係るオーバーヘッドを低減する画像処理装置を提供する。

【解決手段】本画像処理装置は、回路動作中に論理回路を再構成可能な複数の回路構成面を有するロジック回路と、各論理回路に切り替えるための切替時間を予め記憶した記憶部とを備え、実行する画像処理に応じてロジック回路を再構成する。また、本画像処理装置は、処理する順に画像データにおける画素ごとの属性を解析し、解析した属性ごとに対応する論理回路へ切り替える総切替時間を処理する順序を考慮して求め、当該総切替時間に基づいて、固定する回路構成面へ構成する論理回路を決定する。

(もっと読む)

情報処理装置

【課題】リアルタイム系の処理と非リアルタイム系の処理とが混在しつつ情報を処理する情報処理装置において、無駄なスケジューリング発生を極力抑制し、リアルタイム処理の遅延を抑え、より高性能な制御を行える情報処理装置を実現する。

【解決手段】操作に関する指示の入力を受け付けると共に各種表示を行う操作表示部と、画像情報の処理を行う画像処理部と、同種複数のコアを備えたプロセッサと、を備える情報処理装置であって、リアルタイム性を必要としない前記操作部に関連するプロセスについての制御を前記プロセッサの一方のコアで担当するよう固定し、前記プロセスと動作上連携が必要な前記画像処理部に関連するプロセスについての制御を前記プロセッサの他方のコアで担当するよう固定する。

(もっと読む)

画像処理装置、画像処理方法、プログラム、演算処理装置、演算処理方法及びプログラム

【課題】高速なインターフェースを用いることなく画像処理を高速化するための着脱可能な演算処理装置を備えた画像処理装置を提供する。

【解決手段】画像データに処理を行い記憶したことを検知する手段と画像データが送出可能か否かを判断して画像データに識別情報を付与して送出する手段とを有する画像処理部と、画像データが受け入れ可能か否かを判断して識別情報付き画像データを受け入れて記憶する手段と、画像データに演算処理を行う手段と、処理画像データとデータ情報とを記憶する手段とを有する高速演算処理部と、を備え、画像処理部はデータ情報に基づいて取得した処理画像データに処理を行い記憶する手段と、処理画像データをネットワークに接続して送受信する手段と、処理画像データを記録印刷する手段と、を備え、画像処理部と、高速演算処理部と、の間で並行して高速な画像データ処理を行うためにデータの送受信を最適に制御する制御手段を有する。

(もっと読む)

画像再生装置及び中間語プログラム実行方法

【課題】動的翻訳実行の影響によって本来なら優先すべき性能が劣化してしまう事を抑制した、高速に中間語を実行する事が出来る画像再生装置を提供する。

【解決手段】中間語解釈実行部123は、ソースプログラムまたは中間語プログラムを解釈実行中に実行されたモジュールが動的翻訳条件を満たしていれば、実行時翻訳部124を用いて当該モジュールを機械語へ翻訳しようとする。この際、ユーザ操作による応答性能が優先されるべきユーザインタフェース応答スレッド等、動的翻訳が不適切なスレッドおいては機械語への翻訳を禁止する。

(もっと読む)

3次元物体照合装置及び3次元物体照合方法

【課題】高速な照合処理を実現する3次元物体の照合装置を提供する。

【解決手段】対象物体の3次元データを取得する手段(1)と、取得したデータ及びモデルデータを蓄積する蓄積手段(2)と、複数の照合データ領域を設定する領域設定手段(3)と、画像処理専用の演算装置であるグラフィックプロセッシングユニット(GPU)(501、6)とを備える。GPU(501、6)は、設定された照合データ領域毎に、取得した3次元データを蓄積手段に蓄積されたモデルデータと照合し、その際、複数の照合データ領域について、照合する処理を並列的に処理する。

(もっと読む)

ハイブリッドシステム構成を使用した画像処理

【課題】画像を調整するためのシステム及び方法を提供する。

【解決手段】画像を調整するためのシステム及び方法によって、離散プロセッサのグラフィックス処理性能に対する影響が最小化される。ハイブリッドシステム構成は、離散プロセッサ及び統合プロセッサを備えている。画像は、ハイブリッドシステム内の離散プロセッサのビデオエンジン又はグラフィックスエンジンによって生成される。次に、個々の画像がホスト処理メモリ内のバックバッファに転送される。画像が解析され、調整設定値を生成するために使用される画像解析結果が生成される。このバックバッファがスワップされてフロントバッファになり、調整済みの画像を表示するために統合プロセッサによって調整設定値が画像に適用される。この調整を電力節約技法と共に使用して、ディスプレイバックライト照明をうす暗くする際の画像品質を維持することができる。

(もっと読む)

グラフィックオペレーションのための高レベルプログラムインターフェース

【課題】イメージ処理のツールにプログラマが容易にアクセスできることや、グラフィック計算が効率的であることの重要性が常に高まっている。OpenGL(登録商標)とプログラム可能GPUの組み合わせは、グラフィックプログラムが可能であることについて広範な進歩を遂げたが、更に高レベルのインターフェースを実現する。

【解決手段】フィルタとイメージとの間の関係を定義することによって、イメージを生成するためのAPI及び技術を含み、このような関係は、要求しているアプリケーションとグラフィックサービス資源との間の協働セッションによってプログラム的にオブジェクトで組み立てられる。本システムはまた、プログラム的に組み立てられたオブジェクトの最適化とマルチプロセッサ環境でのレンダリングのための技術とに関する態様を含む。

(もっと読む)

グラフィックオペレーションのための高レベルプログラムインターフェース

【課題】イメージ処理のツールにプログラマが容易にアクセスできることや、グラフィック計算が効率的であることの重要性が常に高まっている。OpenGL(登録商標)とプログラム可能GPUの組み合わせは、グラフィックプログラムが可能であることについて広範な進歩を遂げたが、依然としてグラフィックサブシステムへのより高レベルのインターフェースに対する必要性があり、高度なインターフェースを提供する。

【解決手段】第1ノードと第2ノードが結合できるかどうかを判定し、イメージを生成するためのAPI及び技術を含み、このような関係は、要求しているアプリケーションとグラフィックサービス資源との間の協働セッションによってプログラム的にオブジェクトで組み立てられる。本システムはまた、プログラム的に組み立てられたオブジェクトの最適化とマルチプロセッサ環境でのレンダリングのための技術とに関する態様を含む。

(もっと読む)

グラフィックオペレーションのための高レベルプログラムインターフェース

【課題】イメージ処理のツールにプログラマが容易にアクセスできることや、グラフィック計算が効率的であることの重要性が常に高まっている。OpenGL(登録商標)とプログラム可能GPUの組み合わせは、グラフィックプログラムが可能であることについて広範な進歩を遂げたが、依然としてグラフィックサブシステムへのより高レベルのインターフェースに対する必要性があり、高度なインターフェースを提供する。

【解決手段】フィルタとイメージとの間の関係を定義することによって、イメージを生成するためのAPI及び技術を含み、このような関係は、要求しているアプリケーションとグラフィックサービス資源との間の協働セッションによってプログラム的にオブジェクトで組み立てられる。本システムはまた、プログラム的に組み立てられたオブジェクトの最適化とマルチプロセッサ環境でのレンダリングのための技術とに関する態様を含む。

(もっと読む)

データ処理装置および方法

【課題】 複数のレイに対する衝突チェックを実行するデータ処理装置を提供する。

【解決手段】 データ処理装置の制御部は、空間データ構造内の第1ノードと関連した複数のレイに対して複数のパケットを生成する。また、複数のパケットのうちの少なくとも1つは、k個(ただし、kは自然数)のレイに関する情報を含む。さらに、処理部は、複数のパケットが順次に提供され、第1ノードと関連した複数のレイそれぞれが第1ノードの子孫ノードのうちどのノードと関連するかを決定する。

(もっと読む)

画像処理装置、プログラム及びシステム

【課題】画像処理の目標値と評価値との誤差を減少することのできる画像処理装置及びプログラムを提供する。

【解決手段】画像処理装置1は、画像情報30に対して画像処理を実行する複数の画像処理モジュールと画像処理モジュールの画像処理の能力の期待値を示す期待値表情報32を記憶する記憶部3と、画像処理の能力の目標値を設定する目標値設定手段20Hと、目標値と、期待値表情報32の期待値に対して重み付けして算出される総合期待値とに基づいて画像処理モジュールを組み合わせて画像処理手法を構成する手法構成手段20Aと、画像情報30に対して、画像処理手法を用いて処理単位ごとに画像処理を実行する画像処理実行手段20Iと、画像情報30に対して実行された画像処理の能力を処理単位ごとに評価して評価値を出力する評価値算定手段20Eと、目標値及び評価値に基づいて画像処理モジュールを差し替える手法差替手段20Bとを有する。

(もっと読む)

並列処理型プロセッサ

【課題】回路規模や配線資源を大幅に増加することなく、演算精度を容易に変更することのできる並列処理型プロセッサを得る。

【解決手段】プロセッサエレメント3a〜3dを、PEアレイ2−1〜2−Nにおける演算の最大粒度となる個数とする。プロセッサエレメント3a〜3dのゲート回路5は、実現する粒度に基づいて他のプロセッサエレメントの桁上がり信号を入力するか否かを切り替える。メモリ調停回路6は実現する粒度に応じてメモリ7にアクセスする領域を分割する。

(もっと読む)

画像処理装置及びデータプロセッサ

【課題】ハードワイヤード方式の効率性を確保し、且つ、様々な画像処理機能を実現することが容易な画像処理装置を提供する。

【解決手段】ハードワイヤード方式で実現される画像処理のための演算機能とバッファメモリのメモリアクセス制御に制約を設けて、その制約の範囲をプログラム制御等によって可変可能とする。バッファメモリ(105)は記憶ライン単位という制約を受けて外部からデータを入力し、入力する記憶ライン数と記憶ラインの位置を制御回路(101,102)によりプログラマブルにでき、演算回路(106)はバッファメモリから供給される単数又は複数の記憶ラインのデータ単位で演算を行うという制約を受け、そのデータ単位に対する演算処理単位の演算処理内容を制御回路(101,102)によりプログラマブルに指定することができる。

(もっと読む)

ビデオ分析処理方法

【課題】注目ピクセル群を画像からSIMD型プロセッサに適するように選択する。

【解決手段】第1フェーズでは、注目ピクセル群を、所定のマスク23を使用して収集し、そしてピクセルマトリクスに格納する。第2フェーズでは、ビデオ分析処理をピクセルマトリクスに対して行ない、そして第3フェーズでは、これらのピクセルを、同じ所定のマスク23を使用して分散させる。これにより、多数のピクセルを同時に処理することができるので、総合性能を向上させることができる。DMAユニットを使用して、ピクセル群を収集し、そして分散させている間のプロセッサの処理負荷を無くすこともできるので、性能を更に向上させることができる。ネットワークカメラにビデオ分析システムを一体化させることにより、ネットワークトラフィックを減らす。

(もっと読む)

61 - 80 / 245

[ Back to top ]