Fターム[5B061RR03]の内容

Fターム[5B061RR03]に分類される特許

41 - 60 / 218

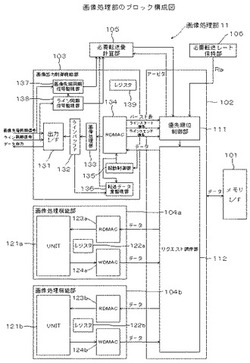

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

インタフェース装置、画像形成装置

【課題】送信データの書き込み要求と、受信データの読み出し要求とが重複して発生しているときに、受信データによるメモリオーバーを起こすことなく、送信データの書き込みと受信データの読み出しとからなる一連の処理を行う時間を短縮することができるインタフェース装置を提供する。

【解決手段】調停部24は、送信データの書き込み要求と、受信データの読み出し要求とが重複して発生して、書き込み要求を読み出し要求に優先して有効としている間において、送信データ記憶部20に記憶されている送信データのデータ量が予め設定された第1データ量を超えており、且つ、受信データ記憶部22に記憶されている受信データのデータ量が、記憶容量未満の範囲で予め設定された第2データ量を超えているときには、書き込み要求を有効とすることを中断して、一時的に読み出し要求を書き込み要求に優先して有効とした後に、書き込み要求を有効とすることを再開する。

(もっと読む)

データ分配装置

【課題】大量のデータを各部に適切に分配し、データ転送の高速化を図ることができる

ようにする。

【解決手段】PCI Express規格のスイッチ及びバスを介してデータの転送を受けるPCI Express規格のエンドポイント21を備える。バッファ22は、上位のスイッチ及びバスを介して転送されたデータをバッファリングする。分配制御回路23は、この転送されたデータを下位の複数の出力先である出力部に分配して転送する制御を行う。PCI Express規格のルートコンプレックス24及びスイッチ25は、分配制御回路23の制御によりデータの転送を行なう。

(もっと読む)

データ転送制御装置およびデータ転送制御方法

【課題】共有バスに接続する複数のDMAチャネルがあって、SDRAM等のメモリにアクセスする際に、あらかじめ決められた優先順位を守りながら、高効率にメモリアクセスする調停手段を提供する。

【解決手段】マスターデバイスからのデータ転送要求を一定量保持する要求保持部と、保持されたデータ転送要求を優先順位及び予め定められた回数だけ連続するように並び替える要求並び替え部とを備え、前記データ転送要求を前記要求並び替え部が並び替えた順で発行することで、優先順位に応じて複数チャネルを並び替えるとともに同格の優先順位を持つ複数チャネルを平均的に連続させることができる。

(もっと読む)

ダイレクトメモリアクセスシステム及びその制御方法

【課題】高機能かつ高性能のダイレクトメモリアクセス転送を、CPUに対する負荷を増大させることなく、かつ、回路規模を増大することなく実現する。

【解決手段】システムは、ダイレクトメモリアクセス部とプロセッサ部とを有する。ここで、プロセッサ部は、メモリと、メモリから命令を読み出して実行することで、ダイレクトメモリアクセス部が実行する命令を当該ダイレクトメモリアクセス部に書き込むプロセッサとを備える。また、ダイレクトメモリアクセス部は、複数のプログラムカウンタと、複数のプログラムカウンタを順に選択する選択手段と、プロセッサによって書き込まれた命令を保持する命令保持手段と、選択手段で選択されたプログラムカウンタにより示される命令保持手段のアドレスに格納されている命令を出力する出力手段と、出力手段によって出力される命令に応じてダイレクトメモリアクセスによるデータ転送を実行する実行手段とを備える。

(もっと読む)

データ通信制御装置

【課題】バスの動作タイミングを適切に調整することができるデータ通信制御装置の提供。

【解決手段】本発明によるデータ通信制御装置は、CPUコア10と周辺機器60の間にバスブリッジ20を備え、前記CPUコアと前記バスブリッジの間は、高速バス70で接続され、前記周辺機器と前記バスブリッジの間は、低速バス72で接続され、前記周辺機器から前記バスブリッジを介して前記CPUコアへデータを送信する際に、前記周辺機器から前記バスブリッジへの前記低速バスによるデータの送信方法を、シリアル通信とパラレル通信の間で動的又は静的に切り換える切換制御部30,62Aを備えることを特徴とする。

(もっと読む)

8ビットベースのデータ処理システム

【課題】ホストとクライアントの間を、ホスト側のOS進化などで実質的にスポイルされない形で結ぶ。

【解決手段】一実施の形態に係るデータ処理システムは、8ビット以上の外部データを扱うホスト100を、8ビット単位の内部データおよび8ビットの内部アドレスを用いて1以上のクライアント600につなぐ構成を持つ。このシステムにおいて、接続部500を介して変換モジュール300Sに複数のクライアント600が接続される場合には、これら複数クライアントのうち、前記内部アドレスにより特定された1つ(ターゲットI/Oボード)が、変換モジュール300Sと情報交換できるように構成される。ここで、ホスト100は、変換モジュール300Sに対して、前記内部アドレスの8ビット空間の1箇所を指定し、指定したアドレス空間に対してデータの送受を行う。指定されたアドレス空間に接続されたターゲットI/Oボードは、受け取ったデータに対して自身の処理を行う。

(もっと読む)

バス制御システム、及び、バス制御方法

【課題】 通信時間を増大させることなく、予め仕様で決められているスレーブアドレスの数の制限を越えて、スレーブデバイスを接続することができるバス制御システムを提供する。

【解決手段】

マスタデバイスから送信される、データ送受信の対象となるスレーブデバイスの論理アドレスを、スレーブバスのバス番号とスレーブデバイスの実アドレスに変換して、全てのスレーブバスに対し、マスタデバイスからの論理アドレスの送信と同時に実アドレスデータを送信する。その後、スレーブバスのバス番号により特定される、データ送受信の対象となるスレーブデバイスが接続されたスレーブバスに対してのみ、マスタバスとの接続を維持し、データ送受信対象でないスレーブデバイスが接続されたスレーブバス上には、通信終了を示す信号を送信してデータの送受信を終了させる。

(もっと読む)

調停装置、画像処理装置、及び画像形成システム

【課題】書込要求信号が連続して調停手段に入力される場合に比べて、読み出しに必要な伝送路の帯域に応じて書込みに必要な伝送路の帯域を確保する、調停装置、画像処理装置、及び画像形成システムを提供する。

【解決手段】キューカウンタ62及び抑制装置64を備え、キューカウンタ62が書込要求信号wrreqが入力されたときに、読出データの読み出しが行われていない読出要求信号rdreqの数をカウントしてカウント値として抑制装置64に出力し、抑制装置64は、入力されたカウント値に応じて、チャネルCH1からのアクセス要求信号CH1_REQが調停回路52に入力される時間を遅延させることにより、チャネルCH1のアクセスを抑制する。

(もっと読む)

データ転送装置及びデータ転送方法

【課題】実行順序が定められた複数のデータ転送処理をDMA転送装置が実行する場合において、CPUが介在する頻度を少なくすることを目的とする。

【解決手段】CPU10は、指定したデータ転送処理を実行させるデータ転送指示情報と、実行順序を制御する制御指示情報との指示情報が並べられた指示コマンドを、各チャネル200に対応付けてコマンドメモリ130に設定し、各チャネル200を起動する。各チャネル200は起動されると、コマンドメモリ130に設定された指示コマンドのうち、自己に対応付けられた指示コマンドの指示情報を並べられた順に読み出す。各チャネル200は、読み出した指示情報がデータ転送指示情報であった場合、データ転送指示情報で指定されたデータ転送処理を実行し、読み出した指示情報が制御指示情報であった場合、他のチャネル200によるデータ転送処理の実行状況に応じて、次の指示情報の読み出しを待つ。

(もっと読む)

非同期バス・インタフェース回路

【課題】マイクロプロセッサにはバス・アクセスのためのバス・アクセス・ウエイトを最小とし、一連の連続バス・アクセス動作が書き込み動作、読み出し動作とも互いに物理的な影響を与えず、各動作を停止させることなく連続非同期バス・アクセスを正常に実行することができる非同期バス・インタフェース回路を提供する。

【解決手段】アドレスを一時保存し、出力するライト・アドレス・バッファ114と、データを一時保存し、出力するライト・データ・バッファ116と、ライト・イネーブル信号を生成し、出力するライト制御回路115と、を備え、ライト・イネーブル信号がイネーブルのとき、ライト・アドレス・バッファ114から出力されるアドレスとライト・データ・バッファ116から出力されるデータとを、内部レジスタ102に書き込む。

(もっと読む)

データ受信システムおよび割り込み実行方法

【課題】複数のデータ出力装置からの非同期の割り込み要求信号を欠落なく、効率的に確実に、データ受信装置に、任意のタイミングでデータを送信するデータ受信システムおよび割り込み実行方法を提供する。

【解決手段】複数のデータ出力装置から非同期で割り込み要求もしくはデータを受信するデータ受信システムにおいて、データ出力装置からの割り込み要求信号を検出し、CPUに割り込み信号を送信する割り込み発生回路部と、データ出力装置から受信データを取得した複数のデータを一時的に保持するデータバッファ部と、割り込み発生回路部からの割り込み信号を受信した際に全てのデータ出力装置に対してデータが入力されているか否かを判断し、入力されているデータを順次受信する割り込みルーチンと、全てのデータ受信が終了した場合に割り込みリセットを実行するCPUを有するデータ受信システムを提供する。

(もっと読む)

コンピュータ・システム及びコンピュータ・システムにおけるデータ転送方法

【課題】 HILSに適合する、オーバーヘッドの少ないDMA転送技法を提供すること。

【解決手段】 DMAによって、コンピュータのメモリからデータを周辺機器に転送するためのデータ転送装置を有するコンピュータ・システムにおいて、連続DMA機構がイネーブル処理に応答して、データ転送要求を継続的に繰り返し出す。HILS用のシミュレーション・システムは、シミュレーションの結果のデータを、メモリの所定の領域に配置する。そして、連続DMA機構からの前記データ読出し転送要求に応答して、世代IDのデータとともに連続DMA機構へ前記メモリからデータを転送する。連続DMA機構は、転送された世代IDを受信IDとして保存し、転送された前記世代IDが、保存されている受信IDと異なる(更新されている)ことに応答して、前記転送されたデータを受信する。連続DMA機構は、ディスエーブルされるまで、データ転送要求を継続的に繰り返す。

(もっと読む)

調停装置、バスアクセス調停プログラムおよびバスアクセス調停方法

【課題】共通のバスへのデータ転送の転送効率を向上させることを課題とする。

【解決手段】調停装置は、複数のDSP間における共通のバスへのアクセス権の切替時に要する切替時間を保持し、切替時間と、DSPの温度が所定閾値以上である場合に受信する複数のDSPの温度情報とに基づいて、複数のDSPそれぞれの位相シフト値を求める。そして、調停装置は、発振器によって送出された基準クロックと、求められた位相シフト値とを用いて、複数のDSPごとに異なるクロックを生成して出力する。

(もっと読む)

DMAコントローラ及びその制御方法

【課題】従来のDMAコントローラは、効果的なデータ転送の最適化を行うことができないという問題があった。

【解決手段】本発明にかかるDMAコントローラは、外部メモリ11とバス9を介して接続された複数のDMA部40−0〜40−mが実行するデータ転送を制御するDMAコントローラであって、DMA部40−0〜40−mからのデータ転送の要求に対してバス9の調停を行う調停回路12と、複数のDMA部40−0〜40−mのうち選択されたいずれか一つのDMA部と、外部メモリ11と、の間において転送される転送データのバースト長を当該転送データのデータ転送間隔に基づいて制御するバス観測回路13と、を備える。このような回路構成により、効果的なデータ転送の最適化を行うことができる。

(もっと読む)

データ転送装置、データ転送方法及びデータ転送プログラム

【課題】DMA転送装置において、任意のタイミングに転送情報を切り替え可能とすることを目的とする。

【解決手段】転送周期決定回路120は、所定の周期を示す周期信号40を生成する。切り替え回路130は、周期信号40に同期して、カウンタ値をインクリメントする。また、切り替え回路130は、カウンタ値をオフセット値43として、固定アドレス記憶部140が記憶した固定アドレス41とオフセット値43とからアドレス44を計算する。DMA転送チャネル110は、切り替え回路130のRAMにおけるアドレス44が示す位置から転送情報42を取得する。そして、DMA転送チャネル110は、取得した転送情報42に従いデータを転送する。

(もっと読む)

情報処理装置およびメモリアクセス調停方法

【課題】プロセッサの内蔵メモリに対して、小規模で常に優先かつ高速なメモリへのデータ入出力機構を実現する。

【解決手段】命令をパイプライン処理するプロセッサと、プロセッサに内蔵するメモリと、メモリに対し高い優先度でアクセスをする入出力制御手段からなる情報処理装置において、メモリアクセス調停方法は、プロセッサと入出力制御手段のメモリへのアクセスが競合した場合に、プロセッサに供給するクロックをウェイトさせるステップ(S512)と、入出力制御手段のメモリへのアクセスを実行するステップ(S506)と、入出力制御手段のメモリへのアクセス終了後にプロセッサのクロックウェイトを解除し、プロセッサのメモリへのアクセスを実行するステップ(S507、S511)からなる。

(もっと読む)

処理装置

【課題】データ転送を調停する調停部の設定を容易にしうるようにすること。

【解決手段】転送モニタ回路33は、調停回路31にて制御されるDMAチャネルのチャネル番号と、生成されるDMAチャネルにより転送されるデータのデータ量をモニタ情報として記憶する。そして、転送モニタ回路33は、調停回路31が調停する要求信号を出力する処理部21〜28が動作するタイミングを制御する同期信号Syncや、処理部21〜28から出力されるエラー通知信号ERR、等に基づく期間のモニタ情報を記憶する

(もっと読む)

集積回路システム、データ書き込み方法、データ読み出し方法

【課題】集積回路において処理に必要な時間を確保しつつ、集積回路同士のバスにおけるデータ転送能力の向上を可能とすること。

【解決手段】集積回路システム1であって、第一バス幅を有する第一データバスに接続されデータ送受信に第一時間を要する第一集積回路20と、第一バス幅よりも広い第二バス幅の第二データバスに接続されデータ送受信に第一時間よりも長い第二時間を要する第二集積回路40と、第一データバス及び第二データバスに接続されそれぞれのバスを介して第一集積回路及び第二集積回路とデータを送受信する中継回路30とを備える。

(もっと読む)

DMA転送制御装置およびDMA転送制御方法

【課題】転送効率を向上したDMA転送を可能にする低消費電力で回路規模の小さなDMA転送制御装置の実現。

【解決手段】転送元からの転送データを一時的にメモリ4に書き込み、メモリに書き込まれた転送データを、転送指示に応じて読み出して転送先に出力するDMA転送制御装置3であって、書き込まれた転送データのメモリにおける先頭位置を示すライトポインタWPと、転送指示で指示済みの転送データのメモリにおける位置を示す指示済リードポインタRAPと、を備え、ライトポインタWPと指示済リードポインタRAPの差分と、転送サイズXとを比較し、差分が転送サイズ以上の時に、転送指示を発行する。

(もっと読む)

41 - 60 / 218

[ Back to top ]