Fターム[5B061RR03]の内容

Fターム[5B061RR03]に分類される特許

61 - 80 / 218

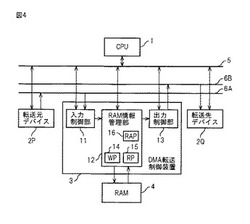

DMA転送制御装置およびDMA転送制御方法

【課題】転送効率を向上したDMA転送を可能にする低消費電力で回路規模の小さなDMA転送制御装置の実現。

【解決手段】転送元からの転送データを一時的にメモリ4に書き込み、メモリに書き込まれた転送データを、転送指示に応じて読み出して転送先に出力するDMA転送制御装置3であって、書き込まれた転送データのメモリにおける先頭位置を示すライトポインタWPと、転送指示で指示済みの転送データのメモリにおける位置を示す指示済リードポインタRAPと、を備え、ライトポインタWPと指示済リードポインタRAPの差分と、転送サイズXとを比較し、差分が転送サイズ以上の時に、転送指示を発行する。

(もっと読む)

バス制御方法

【課題】効率的にバスを使用すること。

【解決手段】バスにアクセスする優先度がそれぞれ異なる複数のバスマスターのうちの一つの注目バスマスターの保証転送帯域に対応するリクエスト許可数を記憶することと、前記バスにアクセス要求している前記注目バスマスター以外のバスマスターの数を、前記注目バスマスターのリクエスト許可数以内でリクエスト数として記憶することと、前記リクエスト数と同数の前記注目バスマスター以外のアクセス要求が処理された後に、前記注目バスマスターのアクセス要求を処理することと、を含む、バス制御方法。

(もっと読む)

データ転送装置

【課題】複数のカメラで撮影した映像の画像データを主記憶部へ転送する場合であっても、1つのDMAコントローラで画像データを転送できるようにする。

【解決手段】複数のカメラ81、82で撮影されたそれぞれの画像データを複数の画像バッファメモリ部51、52に記憶させ、画像結合部7がそれぞれの画像バッファメモリ部51、52に記憶された複数の画像データを連結して結合した画像データとして出力し、ダイレクトメモリアクセスコントローラ部4がその画像データをメモリ部3に転送するようにした。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の動作方法

【課題】バスシステムを効率的に使用できる半導体集積回路装置および半導体集積回路装置の動作方法を提供すること。

【解決手段】ステータス情報が書き込まれるステータスレジスタおよび更新要求が書き込まれる更新制御レジスタを含むレジスタ部を有し、更新制御レジスタに更新要求が書き込まれた場合にステータスレジスタの更新を行うCPU100、200、およびI/O300に対し、ステータスレジスタに記憶されるステータス情報を読み出しかつ更新制御レジスタに更新要求を書き込むための拡張ロード命令を実行できるように、CPU100、200、バスシステムおよびI/O300を構成した。

(もっと読む)

処理装置、画像形成装置及び処理方法

【課題】データ処理の処理速度を低下させることなく別のデータ処理を行うことができる処理装置、画像形成装置及び処理方法を提供する。

【解決手段】主DMA制御部22は、レジスタ部23、DMA起動部24などを備え、従DMA制御部25は、レジスタ部26、DMA起動部27などを備えている。主DMA制御部22は、主DMA転送及び主画像処理の制御を行う。また、従DMA制御部25は、従DMA転送及び従画像処理の制御を行う。マルチプレクサ28は、CPUからのセレクト信号SELがローレベル(Lo)の場合には、主DMA制御部22からの信号を画像処理部21へ出力し、セレクト信号SELがハイレベル(Hi)の場合には、従DMA制御部25からの信号を画像処理部21へ出力する。

(もっと読む)

情報処理装置及び画像データ記録システム

【課題】I/Oバッファに対するDMA転送を高速化することができる情報処理装置及び画像データ記録システムを提供すること。

【解決手段】本発明の情報処理装置1は、内部バス40と、転送元リソースから転送先リソースにデータ転送を行うDMAコントローラー20と、FIFO320(I/Oバッファ)を含み、FIFO320と外部デバイス100の間のデータ転送を行うI/Oコントローラー30と、を含む。DMAコントローラーは、転送元リソースがI/Oコントローラーである場合は、I/Oコントローラーからの1回のデータ転送要求に対して、FIFO320から複数のデータを連続して読み出すか1つのデータを読み出すかを選択し、転送先リソースがI/Oコントローラーである場合は、I/Oコントローラーからの1回のデータ転送要求に対して、FIFO320に複数のデータを連続して書き込むか1つのデータを書き込むかを選択する。

(もっと読む)

データ伝送システム

【課題】ライン上でデータ信号に混入されるインパルス性雑音の認識度を高めて受信状態の通信端末による送信状態への遷移の効率化を図り、ノイズ環境下においても安定かつ確実なパケット通信を行う。

【解決手段】通信端末1a、1b、1c、・・・において、受信状態の端末CPU10a、10b、10c、・・・は、受信したデータ信号S1を構成するフレーム内のスタートビットのコマンドを所定時間幅のインパルス性雑音と認識したとき、このコマンドを破棄して送信待機時間の経過前に送信状態へと遷移する。また、受信状態の端末CPUは、受信したデータ信号を構成するフレーム内のチェックサムコマンドの作用によって、パリティエラーで破損された少なくとも1のビットの1バイトを自動修復する。さらに、受信確認信号の受信ができず所定の回数の再送信の動作を行った後の端末CPUは、インパルス性雑音成分が有する周期に対応させて送信待機時間を短く変更する。

(もっと読む)

信号処理装置

【課題】一定時間毎にA/D変換器を起動して複数のアナログ信号をA/D変換する信号処理装置において、何れかのアナログ信号について、それのA/D変換データのA/D変換器からメモリへのDMA転送を、A/D変換器の起動間隔とは異なる任意の間隔で行えるようにする。

【解決手段】マイコン10にて、A/D変換器11からRAM17にデータを転送するDMAコントローラ16へは、A/D変換完了時毎に生じるDMA転送要求信号(TrgB)とは別のDMA転送要求信号(TrrC)が、タイマユニット25から与えられ、そのタイマユニット25は、CPU21により周期とパルス幅が設定されるPWM信号出力回路23からのPWM信号に特定方向のエッジが生じるとTrgCを出力する。更にDMAコントローラ16は、TrgB,Cの各々について、A/D変換器11のどのチャンネルのA/D変換データを転送対象とするかがCPU21により指定される。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】システムバス、メモリバス、プロセッサバスの三種の各バスの使用効率を最大とする情報処理装置のバスシステムを提供する。

【解決手段】プロセッサ101が接続されたプロセッサバス111と、メインメモリ104が接続されたメモリバス112と、入出力デバイス105が接続されたシステムバス113とが三叉路接続コントロール手段103に接続される。この三叉路接続コントロール手段103は、それぞれのアドレスバスと制御バスが接続され、相互にアドレス及び制御信号を転送すると共に、データバス制御信号を発生するバス・メモリ接続コントローラを有する。又、この三叉路接続コントロール手段103は、それぞれのデータバスが接続され、データバス制御信号に応じてこれらのデータバス上のデータを相互に転送するデータパススイッチを有する。

(もっと読む)

情報処理装置、集積回路装置、電子機器

【課題】ハードウェアの回路規模の増大と処理実行部の処理負担を抑え、多重割り込みにも対応した割り込み処理を有する情報処理装置等を提供する。

【解決手段】情報処理装置10は、複数の割り込み要求20の優先度を保持する優先度設定レジスタ51と現在優先度を保持する現在優先度レジスタ52とIRQ要求元の情報を保持する要求元情報レジスタ53と割り込み制御部60と処理実行部70とを含み、割り込み制御部60は、所定の基準を満たす割り込み要求20をIRQ要求元と判断し、IRQ要求元の優先度と固有識別番号を要求元情報レジスタ53に書き込み、要求元情報レジスタ53の優先度が現在優先度より高ければIRQ30を出力し、処理実行部70は、IRQ30を受け取ると要求元情報レジスタ53に保持されたIRQ要求元の固有識別番号に対応した処理を行う。

(もっと読む)

情報処理装置、バス制御装置

【課題】一番周波数の低い二次側接続装置に合わせることなく個々の二次側接続装置の最大動作周波数で動作可能な情報処理装置にする。

【解決手段】基準発振信号PCICLK_0を供給する主装置3Aを接続部20_0に接続する。二次側には、主装置3Aの指示に基づき情報処理を行なう二次側接続装置が装着される接続部20_@を設ける。接続回路10Aは、基準発振信号PCICLK_0の供給を受け、各二次側接続装置のそれぞれの動作可能周波数に対応する基準発振信号PCICLK_@を生成して各別の基準発振信号線22_@を介して出力する。接続回路10Aは、主装置3Aと各二次側接続装置の基準発振信号PCICLKの周波数の違いを吸収するので、各二次側接続装置の最大の周波数を使用することが可能となる。一番周波数の低い二次側接続装置に合わせることなく個々の二次側接続装置の最大動作周波数で動作可能になり生産性が向上する。

(もっと読む)

バス調停システム

【課題】優先度の低いバスマスタが優先度の高いバスマスタよりも先にバス転送要求を発行するような場合であっても、所望の優先順位に応じたバス調停を行うことができるようにする。

【解決手段】複数のバスマスタと、複数のメモリコントローラと、システムバスを介してメモリコントローラにアクセスする際にアクセスの競合を調停するバスアービタとを備えるバス調停システムであって、前記複数のバスマスタのバス転送要求を格納するキュー状態を前記バスアービタに通知し、前記通知されたキューの状態を予め設定した条件と比較して判定する。そして、判定結果に基づいてアクセスの競合を調停するタイミングを決定する。

(もっと読む)

データ処理システム及びプログラム開発システム

【課題】CPU又はDMA制御装置の一方にメモリアクセスが偏ることを能動的に抑制することができるデータ処理システムを提供することにある。

【解決手段】メモリへのアクセスにおいてCPU又はDMA制御装置の間でバス占有権を調停するバス調停回路は、前記CPUからの前記メモリに対するアクセスによるバス負荷を定期的に計測してそのバス負荷情報を前記DMA制御装置へ送信する。前記DMA制御装置は、バス調停装置から受取ったバス負荷情報に基づいて、データ転送制御のデータ転送量を少なくする制御を行う。これによれば、定期的に計測されたバス負荷に従ってDMA制御装置によるバス占有時間を動的に変更することができる。

(もっと読む)

データ処理システム

【課題】複雑・多機能化するデータ処理システムにおいて、データプロセッサがメモリインタフェースとは別にデータ転送を行うためのデータ転送インタフェースを実現する。

【解決手段】一のデータプロセッサ101に他のデータプロセッサ100との接続を可能にするためのインタフェース手段119を設け、このインタフェース手段に、一のデータプロセッサ内の内部バス108に他のデータプロセッサをバスマスタとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インタフェース手段を介して外部より当該他のデータプロセッサが直接操作できるようにする。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。

(もっと読む)

情報処理装置

【課題】システムバス、メモリバス、プロセッサバスの三種の各バスの使用効率を最大とする。

【解決手段】プロセッサバス111と、メモリバス112と、入出力デバイス105が接続されたシステムバス113とが三叉路接続コントロール手段103に接続される。三叉路接続コントロール手段は、プロセッサバス、メモリバス、システムバスのそれぞれのアドレスバスと制御バスが接続され、相互にアドレス及び制御信号を転送すると共に、データバス制御信号を発生するバス・メモリ接続コントローラを有する。又、この三叉路接続コントロール手段103は、プロセッサバス111、メモリバス112、システムバス113のそれぞれのデータバスが接続され、データバス制御信号に応じてこれらのデータバス上のデータを相互に転送するデータパスイッチを有する。

(もっと読む)

画像処理装置

【課題】ページ間の画像データ処理を行っていない間に動作クロックの供給を停止する画像処理装置の提供。

【解決手段】画像データ処理の際は、まずDMA制御回路14がDMA_STをアクティブとし、DMA_STを受けたCLK制御回路11がCLK2同期画像データ処理回路12へのCLK2供給を開始する。CLK2同期画像データ処理回路12およびCLK1同期画像データ処理回路13は、DMA_STがアクティブとなり、CLK2供給も開始されたことにより動作可能となり、入力される画像データを処理し、1ページ分のDMAデータ出力を行う。1ページ分のデータ出力を終えると、DMA制御回路14はDMA_STを非アクティブとし、画像データ処理を終了させる。これにより、CLK2同期画像データ処理回路12およびCLK1同期画像データ処理回路13は動作を停止させる。

(もっと読む)

通信バス用双方向単線式割り込みライン

スレーブ装置(106)がマスタ装置(104)へスレーブサービス要求を提示しマスタ装置からのマスタサービス要求を受理するために、マスタによってのみ通信開始可能なデータ通信バス(108)と共に双方向単線式割り込みライン(102)を用いる。マスタサービス要求を提示しない場合、マスタ装置(104)はマスタ割り込みインターフェイス(110)内のプル抵抗を介して割り込みライン電圧を設定することにより割り込みライン電圧をアイドル状態電圧に保持する。スレーブ及びマスタ装置はそれぞれ割り込みライン電圧をアイドル電圧からサービス要求電圧へと設定、又は引き上げることによりサービス要求を提示する。マスタサービス要求に応答する又はスレーブサービス要求の処理をマスタに開始させる場合、スレーブはスレーブ割り込みインターフェイス(112)によって割り込みラインをアイドル状態電圧に戻す。速度の遅いスレーブはこれにより保留中のマスタにより開始されたデータトランザクションへの準備をするのに十分な時間を得る。マスタは割り込みライン電圧の要求電圧からアイドル状態電圧への変化を検知し、データ通信バス(108)を介して準備の整ったスレーブ装置と通信を行う。 (もっと読む)

データ転送装置及びデータ転送システム

【課題】誤動作の発生を防止し、効率良くデータの転送を行うことができるデータ転送装置を提供する。

【解決手段】バス14を介してデータ転送を行うデータ転送装置であって、データをターゲットデバイス13へ書き込むデバイスコントローラ12と、前記バスを介して前記デバイスコントローラへ前記データをDMA転送すると共に、前記デバイスコントローラへ転送完了通知要求信号S11を出力するイニシエータコア11と、を備え、前記デバイスコントローラは前記転送完了通知要求信号を受信した場合、前記ターゲットデバイスへの前記データのすべての書き込みに伴い転送完了通知信号S12を出力する。

(もっと読む)

DMA転送装置

【課題】CPUの負荷を増大させることなく、USB受信部がデータの受信を終了したときにDMA制御部の転送を自動的に終了させられるDMA転送装置を提供する。

【解決手段】DMAC3が、USBファンクションモジュール2から送り出される連続するデータが正規の1パケットサイズよりも小さい場合に、データのRAM14への転送を終了(アボート終了)する。

(もっと読む)

OFDM送信装置とその信号分離装置およびメモリアクセス制御方法

【課題】メモリの利用効率を高めて電力消費および発熱を抑圧したOFDM送信装置とその信号分離装置およびメモリアクセス制御方法を提供する。

【解決手段】回路31〜3n、およびCPU1に規定のスロットタイミングを割り当てるのではなく、回路31〜3nから発生される読み出し要求に応えるかたちでメモリ2へのアクセス権を要求元の回路に割り当てる。各回路31〜3nの要求する速度により個々の処理に割り当てるスロットの割合を可変し、各回路31〜3nごとの速度の違いを吸収する。さらに、読み出し要求の無いタイミングではCPU1に無条件でアクセス権を与えることにより、CPU1のメモリアクセスに対する優先度を最も高くするようにした。

(もっと読む)

61 - 80 / 218

[ Back to top ]