Fターム[5B061RR03]の内容

Fターム[5B061RR03]に分類される特許

21 - 40 / 218

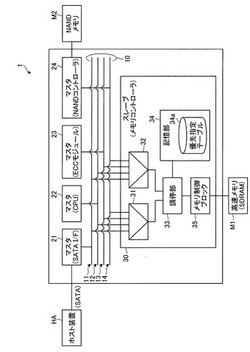

データ転送システム

【課題】動作効率を向上できるデータ転送システムを提供する。

【解決手段】1つの実施形態によれば、第1の速度でデータをそれぞれ転送する複数のラインを有するバスと、前記バスに接続された複数のマスタ装置と、前記バスに接続されたスレーブ装置とを備え、前記スレーブ装置は、前記バスにそれぞれ接続され、前記バスを介して前記マスタ装置から転送指示をそれぞれ前記第1の速度で受信する複数のスレーブインターフェースと、前記複数のマスタ装置の間における処理内容の関連性に依存した順番で前記複数のマスタ装置が優先順位付けされた優先順位情報に従って、前記複数のスレーブインターフェースで受信した転送指示の処理順を決定する調停部と、前記調停部により決定された処理順に従い、転送指示に応じた外部との間のデータ転送処理を前記第1の速度より速い第2の速度で行う処理部とを有することを特徴とするデータ転送システムが提供される。

(もっと読む)

画像形成装置、及び画像データ転送方法

【課題】同じ内部バスを介して複数の用途の画像データが並行して転送される状況に応じて、各用途の画像データの転送をより適切に制御するための技術を提供する。

【解決手段】PCIアクセスコントローラ12は、各ビデオ転送コントローラ34からデータ取得要求信号が出力される状況下において、LCDコントローラ21がLCD表示部22に動作用に供給するクロックLcdClk、水平同期信号LcdHsync、及び垂直同期信号LcdVsyncの周期を共に通常時よりも長くさせる。それにより、LCD表示部22用の画像データの転送頻度を抑え、各ビデオ転送コントローラ34への画像データの適切な転送を確実にする。

(もっと読む)

データ処理装置、画像形成装置、省電力制御方法、省電力制御プログラム及び記録媒体

【課題】本発明は、低電圧動作時に、低電圧では動作不可能なモジュールに対する不正アクセスに対して適切に対応する。

【解決手段】複合装置1は、ASIC16が、それぞれ独自の規定電圧を超える供給電圧の電力供給を受けることで動作可能状態となって機能動作するDDR−SDRAMコントローラ24、PCIeコントローラ31、SATAコントローラ32その他の複数のモジュールを備え、電源供給部40から供給電圧が複数の電圧に切り替えて電力供給される際に、供給電圧が規定電圧よりも低く動作停止状態となっているモジュールに対して、バスマスタからアクセスがあると、代理応答部33が、該モジュールに代わって該アクセスに対して所定の代理応答を該バスマスタに行う。

(もっと読む)

画像処理装置及び方法

【課題】データ転送中の任意のデータ間でコマンドに応じた処理を実行可能なデータ処理装置及びその方法を提供する。

【解決手段】それぞれが処理部を有する複数の処理ブロックが共通バスによって直列に接続された画像処理装置における当該複数の処理ブロックのそれぞれは、共通バスを介して当該処理ブロックに入力されたデータを用いた画像処理を、当該処理ブロックの処理部により行ない、共通バスを介して当該処理ブロックに入力されたコマンドに応じた処理を、当該処理ブロックの処理部に対して行ない、共通バスを介して第1の処理ブロックに入力される第1のコマンドについて、当該第1のコマンドの前に第1の処理ブロックへ入力されたデータに基づくデータ処理によるデータ出力が完了するまで、第1の処理ブロックから当該第1のコマンドを出力することを遅延させる。

(もっと読む)

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

調停装置、画像形成装置、調停方法及びプログラム

【課題】優先順位の異なる複数のDMACからの転送要求を調停するときに、システム全体のパフォーマンスを向上させる。

【解決手段】第1のライトDMAC15は、1ライン単位で入力されるデータを1ライン期間内にメモリに転送させる必要がある。アービタ113内の必要転送時間計算部121は、バースト長と、バス幅と、必要転送レートRaとから、要求されたデータの転送に必要な時間T2を計算する。また、ラインスタート信号により起動されるタイマーにより、1ラインの開始からの経過時間T1を計測する。T1の方がT2より長ければ、T1とT2が等しくなるまで、第1のライトDMAC15からの転送要求に対して、ウェイト要求信号をアサートする。

(もっと読む)

バス調停装置、バス調停方法

【課題】 バス調停装置がバス使用許可を与えようとした時に、バス使用要求信号を出力できなかったマスタは、予め設定したバス獲得回数の比率でバス使用権を精密に付与することが困難である。

【解決手段】 バススレーブの動作中は、予め設定したバス獲得回数の転送を行っていないバスマスタのバス使用要求信号が出力されるのを待つようにバス調停装置を動作させる。

(もっと読む)

半導体集積回路、データ処理装置

【課題】 回路規模を増大させることなく、アルゴリズムを効率よく実装することが可能な、プロセッサアレイ構成を提供する。

【解決手段】 プロセッサアレイにおける入出力制御手段間の経路の内少なくともひとつを、データ処理フローに合せて、所定の方向に多重に持たせることで、効率よく実装することが可能となる。また、上記所定の方向を多重化する代わりに、その方向とは反対方向の経路を省くことで、回路規模の増大を防ぐことを特徴とする。

(もっと読む)

ホスト装置、周辺装置、通信システム、および、通信方法

【課題】クロック信号に同期してデータ送受信を行う通信システムでは、ホスト装置がクロック信号の出力を停止すると、周辺装置からホスト装置へデータ転送ができず、周辺装置からホスト装置へ割込み要求を速やかに伝えることができない。

【解決手段】クロック信号の出力が停止している際に、周辺装置201からホスト装置200への割込み要求を、クロック信号用の信号線を用いることで、ホスト装置200へ伝える。ホスト装置200は、この割込み要求を受信するとクロック信号の出力を再開し、周辺装置201との間でデータの送受信を再開できるようにする。これにより、ホスト装置200からクロック信号の出力が停止している場合であっても速やかに周辺装置201からホスト装置へ割込み要求を伝えることが可能となる。

(もっと読む)

バス帯域モニタ装置およびバス帯域モニタ方法

【課題】各処理ブロックのプライオリティを設定するために有用な情報を取得することができるバス帯域モニタ装置およびバス帯域モニタ方法を提供する。

【解決手段】共通バスに接続され、共通バスを介して入力されたデータを記憶するバッファ部と、バッファ部に記憶されたデータに基づいて予め定められた処理を行う処理部と、バッファ部と処理部との間でのデータの受け渡しの状態に基づいて、共通バス上のデータの帯域を検出する検出部と、を備える。

(もっと読む)

データ転送装置、画像形成装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、複数のアプリケーションが動作する状態で適切なデータ転送を行うデータ転送装置、画像形成装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】複合装置1は、少なくとも画像データの主走査サイズが格納可能な複数のラインFIFO34a〜34nの状態を監視して、リード要求制御回路52が、データの格納されるメインメモリ8へのアクセス要求を調停するアービタに対するメモリリード要求の発行を、該ラインFIFO34a〜34nの監視結果に基づいて制御している。

(もっと読む)

複数のプロトコルのバスを有するバスシステム及びそれに使用されるバススイッチングデバイス

【課題】複数のプロトコルのバスシステムが混在するバスシステムであって,バスの配線量を抑制したバスシステムと,それに使用されるバススイッチデバイスを提供する。

【解決手段】第1のバスシステムと,第2のバスシステムと,第1のバス配線の第1及び第2の部分バス配線間または,第2のバス配線の第3及び第4の部分バス配線間を,接続する共通バス配線と,第1の部分バス配線と共通バス配線との間と第3の部分バス配線と共通バス配線との間とに設けられた第1のバススイッチデバイスと,第2の部分バス配線と共通バス配線との間と第4の部分バス配線と共通バス配線との間とに設けられた第2のバススイッチデバイスとを有し,バススイッチデバイスは,部分バス配線の電圧状態をそれぞれ監視し,メッセージが送信されていない電圧状態を検出した時に,第3及び第4の部分バス配線と前記共通バス配線とを接続する第2の接続状態にそれぞれ切り替える。

(もっと読む)

情報処理装置

【課題】プロセス単位で優先度を制御することによって情報処理装置全体の処理能力を向上させる。

【解決手段】データ転送のためのバス(25)と、それぞれプロセスを処理単位とする処理機能を有し、上記バスに対してデータ転送要求を発行可能な複数の機能モジュール(10,11,12,20,22,23)とを設ける。また、上記プロセス毎に設定されたプロセス識別情報を、当該プロセスを処理する上記機能モジュールに対応付けて保持可能なプロセス識別情報保持部(101,111,121,201,221,231)を設ける。さらに上記機能モジュールからのデータ送要求毎に、対応する上記プロセス識別情報毎の処理の優先順位を決定し、その優先順位に従って上記バスに対するデータ転送要求の競合を調停するバスアービター(26)を設ける。プロセス単位での優先順位制御を行うことで処理能力を向上させる。

(もっと読む)

コード読取装置

【課題】シンボルコードの読取開始からデコード結果が外部機器へ送信されるまでに要する時間を短縮することができるコード読取装置を提供する。

【解決手段】共通の共有23バスを介して共有メモリ24にアクセスするCPU21,22と、シンボルコードの光学読取を行って読取画像を生成する撮像素子25aと、共有バス23を介して読取画像を撮像素子25aから共有メモリ24へ転送するDMAC29により構成される。CPU21は、CPU22の指示に基づいて、共有メモリ24内の読取画像をデコードする。CPU22は、撮像素子25aによる光学読取を制御する撮像制御タスク、読取画像のデコードをCPU21に指示するデコード制御タスク、及び、デコード結果の送信を制御するデコード結果送信タスクのいずれか1つを選択的に実行し、撮像制御タスクがデコード制御タスクよりも優先され、デコード制御タスクがデコード結果送信タスクよりも優先される。

(もっと読む)

データ処理システム

【課題】 データ処理システムの消費電力をきめ細かく制御する。

【解決手段】 複数のマスターの各々は、データの転送要求とともにデータの転送速度を示すスピードグレード信号を出力する。調停回路は、複数のマスターからの転送要求およびスピードグレード信号を調停する。クロックイネーブル生成回路は、調停回路により調停されたスピードグレード信号に応じて、有効期間の比率が異なるクロックイネーブル信号を生成する。スレーブは、クロックイネーブル信号が有効なときにクロック信号を受けて動作し、調停回路により調停された転送要求に応じてデータを転送する。これにより、スレーブを動作させるクロック信号の周波数を転送要求毎に変更でき、スレーブの電力のきめ細かな制御を容易に実施できる。

(もっと読む)

中継装置およびプロセッサーシステム

【課題】処理の順序が定められたリクエストを効率よく中継する。

【解決手段】マスターデバイス(M1)とスレーブデバイス(S1,2)とをツリー型に接続してなるプロセッサーシステムにおいて、通信経路の分岐点に配置される中継器(TB3)は、処理の順序が定められたインオーダーリクエスト1,2,3が順に入力される際には、リクエスト1を下位側に転送して転送済みリクエスト1と分岐先が同じリクエスト2を下位側に転送し(T5〜T7)、転送済みリクエスト1,2と分岐先が異なるリクエスト3を待機させて転送待ちとし(T7〜T13)、転送済みリクエスト1,2に対するレスポンス1,2が返ってきてから待機させたリクエスト3を下位側に転送するから(T14)、処理の順序が定められたリクエストを効率よく中継することができる。

(もっと読む)

プロセッサーシステム

【課題】各デバイス間の通信を効率よく中継する。

【解決手段】マスターデバイス40とそれに対するスレーブデバイスとしての第1のスレーブデバイス50とを接続してデバイス間の通信を中継するクロスバースイッチ45と、マスターデバイス40および第1のスレーブデバイス50に対するスレーブデバイスとしての第2のスレーブデバイス60と第1のスレーブデバイス50とを接続してデバイス間の通信を中継する多段ブリッジ55とを備えて、クロスバースイッチ45と多段ブリッジ55との接続を介してマスターデバイス40と第2のスレーブデバイス60とを接続してデバイス間の通信を中継するから(経路(3))、各デバイス間の通信において通信対象となるデバイス以外のデバイスを経由する必要がなく、各デバイス間の通信を効率よく中継することができる。

(もっと読む)

ポンプ制御装置を結合する入出力システム、方法、および装置

【課題】ポンプ制御装置と異なるインターフェースおよび/または信号伝達形式を有し得

る制御装置とを結合するための入出力システム、方法、および装置を提供すること。

【解決手段】一実施形態では、入出力インターフェースモジュールは、プロセッサと、記

憶装置と、ポンプ制御装置と制御装置とを通信するための少なくとも2つのデータ通信イ

ンターフェースとを備える。入出力インターフェースモジュールは、制御装置から個別信

号を受信し、それに応じて信号を解釈し、ポンプ制御装置へパケットを送信することがで

きる。ポンプ制御装置は、パケットを読み込み、ポンプに適切な操作を行う。入出力イン

ターフェースモジュールは、ポンプ制御装置から受信したデータのパケットを解釈し、制

御装置へ対応する個別信号をアサートすることができる。

(もっと読む)

共通クロック方式の同期型シリアル転送回路

【課題】シリアルクロックの動作周波数が上限に達していても、新たなシリアルデータ信号線路を追加することなく、転送速度のさらなる高速化が可能な、共通クロック方式のシリアル転送回路を提供する。

【解決手段】シリアルデータ信号を伝送する線路として、従来のシリアルデータ信号線路に加えて、シリアルクロック信号を伝送する線路をも利用する。このとき、シリアルクロック信号を伝送する線路のインピーダンスを制御することによって、シリアルデータ信号の一部を表現する。

(もっと読む)

データ受信システムおよび割り込み実行方法

【課題】複数のデータ出力装置からの非同期の割り込み要求信号を用いて、欠落なく効率的に確実に、データ受信装置に任意のタイミングでデータを送信するデータ受信システムおよび割り込み実行方法を提供する。

【解決手段】複数のデータ出力装置からの複数のデータを一時的に保持するデータバッファ回路部と、割り込み信号を受信した際に、全てのデータ出力装置に対してデータが保持されているか否かを判断し、入力されているデータを順次受信する割り込みルーチン手段と、割り込み要求信号に応じてデータバッファ回路部からデータを取得し、データの優先順位を判断して並び替える優先データ判断回路部と、並び替えられた複数のデータを、一時的に保持する並べ替え済データバッファ回路部と、前記割り込み要求信号に応じて、前記並べ替え済データバッファ回路部からデータを取得するCPUと、を有することを特徴とするデータ受信システム。

(もっと読む)

21 - 40 / 218

[ Back to top ]