Fターム[5B079CC16]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 可変性をもたせるもの (66)

Fターム[5B079CC16]の下位に属するFターム

メモリを用いるもの (14)

Fターム[5B079CC16]に分類される特許

1 - 20 / 52

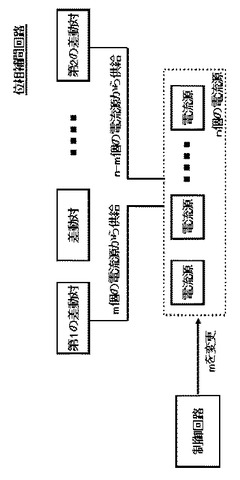

位相補間回路及びその設計方法

【課題】トランジスタのばらつきによる影響を抑制し、位相歪みを解消する位相補間回路を提供する。

【解決手段】位相補間回路は、位相の異なる入力波形を受け付ける複数の差動対を含み、複数の差動対のうち、第1の差動対及び第2の差動対の出力波形を合成する位相補間回路である。さらに、複数の差動対にバイアス電流を供給する電流源をn個含み、第1の差動対に供給するバイアス電流を、n個の電流源のうち、m個の電流源から供給可能であると共に、第2の差動対に供給するバイアス電流をn個の電流源のうち、n−m個の電流源から供給可能であって、n個の電流源が供給する電流は、予め定められた単位電流値を基準として、それぞれ重み付けがされている可変電流源と、出力波形の位相シフト量に基づいて、可変電流源のm個の電流源の数を変更する制御回路と、を備えている。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

中央処理ユニットをリアルタイムで監視するシステムおよび方法

1つまたは複数の中央処理ユニットをリアルタイムで監視する方法を開示する。本方法は、1つまたは複数のCPUに関連する状態データをリアルタイムで監視するステップと、状態データをフィルタ処理するステップと、フィルタ処理された状態データに少なくとも部分的に基づいて、1つまたは複数のシステム設定を選択的に変更するステップと含み得る。  (もっと読む)

(もっと読む)

LSIの電力低減のための適応的クロック位相制御方法および装置

【課題】消費電力を低減する。

【解決手段】クロック信号をデジタル回路に分配する方法、装置は、クロック信号を生成するステップと、制御信号に応じて、クロック信号の位相を遅延され、進められ、あるいはそのままとして、出力クロック信号を生成するステップと、を備える。クロック信号と出力クロック信号の間の遅延量あるいは進み量である位相差を、デジタル回路の電源電圧の大きさの時間的変動に応じて変化させる。

(もっと読む)

LSIシステム

【課題】入力された外部信号の波形で規定される論理をより確実に判定することが可能なLSIシステムを提供する。

【解決手段】LSIシステムは、第1の入力回路と、発振回路と、発振安定化回路と、システムクロック信号をカウントするフリーランカウンタと、第2の入力回路と、第1のキャプチャ信号が入力されたときのフリーランカウンタの第1のカウント値を保持するとともに、第2のキャプチャ信号が入力されたときのフリーランカウンタの第2のカウント値を保持するキャプチャ回路と、設定値を発振安定化回路に出力するとともに、設定値に対応した補正値を出力する補正回路と、キャプチャ回路に保持された第1のカウント値と第2のカウント値との差に補正値を加算した値に基づいて、第2の外部信号の波形のエッジの間隔で規定される論理を判定する判定回路と、を備える。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

リセット制御回路及びリセット制御方法

【課題】

クロック同期回路を含むシステム、特に、異常時のリセット動作について、クロック信号が、停止している場合や、異常状態の検出に対して要求されるリセット応答に比してその周期が長い場合に適切にリセット動作を行うことができるリセット制御回路、及びリセット制御方法の提供を目的とする。

【解決手段】

リセット要求信号RRに応じてリセット信号RSを出力制御するリセット制御回路200は、リセット要求信号RRに応じて、クロック出力待機期間DCの遅延でクロック出力信号RCを発生すると共に、クロック信号CKを変成して出力するクロック変成部210と、クロック出力信号RCに応じて、リセット出力待機期間Dの遅延でリセット信号RSを発生するリセット信号生成部220とを有している。

(もっと読む)

クロック信号生成装置及び方法

【課題】比較的小さな回路規模で、入力された多相クロック信号から所望の位相のクロック信号を生成する。

【解決手段】入力された多相クロック信号から所望の位相のクロック信号を生成する装置において、中間クロック生成器(11)は、多相クロック信号のいずれか一つを基準クロック信号として、基準クロック信号の複数周期を1周期とする多相中間クロック信号を生成する。第1の位相セレクタ(12)は、多相中間クロック信号のいずれか一つを選択する。第2の位相セレクタ(13)は、多相クロック信号のいずれか一つを選択する。ラッチ回路(14)は、第1の位相セレクタ(12)によって選択された中間クロック信号を、第2の位相セレクタ(13)によって選択されたクロック信号でラッチする。

(もっと読む)

タイミング制御回路および半導体記憶装置

【課題】タイミング信号の遅延量の変動を低減する。

【解決手段】周期T1を持つクロック信号CKaと、活性化信号ACTとを入力し、mを否負の整数、tdaをアナログ遅延素子による遅延量としたときにクロックからの遅延量がtd=m・T1+tdaとなる微調タイミング信号FTを発生するタイミング制御回路DLY1を有する。タイミング制御回路DLY1は、粗調遅延回路CDと微調遅延回路FDからなる。粗調遅延回路CDは、活性化信号ACTを受けてから、クロック信号CKaの立ち上がりエッジをカウントするカウンタを有し、クロック信号CKaの立ち上がりからの遅延量がm・T1である粗調タイミング信号CTを出力する。微調遅延回路FDは、複数のアナログ遅延素子を有し、粗調タイミング信号CTからの遅延量がtdaとなる微調タイミング信号FTを出力する。

(もっと読む)

クロック生成回路

【課題】簡易な回路構成で、周波数が定常的に揺らいでいるクロック信号を生成できるクロック生成回路を提供する。

【解決手段】直列に接続された奇数個のインバータinv1〜invNを有し、最終段のインバータinvNの出力が初段のインバータinv1に入力され、クロック信号を生成して出力するリングオシレータ11と、リングオシレータ11から出力される前記クロック信号が与えられ、分周して出力する分周回路12と、分周回路12の出力に基づいてオンオフ制御され、オン時はリングオシレータ11の加熱を行うヒータ14と、を備える。

(もっと読む)

遅延パルス発生回路

【課題】クロックパルスを用いずに入力パルスを遅延させた出力パルスを生成する。

【解決手段】外部からの入力パルス信号に応じて動作を開始し、その動作の開始から第1の遅延時間T1後に出力信号を変化させる第1の遅延回路102と、その出力信号に応じて、動作の開始から第1の遅延時間T1後に動作を開始し、その動作の開始から第2の遅延時間T2後に出力信号を変化させる第2の遅延回路104と、を備え、その出力信号の変化に応じて入力パルス信号を遅延させた出力パルス信号を生成する。

(もっと読む)

クロック信号供給回路

【課題】クロック信号が安定するまでの待ち時間を設定するレジスタの初期値を任意に変更可能としたクロック信号供給回路を提供する。

【解決手段】待ち時間設定部は、起動時の初期値に基づいて、待ち時間設定信号を選択するための選択信号を出力するデータ保持回路9a,9bと、選択信号に基づいて待ち時間設定信号を選択する選択回路と、データ保持回路9a,9bの初期値を任意に設定可能とする初期値設定回路21,22,23,24,25とを備えた。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

クロック遅延補正回路

【課題】クロック分配回路のクロック遅延を補正するクロック遅延補正回路で固定遅延手段を除き、設計時における設計検証を容易にする。

【解決手段】クロック遅延補正回路10は、分配クロックCLKの周期を示す周期データを生成する周期データ生成手段11と、可変遅延時間を持ち分配クロックCLKを遅延して出力クロックCOUT1を生成する可変遅延回路121と、出力クロックCOUT1の位相と基準クロックCREF1の位相とを比較する位相比較回路122と、位相比較回路122の比較結果に従ってカウントUPするカウンタ123とを有し、カウンタ123のカウント値で可変遅延回路121の遅延時間を制御する。

(もっと読む)

半導体集積回路

【課題】複数の順序回路として少なくともレベルセンス型順序回路を用いたシステムにおいて、動作周波数を高めると共に、信頼性を向上させる。

【解決手段】マイクロコンピュータ(1)は、クロック供給元とされるクロック発生回路(2)と、クロック信号CLKに同期動作する機能モジュールと、機能モジュールに含まれ、クロック供給先とされるレベルセンス型順序回路(12〜14)と、クロック信号をレベルセンス型順序回路に伝播するクロック供給系(11)等とを備える。クロック供給系は、クロック発生回路から出力されるクロック信号を複数の分岐を介して末端に伝播するクロック配線(20)を有する。クロック配線の途中には、少なくともパルス生成回路(26,28,29)が配置される。パルス生成回路は、レベルセンス型順序回路の入力動作期間の終点を規定するクロック信号の立ち下がりエッジの変化タイミングを可変とする。

(もっと読む)

スペクトラム拡散クロック制御装置及びスペクトラム拡散クロック発生装置

【課題】SSC機能のオン・オフを制御可能とし、周波数の過渡的な変化なしに、SSC機能のオン・オフの滑らかな遷移を可能とする装置の提供。

【解決手段】入力クロック信号を入力し、位相の可変制御する位相制御信号に応じて出力クロック信号の位相を可変させる位相補間器4に対して位相制御信号を生成する制御回路3に、カウント動作の停止を制御するカウント動作制御信号を出力するカウント動作制御回路31を備える。カウント動作制御回路31は、カウンタ22、23のカウント値26、27を入力し、SSC制御端子8から供給される制御信号が停止を示し、カウンタ22、23のカウント値26、27がともに初期値(=0)であるときに、カウント動作制御信号32をカウント停止を示す値に設定する。

(もっと読む)

デジタルDLL回路

【課題】信号の立ち上がり側と下がり側の遅延は個別に制御でき、クロックのデューティーずれやデータ信号の立ち上がり/立ち下がりの遅延差を補償することができるデジタルDLL回路を提供する。

【解決手段】信号の立ち上がりエッジ側遅延指定のための第1遅延指定値を保持する第1レジスタ11、信号の立ち下がりエッジ側遅延指定のための第2遅延指定値を保持する第2レジスタ12、信号の立ち上がり側と下がり側の遅延を個別に制御可能なデジタル制御可変遅延回路13、および可変遅延回路13の立ち上がり側遅延と立ち下がり側遅延をそれぞれ第1レジスタ11の第1遅延指定値および第2レジスタ12の第2遅延指定値に維持するよう制御を行う制御回路14を有する。

(もっと読む)

1 - 20 / 52

[ Back to top ]