Fターム[5C006FA13]の内容

Fターム[5C006FA13]に分類される特許

1 - 20 / 204

画像表示装置および画像表示装置の駆動方法

【課題】立体表示に利用される眼鏡式の画像表示装置において、パネル温度などの要因によって変化する液晶応答時間に応じて、クロストークを抑えた最適な立体表示を行う。

【解決手段】液晶パネル37に送信される画像データを画像符号回路16で圧縮して符号化し、画像復号化回路35で復号化することで、画像データの転送レートを上げ、表示パネルにおける走査期間を短縮する。上記符号化を行う際の圧縮率は、温度センサー31によって検出されたパネル温度に基づいて決定される。

(もっと読む)

画像表示装置の制御方法

【課題】種々の原因により表示処理部の誤動作が発生した場合でも、必要最小限の時間で表示処理の正常化が可能となる画像表示装置の制御方法等を提供する。

【解決手段】第1の表示処理部20及び第2の表示処理部30を有するプロジェクター10は、第1の表示処理部20の初期設定を行い、第1の表示処理部20の初期設定状態を検査する。プロジェクター10は、第1の表示処理部20の初期設定状態が異常であると検出されたとき、第1の表示処理部20の再初期設定を行う。また、プロジェクター10は、第2の表示処理部30の初期設定を行い、第2の表示処理部30の初期設定状態を検査する。プロジェクター10は、第2の表示処理部30の初期設定状態が異常であると検出されたとき、第2の表示処理部30の再初期設定を行う。表示処理部毎に、初期設定状態を検査し、再初期設定を行うことで、表示処理の正常化に要する時間を短縮する。

(もっと読む)

カラー表示方法およびカラー表示装置

【課題】表示パネルを3枚積層した反射型カラー表示装置の電子ペーパーの特性に適した画質補正を行い、表示品質を向上するカラー表示方法およびカラー表示の実現。

【解決手段】3枚の表示パネルを積層した反射型カラー表示素子10と、3原色の画像データに基づいてカラー表示素子を制御する駆動制御回路29と、を有するカラー表示装置であって、駆動制御回路は、3原色の画像データを色空間画像データに変換する色空間変換部31と、画像の明度、色相および彩度に関する評価基準に基づいて、画像を複数の型に分類する分類部32と、色空間画像データの明度を、分類した型ごとの補正特性にしたがって補正する明度補正部33と、明度補正した色空間画像データの彩度を補正する彩度補正部34と、彩度補正した色空間画像データを3原色の画像データに変換する3原色変換部36と、を有する。

(もっと読む)

直視型表示装置

【課題】本発明は、表示画面が明るく、かつ、信号量の増加を抑えた直視型表示装置を提供する。

【解決手段】直視型表示装置1は、補色関係にあるサブピクセルの対で輝度を表現する各画素が構成され、複数の画素が集合した色表現単位で1色を表現する表示素子20を備えるものであって、入力された映像信号における複数の画素の画素値を色表現単位の各サブピクセルの信号レベルに変換する変換式によって、映像信号を直視型表示装置用映像信号に変換する映像信号変換手段10を備え、表示素子20が、映像信号変換手段10によって変換された直視型表示装置用映像信号が示す映像を表示する。

(もっと読む)

駆動用集積回路および電子機器

【課題】端子数が少なく、かつ、画像信号および制御信号を高速に受信して電気光学装置を駆動することができ、さらに耐ノイズ性に優れた駆動用集積回路を提供する。

【解決手段】 レシーバー61、62および63は、差動形式の画像信号GD、画素クロックPCLKおよび時間多重制御信号CDを各々受信する。画像信号受信部31は、レシーバー62により受信された画素クロックPCLKによりレシーバー61により受信された画像信号をサンプリングし、電気光学装置を駆動する画像信号VIDを発生する。受信バッファー32は、レシーバー62により受信された画素クロックPCLKによりレシーバー61により受信された時間多重制御信号をサンプリングして記憶する。駆動制御部33は、同期信号検知部301、コマンド検知部302により、受信バッファー32内の時間多重制御信号に含まれる同期信号、コマンドを検知し、電気光学装置の駆動制御を行う。

(もっと読む)

映像信号処理回路、該処理回路に用いられる映像信号処理方法、及び画像表示装置

【課題】伝送フォーマットに無効ビットが存在する場合でも、EMIの放射レベルが軽減される映像信号処理回路を提供する。

【解決手段】映像信号処理回路12では、無効ビット極性設定手段(たとえば、入力映像信号判定部42及び無効ビット制御部43)により、出力映像信号vaの伝送フォーマットに、入力映像信号inを構成するデータに対応するデータのない無効ビットが存在する場合、入力映像信号inの階調データの“0”及び“1”の数が計数されて“0”の数と“1”の数との大小が比較判定され、この判定結果に基づいて無効ビットの極性(“0”又は“1”)が設定される。そして、無効ビットの極性が設定された出力映像信号vaが、映像信号線13を経て伝送される。

(もっと読む)

映像表示装置

【課題】フレームレートコンバータ回路とタイミングコントロール回路とがそれぞれ別個の回路基板に設けられることによる不都合が生じにくい映像表示装置を得る。

【解決手段】本発明の実施形態にかかる映像表示装置は、筐体と、表示部と、壁部と、第一の回路基板と、第二の回路基板と、を備える。表示部は、表示画面を有し、筐体内に少なくとも一部が収容される。壁部は、表示部の表示画面の反対側に位置される。第一の回路基板は、壁部の表示画面の反対側の表面上に位置され、この第一の回路基板には、入力された信号から少なくとも映像データを出力する入力信号処理回路が設けられる。第二の回路基板は、表面上に位置され、この第二の回路基板には、フレームレートコンバータ回路と当該タイミングコントロール回路とが設けられる。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

タイミングジェネレーター、撮影装置、ドットクロック出力方法

【課題】ドットクロックの出力数を数えるカウンターのオーバーフローを回避する。

【解決手段】被写体を撮影する撮影センサーのフレームレートを示す情報を取得するフレームレート情報取得部と、前記撮影センサーの出力データに基づいて生成された前記被写体の像を示す画像データを表示する際の同期信号であるドットクロックの出力数をラインごとの表示周期である水平同期期間ごとに数えるカウンターを有する表示部に前記ドットクロックを出力する表示制御部であって少なくとも前記撮影センサーのフレームレートに応じて長さが変動する前記水平同期期間内に第一の周期で前記ドットクロックを出力する場合の前記ドットクロックの出力数が前記カウンターの上限値を超える可能性があるか否かを判定し前記可能性があると判定される場合に前記ドットクロックの周期を前記第一の周期から前記第一の周期より長い第二の周期に切り換えて出力する表示制御部と、を備える。

(もっと読む)

表示装置及び画像データの転送方法

【課題】処理能力を上げることなく画像データの転送に必要とする処理時間の短縮を図った表示装置及び画像データの転送方法を提供する。

【解決手段】CPU4が、バイパスライト信号をGDC6に対して出力する。その後、CPU4は、ROM5及びGDC6の双方に対してリード信号を出力する。ROM5は、リード信号の出力に応じてデータバス8に対して画像データを出力する。GDC6は、リード信号の出力に応じてデータバス8に出力される画像データをCPU4を経由せずに直接読み取って、その読み取った画像データをVRAM7に書き込む。

(もっと読む)

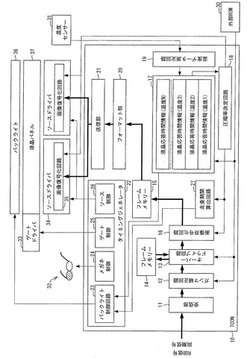

表示装置、及び、表示方法

【課題】映像を高フレームレートでスムーズに表示することができ、映像の高解像度化に対応可能な表示装置、及び、表示方法を提供する。

【解決手段】表示装置1は、入力映像の映像フォーマットを判別するフォーマット判別部52と、入力映像をフレームメモリー55に展開してフレームレート変換を行う映像処理部54と、所定の表示解像度で画像を表示する液晶ライトバルブ3と、フォーマット判別部52により判別した映像フォーマットに対応して、映像処理部54による処理後の映像を液晶ライトバルブ3の表示解像度に適合した映像に変換し、液晶ライトバルブ3に表示させる駆動制御部56と、を備えている。

(もっと読む)

画像データ伝送システムおよび電子機器

【課題】画像データを伝送する伝送システムの消費電力を低減する。

【解決手段】送信部1は、所定の単位の個数と所定の単位の伝送期間との積によって定義される、1フレームの画像の伝送のための予め定められた伝送期間内に、複数のデータ信号を順次出力する。一方、送信部1は、上記の予め定められた伝送期間のうちの、データ信号を含まない所定の単位の伝送時間の合計に等しい期間に制御信号を出力する。この期間が送信部1のスリープモード期間に対応する。予め定められた伝送期間に対するスリープモード期間の割合が、予め定められた伝送期間に対する、制御信号の伝送期間および制御信号の伝送のためのマージン期間との合計の割合よりも大きくなるように、スリープモード期間が設定される。

(もっと読む)

液晶表示装置

【課題】液晶パネルの駆動電圧値を複数フレーム単位に制御する場合であっても、液晶パネルの焼き付きを確実に防止することのできる「液晶表示装置」を提供することである。

【解決手段】液晶パネル25を有する表示ユニット20と、画素毎の階調値を表示ユニット20に供給する画像データ出力ユニット10とを有し、液晶パネル25の各画素に印加される前記階調値に基づいた駆動電圧値の正負の極性をフレーム毎に反転させるようにした液晶表示装置であって、画像データ出力ユニット10は、第1フレームグループFG1の各画素についての階調値に基づいた駆動電圧値の全フレームでの累積値が、第2フレームグループFG2の対応する画素についての駆動電圧値の全フレームでの累積値によって相殺されるように、第2フレームグループの各フレームにおける各画素の階調値を決定する階調値決定手段11を有する構成となる。

(もっと読む)

半導体回路及び半導体回路の信号取込方法

【課題】異なる入力方式で入力される信号を入力方式に応じて適切に取り込むことができる、半導体回路及び半導体回路の信号取込方法を提供する。

【解決手段】差動入力方式の場合には、差動入力回路16は、P側入力端子12に入力されたデータ信号及びN側入力端子14に入力されたデータ信号が入力される差動アンプ30の出力信号outから、DFFN32がクロック信号の立ち下がりのタイミングでEVENデータを取り込む。また、出力信号outから、DFF34がクロック信号の立ち上がりのタイミングでODDデータを取り込む。シングル入力方式の場合には、シングル入力回路18は、P側入力端子12に入力されたODDデータを取り込むためのデータ信号からDFF44がODDデータを取り込むと共に、N側入力端子14に入力されたEVENデータを取り込むためのデータ信号からDFF45がEVENデータを取り込む。

(もっと読む)

液晶駆動装置

【課題】アクセス効率を従来よりも高める液晶駆動装置を提供すること。

【解決手段】本発明の液晶駆動装置では、RAM5をL個のバンク(Lは1と素数以外の整数)に分割し、LがM×N(M、Nは2以上の整数)となり、且つ、M×Nの整数倍がX×Y(X、Yは4以上の整数)になるように、MとNとを決定し、表示パネルの(X×Y)個の画素の各々とそれに隣接する画素とに対するバンクが異なるように、前記(X×Y)個の画素に対して(M×N)個のバンクを割り当てる。これにより、CPU1又はLCD制御装置4がラインアクセス(水平アクセス、垂直アクセス)、ウィンドウアクセスを行う場合、(M×N)個のバンクのうちの隣接する2つのバンクが同一バンクではないため、隣接する2つのバンクが連続してアクセスされることがなく、LCDアクセスが割り込まれてもCPUアクセスを行うためのコマンドの処理待ち状態が減る。

(もっと読む)

表示装置、信号線ドライバ、及び、データ転送方法

【課題】表示装置において、映像データ及び制御信号を供給するために必要な配線の数を減らし、走査線ドライバに供給される制御信号が映像データを供給するデータ伝送線に及ぼすノイズの影響を無くす。

【解決手段】液晶表示装置1が、タイミングコントローラ2と液晶表示パネル3と複数のデータドライバ4とゲートドライバ5とを備えている。タイミングコントローラ2は、複数のデータドライバ4のうちの特定ドライバ4L、4Rに制御データを供給する。特定ドライバ4L、4Rは、制御データに応答してゲートドライバ5を制御するゲートドライバ制御信号を生成し、ゲートドライバ制御信号をゲートドライバ5に供給する。

(もっと読む)

表示装置の駆動回路

【課題】カスケード信号の遅延時間とシステムクロックのクロック周期との関係によらず、データドライバ間のデータの連続性を保つことができる駆動回路を提供する。

【解決手段】駆動回路100のデータドライバNに内部カウンタ301を備え、内部カウンタ301は、初段のデータドライバ1が表示データの先頭信号を読み込む際にリセットされ、前段のデータドライバN−1からカスケード信号(CASCADE)が入力され、カウンタ値が第1の設定値に等しくなった場合に、内部カウンタ301がリセットされるとともに、自段のデータドライバNにおける表示データの読み込みが開始され、カウンタ値が(2)式で求められる第2の設定値に等しくなった場合に、カウンタ部300は、次段のデータドライバN+1にカスケード信号を入力するように構成した。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

投影装置及びその制御方法

【課題】多画素の画像を分割して台形補正処理を並列に行うことにより、処理に要する時間を短縮する、または画質劣化を低減する。

【解決手段】1つの投影画像を複数の分割画像に分割し、分割された複数の分割画像に対して、それぞれに係る補正量の台形補正を適用し、アドレス構造を有する記憶領域に記憶させる。このとき、画像が記憶される記憶領域のアドレスは、アドレス順に読み出した際に、台形補正が適用された1つの画像として投影される際の走査順となるように決定される。

(もっと読む)

1 - 20 / 204

[ Back to top ]