Fターム[5C024GX02]の内容

光信号から電気信号への変換 (72,976) | 撮像素子の細部(構造) (7,971) | セル構造 (7,384) | 受光素子 (4,937)

Fターム[5C024GX02]の下位に属するFターム

フォトダイオード (3,306)

フォトトランジスタ (81)

光導電体 (579)

赤外線検出素子 (114)

蛍光体層(X線変換用等) (143)

電歪素子、圧電素子(超音波変換用) (3)

液晶層 (5)

誘電体層 (26)

受光部及び垂直CCDで感光

Fターム[5C024GX02]に分類される特許

141 - 160 / 680

レンズアレイ積層体及びその製造方法、並びに撮像ユニット集合体及びその製造方法

【課題】レンズアレイの各レンズ部と、それに対応するベースの素子とを高精度に位置あわせしてレンズアレイをベースに積層接合したレンズアレイ積層体、及び撮像ユニット集合体を提供する。

【解決手段】複数のレンズアレイを積層して一体に接合してなるレンズアレイ積層体の製造方法であって、前記レンズアレイは、1次元又は2次元の所定の並びに配列された複数のレンズ部と、これらのレンズ部と一体に形成され、これらのレンズ部を相互に連結する基板部と、を有しており、前記レンズアレイを、その表裏の面をそれぞれ成形する一対の型を用いて形成し、一つの前記レンズアレイ、又は複数の前記レンズアレイが積層接合された積層体をベースとして、該ベースの一面をその面を成形した型で保持すると共に、該ベースに積層接合される前記レンズアレイの該ベースとの接合面とは反対側の面をその面を成形した型で保持し、その状態で該ベースと該レンズアレイとを積層接合する。

(もっと読む)

固体撮像装置

【課題】本発明は、撮像領域の中央部に位置する行の単位画素内の光電変換手段における信号蓄積時間が最も短く、撮像領域の上下端に位置する行に向かって信号蓄積時間が長くなるように行選択を行うことを特徴とする。

【解決手段】単位画素11が二次元の行列状に配置された撮像領域10と、単位画素を行単位で駆動し、駆動される単位画素内の光電変換手段における信号蓄積時間を設定する垂直ライン駆動手段と、信号蓄積時間を行単位で可変制御する蓄積時間制御回路23とを具備する。

(もっと読む)

固体撮像素子、それを備えたカメラ、および、固体撮像素子の駆動方法

【課題】フレームレートを高めつつ、スミア段差の発生を防止する。

【解決手段】画素部は、切出領域301とそれ以外の不要領域302とに区画されている。画素部では、行毎に、第1配線104および第2配線105の両方または一方が設けられている。不要領域302では、画素毎に設けられたゲート電極103が、行毎に設けられた第1配線104に行単位で共通に接続されている。切出領域301では、画素毎に設けられたゲート電極103が、行毎に設けられた第2配線105に行単位で共通に接続されている。

(もっと読む)

固体撮像素子の製造方法

【課題】光の利用効率の高い固体撮像素子を製造するにあたって、電極パッドに腐食が無く、外部との電気的接続が良好で信頼性の高い固体撮像素子を製造する方法を提供すること。

【解決手段】半導体基板1表面に設けた複数の光電変換素子2の受光部に対応して該受光部に達する複数の凹部5を有する絶縁層4を該基板表面に形成し、該絶縁層の凹部を除く表面に外部との電気的接続のための電極パッド3を設け、該絶縁層の屈折率より高い屈折率を有する樹脂7にて該凹部を充填した固体撮像素子の製造方法であって、前記電極パッドを被覆し、かつ、該凹部を露出する保護膜6を形成する工程と、該凹部に高屈折率樹脂を埋め込む工程と、前記保護膜を除去する工程と、を上記の順に実行する。

(もっと読む)

固体撮像素子

【課題】画素ブロックにおける最初に読み出される画素の信号とその画素ブロックにおける他の画素から読み出される信号とのばらつきを、低減する。

【解決手段】垂直走査回路は、n行目の画素ブロック20の転送トランジスタTX1,TX2を互いに異なるタイミングで順次オンさせる。垂直走査回路は、各転送トランジスタTX1,TX2のオン期間の前の所定期間(期間t2−t3及び期間t5−t6)にn行目のリセットトランジスタRESをオンさせる。n行目の画素ブロックの転送トランジスタTX1,TX2のうち最初にオンされる転送トランジスタTX1のオン期間の直前のn行目のリセットトランジスタRESのオン期間t2−t3の長さは、n行目の画素ブロック20の他の転送トランジスタTX2のオン期間の直前のn行目のリセットトランジスタRESのオン期間t5−t6の長さと同一のTにされる。

(もっと読む)

固体撮像装置及びその駆動方法

【課題】ブルーミングを抑制することができる固体撮像装置を提供することを課題とする。

【解決手段】入射光に応じた電荷を生成して蓄積するための光電変換部と、電荷を蓄積するためのフローフィングディフュージョン部と、光電変換部に蓄積された電荷をフローフィングディフュージョン部へ転送するための転送トランジスタと、フローフィングディフュージョン部に蓄積された電荷に応じた電圧をリセットするためのリセットトランジスタと、光電変換部に電荷を蓄積中、転送トランジスタのゲートには電荷を転送する転送電位と電荷を非転送とする非転送電位との中間となる第1の電位を有するパルスを間欠的に印加し、リセットトランジスタのゲートにはフローフィングディフュージョン部の電圧をリセットするパルスの電位よりも低く、第1の電位よりも高い第2の電位を印加する駆動回路とを有する。

(もっと読む)

放射線撮像装置

【課題】結合後の欠損画素である結合欠損画素を適正に監視することができる放射線撮像装置を提供することを目的とする。

【解決手段】結合(ビニング)の対象となる行列方向に隣接する複数の画素のいずれかの画素において欠損画素が含まれている場合には、ビニング処理後(結合後)のビニング画素(結合画素)をビニング欠損画素(結合欠損画素)としてビニング欠損画素検出部23は処理する。そのビニング欠損画素の検出後に、検出されたビニング欠損画素のデータバスラインの読み出し方向の下流側に隣接するビニング画素の欠損判断を優先的にビニング欠損画素検出部23は行うことで、ビニング処理後(結合後)の欠損画素であるビニング欠損画素(結合欠損画素)を適正に監視することができる。

(もっと読む)

固体撮像装置

【課題】列間引き読み出し時に間引きされる画素の列に対応した列回路の動作を停止させることができ、列間引き読み出し時における消費電力を低減することができる固体撮像装置を提供する。

【解決手段】入射光を信号電荷に変換する光電変換手段と、信号電荷を増幅する増幅手段と、信号電荷をリセットするリセット手段と、増幅手段の出力を選択的に出力信号線に出力する選択手段と、を有する画素を、2次元の行列状に複数配列した画素部と、画素部の列単位の出力信号線に流れる電流を一定にする負荷手段と、列単位の出力信号線を複数本単位で接続する第1のスイッチ素子と、負荷手段と列単位の出力信号線とを接続する第2のスイッチ素子と、出力信号線の画素信号成分をアナログ信号処理するアナログ処理回路と、アナログ信号処理された画素信号の出力を制御する水平走査部と、第1のスイッチ素子と第2のスイッチ素子とを制御するモード設定部と、を備える。

(もっと読む)

マイクロレンズアレイの製造方法及びフォトマスク

【課題】斜め方向でのレンズ間ギャップが0.2μm以下のマイクロレンズアレイのレンズ間ギャップの製造バラツキを小さくする。

【解決手段】市松状に配置した第1のマイクロレンズを、第1のフォトマスクのパターンを感光性レンズ材料層に露光し現像することにより形成する第1の工程と、前記第1の工程において選択されなかった第2のマイクロレンズを市松状に配置した第2のマイクロレンズを、第2のフォトマスクのパターンを感光性レンズ材料層に露光し現像することにより形成する第2の工程とを有し、前記第1のフォトマスクに、八角形の遮光パターンと、前記遮光パターンの斜め方向の間の間隔に位置する光透過率が100%の帯状の間隙パターンと、前記遮光パターンと前記帯状の間隙パターン以外の領域であって半透過性を有する半透光部とを有するフォトマスクを用いてマイクロレンズアレイを製造する。

(もっと読む)

撮像装置、撮像システム及びそれらの制御方法

【課題】 素子サイズの寸法を小さくしても1/fノイズによる取得画像に対するアーチファクトを低減することが可能な撮像装置又は撮像システムを提供する。

【解決手段】 撮像装置は、画素を行列状に複数備えた検出部101と、読出回路103と、A/D変換器104と、画素データの補正処理を行う補正処理部400と、制御部108と、を有する。ここで、読出回路103は、リセット手段SRを有し、制御部108は、読出回路103が所定行の信号処理動作の期間内に複数のリセット信号をA/D変換器104に出力し、A/D変換器104が期間内に複数のリセット信号をデジタルデータである複数のリセットデータに変換し、補正処理部400が期間内にA/D変換器104から出力された複数のリセットデータを加算平均処理し、期間内にA/D変換器104から出力された画素データと加算平均処理されたリセットデータとを減算処理するように、制御を行う。

(もっと読む)

固体撮像素子及びその製造方法

【課題】画素の微細化に対して有効なチャネルストップ部を形成でき、混色現象等を防止して画質の良好な固体撮像素子を実現する。

【解決手段】チャネルストップ部90は、複数回の不純物イオン注入工程によって形成されており、半導体基板100の深さ方向(バルク深さ方向)に多段階の不純物領域90A、90B、90C、90Dが形成される。チャネルストップ部90は、多段階の不純物領域90A、90B、90C、90Dが、半導体基板表面側に位置するほど不純物濃度を高くし、最下層90Dの底が光電変換部10Bより下方のオーバーフローバリア領域92と接触するように、光電変換部10Bの底の深さより深く形成される。

(もっと読む)

固体撮像装置

【課題】光の経路に配線が存在する場合でも、光の減衰や回折の影響を最小限に留め、画素の微細化を図ると同時に感度の向上、混色の防止を図ることのできる固体撮像装置を提供する。

【解決手段】配線及び拡散防止膜による光の回折光が通過する位置に拡散防止膜を適宜配置することで、拡散防止膜による光の減衰を最小減にとどめ、かつ、回折光による感度低下を抑制することや、隣接画素への信号の漏れ込みを低減することを可能とする。

(もっと読む)

固体撮像装置

【課題】画素の暗電流を増大させることなく、画素縮小化による受光性能の低下を抑制した高画質の固体撮像装置を提供することを課題とする。

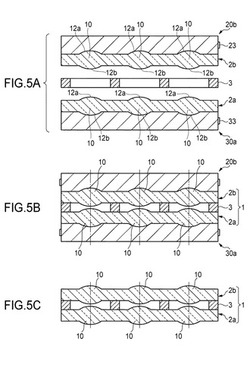

【解決手段】複数の画素を有し、前記複数の画素の各々は、半導体基板中の受光部(3)と、前記受光部の上に設けられる層間絶縁膜(6)と、前記受光部の上方において前記層間絶縁膜内に設けられ、前記受光部と直接接しない層内レンズ(10a,10b)とを有し、前記層内レンズは、前記層間絶縁膜より高い屈折率を有し、前記受光部の上部から入射する光を集光する作用を有し、前記層内レンズは、前記画素内で一様な厚さを有することを特徴とする固体撮像装置が提供される。

(もっと読む)

固体撮像素子及びその製造方法、撮像装置

【課題】レンズ形状の制御を容易にすることによって、容易に製造が可能であると共に、感度等の特性が良好である構成の固体撮像素子を提供する。

【解決手段】半導体基板1に形成された受光部2と、半導体基板1の上に形成された絶縁層9と、受光部2の上方の絶縁層9に形成された孔部の内部の外側に塗布により形成され、絶縁層9と共に導波路10のクラッド部を構成する膜11と、絶縁層9の材料及び塗布により形成された膜11の材料よりも屈折率の高い材料から成り、孔部の内部の内側に形成された導波路10のコア部12と、孔部の底部において、塗布により形成された膜11とコア部12との界面によってレンズ面10Aが形成され、導波路10と一体化している層内レンズとを含む、固体撮像素子を構成する。

(もっと読む)

固体撮像素子、撮像装置、撮像方法

【課題】シンプルな駆動方法によりダイナミックレンジを拡大させることが可能な固体撮像素子を提供する。

【解決手段】画素部100を複数有する固体撮像素子10であって、画素部10は、光電変換部3と、光電変換部3で発生した電荷を蓄積可能な不揮発性メモリトランジスタMT1,MT2を有し、光電変換部3をリセットした後、不揮発性メモリトランジスタMT1のゲート電極CG1に第一の電圧を印加し、不揮発性メモリトランジスタMT2のゲート電極CG2に第一の電圧とは異なる大きさの第二の電圧を印加して光電変換部3で発生した電荷をフローティングゲートFG1,FG2に蓄積する制御部40と、フローティングゲートFG1,FG2に電荷が蓄積された後に、フローティングゲートFG1に蓄積された電荷に応じた第一の撮像信号と、フローティングゲートFG2に蓄積された電荷に応じた第二の撮像信号とを読み出す読み出し回路20とを備える。

(もっと読む)

放射線撮影装置及びその制御方法

【課題】変換素子のリセットを目的とする光を照射する光源の負荷や消費電力、発熱量を低減するとともに、変換素子の劣化の促進を抑制する。

【解決手段】変換素子を有する画素を複数含み構成され、被写体300を透過した放射線111bに基づく放射線画像を取得するための平面検出器120と、変換素子に対して当該変換素子が感知可能な波長帯域の光を照射する光源130と、前記放射線画像の撮影を行う前に、放射線を用いずに撮影されたオフセット画像から基準値を検出し、当該基準値に基づいて変換素子を飽和状態とする光を光源130から照射する制御を行う制御部150を備える。

(もっと読む)

固体撮像素子、撮像装置、撮像方法

【課題】不揮発メモリトランジスタの閾値電圧のばらつき等を抑えて高画質化を図ることが可能な固体撮像素子を提供する。

【解決手段】画素部100を複数有する固体撮像素子10であって、画素部100は、光電変換部3と、光電変換部3で発生した電荷を蓄積可能なフローティングゲートFG1,FG2をそれぞれ含む不揮発性メモリトランジスタMT1,MT2とを有し、光電変換部3のリセット後に光電変換部3で発生した電荷をフローティングゲートFG1,FG2に蓄積し、次いで、露光期間中に光電変換部3で発生した電荷をフローティングゲートFG1に蓄積する制御部40と、フローティングゲートFG1に蓄積された電荷に応じた第一の信号と、フローティングゲートFG2に蓄積された電荷に応じた第二の信号との差分を撮像信号として読み出す読み出し回路20とを備える。

(もっと読む)

固体撮像素子の白キズ補正装置

【課題】撮像画像における被写体の再現性を大きく損なうことなく、固体撮像素子の欠陥画素に起因して生じる白キズを補正する技術を提供する。

【解決手段】固体撮像素子を遮光しかつ一定の露光時間で撮像を行った場合において、固体撮像素子の複数の画素の各々を注目画素とし、当該注目画素の周辺画素の画素値の平均値と当該注目画素の画素値との差分から当該注目画素が撮像画像にて白キズとなって現れる欠陥画素であるか否かを判定する。そして、欠陥画像である場合には、固体撮像素子の撮像面における当該注目画素の位置を示す位置情報を記憶する。一方、利用者により指定された露光時間での撮像を行う際には、当該位置情報の示す欠陥画素については、当該欠陥画素の原画素値と周辺画素の画素値の平均値とを露光時間に応じた比率(露光時間が短いほど前者の比率が高い)で重み付け平均した値に置き換えて画素値を補正する。

(もっと読む)

CMOSイメージセンサ及びその動作方法

【課題】自己較正により製造歩留まり率を改善可能なCMOSイメージセンサ及びその動作方法を提供する。

【解決手段】CMOSイメージセンサは画素配列ユニット、行選択ユニット及び論理回路を有する。画素配列ユニットはオブジェクトを検知するために用いられる。画素配列ユニットはM個の画素及びP個のマルチプレクサを有し、各画素は1つのマルチプレクサに電気的に接続されている。行選択ユニット及び論理回路はP個のマルチプレクサに電気的に接続されている。行選択ユニットは行選択信号を生成するために用いられる。論理回路は、オブジェクトに対応する検知領域を決定するために用いられる。検知領域はM個の画素のうちN個の画素を有する。更に、論理回路は、これらN個の画素に電気的に接続されているQ個のマルチプレクサを制御して行選択信号をN個の画素に送る。

(もっと読む)

バイナリ値変換回路およびその方法、AD変換装置、固体撮像素子、並びにカメラシステム

【課題】イメージセンサに集積しやすいよう小型で低消費電力であり、クロック位相情報をバイナリ値に変換し、かつデジタル加減算可能なバイナリ値変換回路およびその方法、AD変換装置、固体撮像素子、並びにカメラシステムを提供する。

【解決手段】状態に応じてレベルが反転する信号のレベルが反転した際に、少なくとも一つのクロック信号の位相情報をラッチするラッチ回路12と、ラッチ回路のラッチ位相情報を、パルス信号に応じてパルス列に変換する少なくとも一つの変換回路13と、変換回路の変換により得られたパルスをカウントクロックとして用いて、クロックの位相情報をバイナリコードに変換するリップルカウンタ部14と、を有する。

(もっと読む)

141 - 160 / 680

[ Back to top ]