Fターム[5C094DA15]の内容

要素組合せによる可変情報用表示装置 (81,180) | パネルの全体的構造 (7,880) | 積層 (4,364) | 膜の積層 (3,995) | 電極の被覆(間接的被覆を含む) (952) | 絶縁膜 (877)

Fターム[5C094DA15]に分類される特許

121 - 140 / 877

表示装置用基板及びそれを用いた液晶表示装置

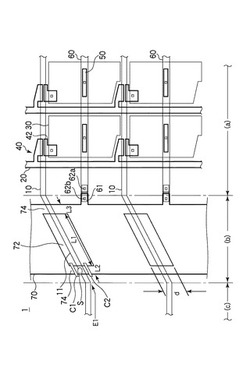

【課題】本発明は、静電気流入による層間短絡などの障害が生じたとしても容易に修復することのできる表示装置用基板を提供することを目的とする。

【解決手段】基板1上の表示領域内に配設され、表示領域の内方より表示領域の外方に向けて引き出し形成される第1の配線部10を有する。さらに、基板1上の表示領域の外の第1の配線部10と絶縁膜を介して交差して形成される第2の配線部70を有する。さらに、第2の配線部70に形成され、少なくとも交差する第1の配線部10と重なり合う領域に開口した開口部72を有する。さらに、開口部72の両端に形成され、絶縁膜を介して第1及び第2の配線部10、70が重なり合う重畳部74を有する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

グラフェンを利用した有機発光表示装置

【課題】グラフェンを利用した有機発光表示装置を提供する。

【解決手段】基板と、基板上に第1方向に形成された第1配線と、基板上に第2方向に形成された第2配線及び第3配線と、第1及び第2配線と連結されている第1薄膜トランジスタと、第1薄膜トランジスタ及び第3配線と連結されている第2薄膜トランジスタと、第2薄膜トランジスタと連結された有機発光素子と、を備え、第2配線及び第3配線は、グラフェンからなる有機発光表示装置である。

(もっと読む)

発光装置および電子機器

【課題】発光装置の各部に寄生する容量の影響を低減する。

【解決手段】単位素子Pは、第1電極21と第2電極22との間に発光層23が介在する発光素子Eと、発光素子Eに供給される電流量を制御する駆動トランジスタTdrと、駆動トランジスタTdrのゲート電極に電気的に接続された容量素子C1と、駆動トランジスタTdrのゲート電極の電位をデータ信号に応じて設定するための選択トランジスタTslと、駆動トランジスタTdrのゲート電極とドレイン電極との接続を制御するための初期化トランジスタTintとを含む。第1電極21は、容量素子C1と重なり合う一方、選択トランジスタTslや初期化トランジスタTintとは重なり合わない。

(もっと読む)

電気光学装置の製造方法および電気光学装置

【課題】誘電体層に高誘電率絶縁膜を用い、高誘電率絶縁膜等のエッチングにドライエッチングを採用した場合でも、静電破壊の発生を防止することができる電気光学装置の製造方法、および当該方法により製造した電気光学装置を提供すること。

【解決手段】液晶装置100を製造するにあたって、高誘電率絶縁膜形成工程および高誘電率絶縁膜パターニング工程によって誘電体層42aを所定領域に形成した後、第2電極形成用導電膜形成工程および第2電極形成用導電膜パターニング工程によって容量線5b(第2電極)を形成する。このため、高誘電率絶縁膜42は、広い領域にわたって形成された状態でドライエッチング時のプラズマを受けるのは、高誘電率絶縁膜パターニング工程の間だけであり、第2電極形成用導電膜パターニング工程を行う時点では、すでにパターニングされている。

(もっと読む)

薄膜トランジスタアレイパネル

【課題】薄膜トランジスタアレイパネルにおいて、酸化シリコン膜の厚さを減少させる。

【解決手段】本発明の実施形態に係る薄膜トランジスタアレイパネルは、絶縁基板と、絶縁基板上に配置され、ゲート電極を含むゲート線と、ゲート線上に配置され、窒化シリコンを含む第1ゲート絶縁膜と、第1ゲート絶縁膜上に配置され、酸化シリコンを含む第2ゲート絶縁膜と、第2ゲート絶縁膜上に配置される酸化物半導体と、酸化物半導体上に配置され、ソース電極を含むデータ線と、酸化物半導体上に配置され、ソース電極と対向するドレイン電極と、ドレイン電極と接続される画素電極と、を含み、第2ゲート絶縁膜の厚さは200Å以上500Å未満であることを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】鮮明な多階調カラー表示の可能なEL表示装置及びそれを具備する電気器具を提供する。

【解決手段】画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。また、時分割駆動方式を用いる際、データ信号側駆動回路102及びゲート信号側駆動回路103を、特異な結晶構造を有するシリコン膜を用いた極めて動作速度の速いTFTで形成する。

(もっと読む)

薄膜トランジスタおよび表示装置用電極基板の製造方法

【課題】ボトムコンタクト構造で、かつセルフアラインのTAOS TFTにおいて、TAOS層のソース領域およびドレイン領域に相当する領域を十分に低抵抗化できる製造方法、およびこのTAOS TFTを用いた表示装置用電極基板の製造方法を得る。

【解決手段】ゲート電極12、ソース電極14およびドレイン電極15上に、ゲート電極12を跨いでソース電極14とドレイン電極15とを繋ぐように第1、第2TAOS層16、17を形成するステップと、第1、第2TAOS層16、17上に、ゲート電極12をマスクとしたガラス基板11側からの露光により島状絶縁膜18を形成するステップと、ガラス基板11の全面に、島状絶縁膜18をマスクとして、島状絶縁膜18側からプラズマを照射するステップと、島状絶縁膜18の周囲に露出した第1、第2TAOS層16、17をアルカリ溶液に浸すステップとを備える。

(もっと読む)

半導体装置及びトランジスタの駆動方法

【課題】光照射されてトランジスタの電気特性が変動した場合でも、その電気特性をほぼ光照射前の状態にする手法を提供する。

【解決手段】酸化物半導体を用いたトランジスタのゲート電極に、正のバイアス電圧を10msec以上印加することにより、光照射されて変動した当該トランジスタの電気特性をほぼ光照射前の状態にすることが可能になる。なお、当該トランジスタのゲート電極に対する正のバイアス電圧印加は、当該トランジスタが受光する光量を参照して適切なタイミングで行う。これより光照射されても表示品位の低下が抑制された表示装置を実現することができる。

(もっと読む)

情報表示システム、情報表示器、駆動装置

【課題】薄型でコンパクトな駆動装置と、薄型の情報表示器を用いて情報を表示できる情報表示システムを提供する。

【解決手段】 情報表示器1Aは、第1基板11及び第2基板12の間において電界で駆動する表示媒体を備え、画素電極34が配置されたTFT基板31を備える駆動装置30を用いて第1基板11と画素電極34との間に形成させた電界によって、表示媒体が駆動されて情報表示画面領域に情報を表示するように構成されており、情報表示システムは、第1基板11側の外側に、弾性変形する弾性体層61が配置される。

(もっと読む)

半導体装置及びその作製方法

【課題】従来では、LDD構造を備えたTFTやGOLD構造を備えたTFTを形成しようとすると、その製造工程が複雑なものとなり工程数が増加してしまう問題があった。

【解決手段】第2のドーピング工程によって低濃度不純物領域24、25を形成した後、第4のエッチング工程を行うことによって、第3の電極18cに重なる低濃度不純物領域の幅と、第3の電極に重ならない低濃度不純物領域の幅とを自由に調節できる。こうして、第3の電極18cと重なっている領域は、電界集中の緩和が達成されてホットキャリアによる防止ができるとともに、第3の電極18cと重なっていない領域は、オフ電流値を抑えることができる。

(もっと読む)

発光装置

【課題】複雑な構造とすることなく、従来よりも密閉性に優れた空間に発光素子を備え、

かつ作業性に優れた封止技術を提供することにより、発光素子の劣化を防ぎ、信頼性の向

上を図ることを目的とする.

【解決手段】本発明では、密閉性に優れた封止構造を形成するために二重構造の封止を行

う。なお、この場合において、素子が形成される素子基板(以下、第1の基板ともいう)

と、封止に用いる封止基板(以下、第2の基板ともいう)にそれぞれサイズの異なる基板

を用いて、両基板が重ならない領域(以下、オフセット領域という)を設けることにより

、二重構造における外側のシールパターンを形成する場合における作業性を良くすること

を特徴とする。

(もっと読む)

半導体装置

【課題】薄膜トランジスタの電流駆動能力を増大するとともに負荷である配線容量を低減することが可能な半導体装置を提供する。

【解決手段】 絶縁基板と、前記絶縁基板上に形成されたゲート電極及び第1信号配線と、前記ゲート電極及び前記第1信号配線を覆う第1絶縁膜と、前記ゲート電極の直上の位置を含む前記第1絶縁膜上に形成された酸化物半導体層と、前記酸化物半導体層の一部を覆うとともにその領域を挟んだ両側で前記酸化物半導体層を露出し、且つ、前記第1信号配線の直上の位置を含む前記第1絶縁膜上に形成された第2絶縁膜と、前記第2絶縁膜から露出した前記酸化物半導体層にそれぞれ電気的に接続されたソース電極及びドレイン電極と、前記第2絶縁膜上に形成されるとともに前記第1信号配線と交差する第2信号配線と、を備えたことを特徴とする半導体装置。

(もっと読む)

表示装置

【課題】簡易な構成で配線間の静電破壊を防ぐこと。

【解決手段】表示装置は、絶縁基板と、前記絶縁基板の上に第1の信号線と第2の信号線とが形成された第1の導電層と、前記第1の導電層の上層に設けられた絶縁層と、前記絶縁層の上層に設けられ、前記第1の信号線および第2の信号線と平面的に重なる半導体膜が形成された半導体層と、を含む。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

電気光学装置、投射型表示装置、電気光学装置の製造方法

【課題】画素電極表面でのヒロックの発生や、平坦化絶縁膜において凹部を埋める部分での空洞の発生を防止することのできる電気光学装置、該電気光学装置を用いた投射型表示装置、および当該電気光学装置の製造方法を提供すること。

【課題手段】電気光学装置100の素子基板10において、反射性の画素電極9aの上層側に設けられた平坦化絶縁膜17は、画素電極9a上に積層された層がドープトシリコン酸化膜170からなる。ドープトシリコン酸化膜170の熱膨張係数は、画素電極9aを構成するアルミニウム膜の熱膨張係数との差が小さい。このため、加熱した状態で平坦化絶縁膜17を成膜しても、画素電極9aおよび平坦化絶縁膜17に大きな熱応力が発生しないので、画素電極9aの表面にヒロック等の欠陥が発生しにくい。また、ドープトシリコン酸化膜170は、段差被覆性に優れている。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造コストの削減が可能な薄膜トランジスタ回路基板及びその製造方法を提供する。

【解決手段】 チャネル領域、前記チャネル領域を挟んだ両側にソース領域及びドレイン領域を有する酸化物半導体薄膜と、前記酸化物半導体薄膜と同一材料によって形成され、第1低抵抗部及び第2低抵抗部を有する第1容量形成部と、前記酸化物半導体薄膜の前記チャネル領域上及び前記第1容量形成部の前記第1低抵抗部上に形成されるとともに、前記酸化物半導体薄膜の前記ソース領域及び前記ドレイン領域及び前記第1容量形成部の前記第2低抵抗部を露出するゲート絶縁膜と、を備え、前記酸化物半導体薄膜のうち、前記ソース領域と前記ドレイン領域との間の前記チャネル領域の長さL1は、前記第1容量形成部のうち、前記ゲート絶縁膜が積層された端部から前記第2低抵抗部に至るまでの長さL2よりも短い。

(もっと読む)

有機発光ディスプレイ装置及びその製造方法

【課題】有機発光ディスプレイ装置及びその製造方法を提供する。

【解決手段】基板上に配置され、屈折率の異なる複数の絶縁膜を含み、前記複数の絶縁膜のうち少なくとも一つは同一面上で異なる厚さで形成されたバッファ層と、前記バッファ層の厚い領域に形成された薄膜トランジスタの活性層と、前記バッファ層の薄い領域に形成された画素電極と、ゲート絶縁膜を介して前記活性層上に形成された前記薄膜トランジスタのゲート電極と、前記活性層に接続された前記薄膜トランジスタのソース及びドレイン電極と、前記画素電極上に形成された発光層と、前記発光層を介して、前記画素電極に対向配置される対向電極と、を備える有機発光ディスプレイ装置。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

121 - 140 / 877

[ Back to top ]