Fターム[5E082AB01]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | コンデンサの型式 (4,071) | 平板電極対向型(サンドイッチ型) (285)

Fターム[5E082AB01]に分類される特許

141 - 160 / 285

スタンドオフをもつ高精密キャパシター

キャパシターなどの電子コンポーネントである。第1主面および第2主面を有する基体と、基体の第1主面に積層した誘電体層と、第1電極と、そして第2電極とを有する。第1電極および第2電極にパシベーション層を積層する。第1電極上のパシベーション層に第1開口を形成し、第2電極上のパシベーション層に第2開口を形成する。第1開口内に第1ボトム電極成端部を設けるとともに、第2開口内に第2ボトム電極成端部を設ける。第1ボトム電極成端部を第1電極に電気的に接続するとともに、第2ボトム電極成端部を第2電極に電気的に接続する。第1ボトム電極成端部と第2ボトム電極成端部との間にスタンドオフを設け、パシベーション層に装着し、これによって実装時、電子コンポーネントの支持体とする。スタンドオフがあるため、素子は傾くことがなくなる。 (もっと読む)

電子部品とその製造方法

【課題】従来の誘電体膜を用いた電子部品は高温時に誘電体膜における樹脂が酸化分解しやすいなどの課題を有していた。

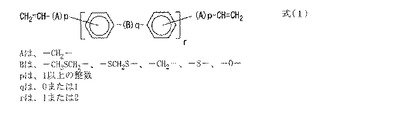

【解決手段】誘電体膜を備える電子部品であって、誘電体膜は、樹脂モノマーを重合反応させることによって形成された膜であり、樹脂モノマーが、ビニル基と芳香環とをアルキレン基を介して結合した一般式(1)で示されることを特徴とする電子部品とする。このことにより、上記化合物によれば、重合反応しやすく、特性が良好な電子部品が得られる。

【化1】 (もっと読む)

(もっと読む)

キャパシタおよび電子回路

【課題】キャパシタの極性による容量値の差を抑制することが可能なキャパシタおよび電子回路を提供すること

【解決手段】本発明は、基板(10)上に設けられた下部電極(12a、12b)と、下部電極(12a、12b)上に設けられた誘電体膜(14a、14b)と、誘電体膜(14a、14b)上に設けられた上部電極(16a、16b)とを有する2つのサブキャパシタ(20a、20b)と、2つのサブキャパシタ(20a、20b)のそれぞれの下部電極(12a、12b)は、それぞれ他方の上部電極(16b、16a)と相互に接続する2つの接続部(L1,L2)と、を具備するキャパシタおよび電子回路である。

(もっと読む)

多孔質導電性基板材料の被膜を誘電体で製造する方法及びこの方法を用いた高容量密度キャパシタの製造

本発明は、溶液の全質量における誘電体の部分として10質量%未満の濃度を持つ誘電体の前駆化合物の溶液を用いることにより、多孔質導電性基板材料の被膜を誘電体で製造する方法に関する。 (もっと読む)

薄膜コンデンサ

【課題】電気伝導度が高いアルミニウムまたは銅を用いて電極を厚く形成することで、ESRが低く、小型薄膜化可能な薄膜コンデンサを提供することを目的とする。

【解決手段】有機物からなる基板2と、基板2の上面に設けられた凹部と、基板2の凹部に形成されたアルミニウムからなる第一の金属端子8と、第一の金属端子8の上に形成された誘電体薄膜3と、誘電体薄膜3の上に形成されたアルミニウムからなる第二の金属端子9と、前記誘電体薄膜3と前記第二の金属端子9とを覆うように設けられた保護層4と、第一および第二の金属端子8、9の夫々とを接続するように保護層4に設けられた第一および第二の外部端子11、12とを有し、第一の金属端子8の表面を化学的機械研磨して基板2の表面を平滑化した構成を有している。

(もっと読む)

プリント回路基板内蔵型キャパシタの製造方法

【課題】プリント回路基板内蔵型キャパシタの製造方法を提供する。

【解決手段】補強基材及びその両面に積層された銅箔からなるCCL基板を用意するステップと、前記CCL基板の銅箔表面を平坦化するステップと、前記平坦化された銅箔表面上に誘電層を形成するステップと、前記誘電層上に上部電極を形成するステップとを含む。

(もっと読む)

ゾル−ゲル法による強誘電体膜の形成方法及びキャパシタの製造方法

【課題】ゾルーゲル法において、強誘電体膜の結晶配向性を制御し、優れた電気的特性を示し、クラックがなく、厚膜化が容易な強誘電体膜を提供する。

【解決手段】強誘電体膜の構成金属元素の有機金属化合物とアルカノールアミン及びβ−ジケトンの一方又は双方を含有する安定剤と溶剤とを含む原料溶液をシリコン基板上に塗布し、上記塗布された原料溶液を上記溶剤の沸点よりも高く上記安定剤の沸点よりも低い温度で乾燥させて乾燥ゲル膜を形成し、上記乾燥ゲル膜を焼結してペロブスカイト結晶を含む1000Å以下の膜厚の強誘電体膜を形成する。

(もっと読む)

薄膜デバイス

【課題】薄膜デバイスにおける導体層と端子電極との接続信頼性を高めると共に、薄膜デバイスの小型化、低背化を図る。

【解決手段】薄膜デバイス1は、デバイス本体1Bと4つの端子電極とを備えている。デバイス本体1Bは4つの側面を有し、各端子電極は各側面の一部に接触するように配置されている。デバイス本体1Bは、第1の受動素子を構成するために用いられる下部導体層43と、第2の受動素子を構成するために用いられる上部導体層73とを含んでいる。デバイス本体1Bの側面1eにおいて、下部導体層43の端面43E1と上部導体層73の端面73E1は、電気的且つ物理的に接続されている。端子電極13は下部導体層43の端面43E1および上部導体層73の端面73E1に接触して、導体層43,73に接続されている。

(もっと読む)

コンデンサ用電極及びそれを用いた電気二重層コンデンサ

【課題】炭素系の多孔質材料を含まない新規なコンデンサ用電極及び、それを用いた電気二重層コンデンサを提供する。

【解決手段】誘電体5と、誘電体を介して設けられる1対の電極10a、10bとを具備する電気二重層コンデンサ1において、それらの電極は電界効果を有する半導体からなるコンデンサ用電極であり、電極10aは、誘電体と接する面と対向する面に設けられた導電体20aを介して直流電源50の一方の極に接続され、電極10bは、誘電体と接する面と対向する面に設けられた導電体20bを介して直流電源の他方の極に接続される。

(もっと読む)

成膜方法

【課題】 密着性の高い膜を金属箔上に形成する。

【解決手段】 金属箔10の表面10a上に、その表面を部分的に露出させながら複数の島状構造12を形成する。次に、これらの島状構造を覆うように膜20を形成する。これらの島状構造は金属箔の表面上に凹凸を形成する。島状構造を覆うように膜20を形成すると、島状構造からなる凹凸と膜とが噛み合う。この結果、金属箔に対する膜の密着性が高まる。

(もっと読む)

薄膜キャパシタ素子、インターポーザ、半導体装置、及び、薄膜キャパシタ素子或いはインターポーザの製造方法

【課題】

薄膜キャパシタに絶縁破壊等の問題が生じた場合であっても、接続されている他のデバイス等に悪影響を及ぼすことのない、信頼性の高い薄膜キャパシタ素子、インターポーザ、半導体素子、及び、これらの製造方法を提供する。

【解決手段】

本発明の薄膜キャパシタ素子10は、誘電体層13とそれを挟む2つの電極12,14を有する薄膜キャパシタ15と、前記電極と電気的に接続される外部端子23とを備え、前記電極と外部端子との間に設けられ、前記電極に隣接するとともに、前記隣接する電極よりも大きな抵抗率を有する材料からなる抵抗層30を有する。

(もっと読む)

薄膜電子部品の製造方法

【課題】短絡の発生が十分に防止された薄膜電子部品を得ることが可能な薄膜電子部品の製造方法を提供すること。

【解決手段】基板10の第1の主面10a側に電極層31,32を有する薄膜電子素子40を形成する薄膜電子素子形成工程と、第2の主面10b側に前記薄膜電子素子40と対応するアライメントマーク70を形成するアライメントマーク形成工程と、基板10及び電極層31,32を貫通する貫通孔52、53を第2の主面10b側からの穿孔により形成する貫通孔形成工程等を備え、貫通孔形成工程よりも前に、第2の主面10bを研磨する研磨工程を備える、薄膜電子部品100の製造方法。

(もっと読む)

ディカップリング機能を有する多層基板

【課題】低周波及び高周波帯域で優れたディカップリング特性を発揮するディカップリング機能を有する多層基板を提供する。

【解決手段】多層基板上面にはパワー/接地端子部に連結されるIC部品200実装の基板本体100と、パワー誘電層に形成されパワー端子部T10,T11,T12とIC部品200に連結されるパワーライン部L10と、接地誘電層に形成され接地端子部とIC部品200に連結される接地ライン部L20と、基板本体100上面に実装され基板本体100上面のパワー端子部T10,T11,T12と接地端子部T20,T21,T22との間に連結される積層型チップキャパシタと、基板本体100の内部に内蔵されパワーライン部L10と接地ライン部L20との間に連結される薄膜キャパシタを備える。

(もっと読む)

複合電子部品

【課題】 十分な耐衝撃性を確保した複合電子部品を提供する。

【解決手段】 このレゾネータ1では、板状の保持部72,82が含む受け部73,83により圧電素子2が支持され、保持部72,82が含む片部74a,84aが容量素子3と接触させられている。これにより、圧電素子2と容量素子3との間隔が一定に保たれることになる。更に、レゾネータ1が衝撃を受けても板状の保持部72,82により衝撃が吸収されることになる。従って、レゾネータ1の耐衝撃性を向上させることができる。

(もっと読む)

複合電子部品

【課題】 十分な耐衝撃性を確保した複合電子部品を提供する。

【解決手段】 このレゾネータ1では、容量素子3は、容量素子3において振動領域2aと重なる部分から、圧電素子2より外側に突出する突出部37を有している。突出部37は容量素子3の長手方向と略直交する方向において容量素子3の両側に設けられている。これにより、容量素子3の突出部37がモールド樹脂5に食い込むため、圧電素子2の振動領域2aを内包する振動空間5aがモールド樹脂5に設けられていても、モールド樹脂5に対して容量素子3が十分に固定されることになる。従って、レゾネータ1の耐衝撃性を向上させることができる。

(もっと読む)

薄膜デバイス

【課題】薄膜デバイスにおける導体層と端子電極との接続信頼性を高めると共に、端子電極の形状や位置のばらつきを抑制する。

【解決手段】薄膜デバイス1は、基板と、この基板の上に順に積層された絶縁層、下部導体層、誘電体膜、絶縁層、上部導体層および保護膜8と、端子電極11〜14を備えている。端子電極11〜14は、上部導体層の端面の一部と、この端面に続く上部導体層の上面の一部とに接触している。保護膜8は、その外縁から内側に凹んだ形状をなして上部導体層の上面のうち端子電極11〜14に接触する部分を露出させる凹部81〜84を有している。凹部81〜84は端子電極11〜14の一部を収容している。

(もっと読む)

セラミック電子部品及びその製造方法

【課題】実装基板の電極素子への電気的接続を確実に行うこと及び長寿命化を実現可能とするセラミック電子部品を製造できるセラミック電子部品の製造方法等を提供すること。

【解決手段】 本発明は、セラミック電子部品本体11のバンプ電極形成面10aに複数のバンプ電極を形成してセラミック電子部品10を製造する方法において、セラミック電子部品本体11のバンプ電極形成面10aに、Cuを含む金属ペースト26を印刷により複数箇所に塗布し、複数箇所に塗布した金属ペースト26上に、金属ペースト26の焼付け温度よりも高い融点を有するCuで構成される均一寸法の金属ボール22を搭載し、金属ペースト26を、金属ボール22を構成するCuの融点よりも低い温度で焼付け処理し、バンプ電極を得る方法である。

(もっと読む)

電気回路装置

【課題】相対的に低いインピーダンスを有し、温度上昇を抑制可能な電気回路装置を提供する。

【解決手段】電気回路装置200は、電気素子100と、導体板210,220とを備える。電気素子100は、陽極電極10A,10Bと、陰極電極20E,20Fとを有し、1×10−5〜10GHzの周波数領域において相対的に低いインピーダンスを有する。導体板210は、電気素子100を構成する導体板の抵抗よりも低い抵抗を有し、陽極電極10A,10B間に接続される。導体板220は、電気素子100を構成する導体板の抵抗よりも低い抵抗を有し、陰極電極20E,20F間に接続される。

(もっと読む)

コンデンサ

【課題】下部共通電極による寄生抵抗が小さいコンデンサを提供すること。

【解決手段】下部共通電極と、該下部共通電極上に積層された誘電体層および上部電極層から成る複数個の容量形成部とを備えたコンデンサであって、前記上部電極層は、第1上部電極層と、該第1上部電極層と電気的に絶縁されるとともに隣接して配置された第2上部電極層とを含み、前記第1上部電極層および前記第2上部電極層は、対向した辺同士が互いに噛み合う形状を有することから、下部共通電極内を通る電流の経路の幅が広くなるので、寄生抵抗を低減させたコンデンサとなる。

(もっと読む)

誘電体素子とその製造方法

【課題】導電体と誘電体との密着性に優れた誘電体素子を提供する。

【解決手段】誘電体素子10は、第1の導電体12と、その上に設けられた誘電体14を有している。第1の導電体と誘電体との間には中間領域16が形成されている。中間領域では、第1の導電体および誘電体のいずれとも異なる添加物が誘電体と混在している。この添加物は、Si、Al、P、Mg、Mn、Y、V、Mo、Co、Nb、FeおよびCrのうち一つ以上の元素を含んでいる。

(もっと読む)

141 - 160 / 285

[ Back to top ]