Fターム[5E082BC30]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 目的、効果 (2,673) | 損失(tanδ)の改善 (81)

Fターム[5E082BC30]に分類される特許

1 - 20 / 81

フィルムコンデンサ用のフィルムおよびフィルムコンデンサ

積層セラミック電子部品及びその製造方法

【課題】一定水準のESRを具現しながら、同一容量の積層セラミック電子部品におけるQ値の選択幅を広げる。

【解決手段】複数の誘電体層111が積層されたセラミック素体110と、セラミック素体110の内部に形成された第1及び第2内部電極131、132とを含み、第1及び第2内部電極131、132は、銅が80から99.9wt%、及び、ニッケルが0.1から20wt%を含み、周波数が1000MHz以下である積層セラミック電子部品を形成する。

(もっと読む)

4端子型セラミックコンデンサ

【課題】 実装面積をより小さくすることができ、かつ、耐振動性を向上させることが可能な4端子型セラミックコンデンサを提供する。

【解決手段】 4端子型セラミックコンデンサ1は、直方体状のセラミックコンデンサ部10と、対向する側面10a,10bに形成された一対の電極20,21と、一対の電極20,21それぞれに接続されたヘアピン状のリード線30,31とを備える。リード線30(31)は、側面10a(10b)の長手方向に伸びる一対の直線部30a,30b(31a,31b)と、該一対の直線部30a,30b(31a,31b)の端部同士を滑らかに接続する湾曲部30c(31c)とを含む。一方の直線部30a(31a)は電極20(21)に接続され、他方の直線部30b(31b)は電極20(21)と離間して設けられ、湾曲部30c(31c)は、平面視した場合に、側面10a(10b)に対して垂直な方向に伸びる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、上記セラミック素体の内部に形成され、上記セラミック素体の第1面及び上記第1面と連結された第3面または第4面に露出し、上記第1面に露出した領域のうち一部が互いに重なる引出し部を有する第1及び第2内部電極と、上記セラミック素体の第1面及び上記第1面から延長されて上記第1面と連結された第3面または第4面に形成され、上記引出し部と夫々連結される第1及び第2外部電極と、上記セラミック素体の第1面、上記第1面と連結された第3面及び第4面に形成される絶縁層と、を含む。

(もっと読む)

セパレーター、セパレーター製造装置及びセパレーター製造方法

【課題】セパレーターの通液性が低下するのを抑制することが可能であり、従来のセパレーターよりも、一層高い電解液吸収性や一層低いイオン抵抗を実現することが可能なセパレーターを提供する。また、上記のようなセパレーターを製造することが可能なセパレーター製造装置を提供する。さらにまた、上記のようなセパレーターを製造することが可能なセパレーター製造方法を提供する。

【解決手段】基材層10と、基材層10との接合に用いられる接合ナノ繊維22を少なくとも含むナノ繊維層20とを有し、基材層10とナノ繊維層20とは、接合ナノ繊維22により接合されているセパレーター1。

(もっと読む)

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

金属化フィルムとその製造方法

【課題】誘電体フィルムの表面に蒸着された蒸着膜中の粒界面積の減少と格子欠陥の修復を図り、電気抵抗率の小さな金属化フィルムコンデンサの内部電極を構成する金属化フィルムとその製造方法を提供する。

【解決手段】金属化フィルムコンデンサ10を構成する誘電体フィルム1と該誘電体フィルム1の表面に配された内部電極層2とからなる金属化フィルム4の製造方法であって、誘電体フィルム1の表面に金属を蒸着させ(蒸着金属2”)て金属蒸着膜2’とし、冷間加工にて金属蒸着膜2’の結晶内に加工歪を導入し、誘電体フィルム1と加工歪を導入した金属蒸着膜2’からなる中間体3を製造する第1のステップ、中間体3を熱処理し、金属蒸着膜2’の少なくとも一部を再結晶化して内部電極層2とし、誘電体フィルム1と内部電極層2とからなる金属化フィルム4を製造する第2のステップからなる。

(もっと読む)

貫通型積層コンデンサ

【課題】コンデンサ素体と接地用端子電極との密着性を向上させることができる貫通型積層コンデンサを提供すること。

【解決手段】貫通型積層コンデンサC1は、誘電体層10が積層されたコンデンサ素体L1と、接地用内部電極20と、接地用内部電極20よりも積層数が多い信号用内部電極31,32と、接地用内部電極20に接続される接地用端子電極3,4と、信号用内部電極31,32に接続される信号用端子電極1,2と、引き出し電極部20b,20cの幅Aよりも狭い幅B1,B2で接地用端子電極3,4に接続されるダミー電極36〜39とを備えている。ダミー電極36〜39は、誘電体層10の積層方向から見た際に積層方向に隣接するダミー電極36〜39同士が接地用内部電極20の引き出し電極部20b,20cに重なる領域内において互いに重ならないように配置される。

(もっと読む)

セラミックス組成物及び電子部品

【課題】低温焼成が可能で、高周波領域での誘電損失が低く、メッキ耐食性に優れた焼結体を得ることが可能なセラミックス組成物及び電子部品を提供する。

【解決手段】Ba4(Re(1−x),Bix)9.33Ti18O54で現わされる主相成分と、主相成分100質量部に対し酸化物換算で、B成分を0.3〜1.4質量部、Li成分を0.1〜0.3質量部、Zn成分を1.5〜7質量部及びAg成分を1.5〜2質量部含有する第1副成分と、主相成分100質量部に対し酸化物換算で、Si成分を0〜1.25質量部、Al成分を0〜1.25質量部、Bi成分を0〜5質量部含有する第2副成分とを含むセラミックス組成物。該セラミックス組成物を焼成して得られるセラミックス層と、該セラミックス層の表面及び/又は内部にあって、セラミックス組成物と同時焼成して得られる導体層とを有する電子部品。

(もっと読む)

誘電体、及びキャパシタ型蓄電池

【課題】比誘電率が高い誘電体、並びに、それを利用した、静電容量が大きいキャパシタ型蓄電池を提供する。

【解決手段】架橋構造を有する樹脂と、金属塩構造を持つ分子鎖を有する化合物である金属イオンと、を含んで構成される誘電体10、及びそれを利用したキャパシタ型蓄電池である。架橋構造を有する樹脂はメタアクリル樹脂であり、重量平均分子量1000当たり少なくとも1個の架橋性基を有し、該架橋性基の少なくとも一部は架橋反応により架橋構造となる。

(もっと読む)

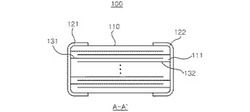

デカップリングデバイス

【課題】製造コストが小さく且つ温度変化による特性変動が小さいデカップリングデバイスを提供する。

【解決手段】デカップリングデバイス100は、複数の第1内部導体層111と複数の第2内部導体層112又は複数の第3内部導体層113とを交互に繰り返し積層してなる積層体110と、積層体110の外面に形成され第1内部導体層111と接続する第1外部電極121と、積層体110の外面に形成され第3内部導体層113と接続する第2外部電極122と、積層体110の外面に形成され第2内部導体層112と第3内部導体層113とを接続するとともに所定の抵抗値R11を有する抵抗性電極130とを備えた。

(もっと読む)

キャパシタ型蓄電池、キャパシタ型蓄電池用蓄電層

【課題】静電容量が高く、強度に優れた薄膜キャパシタ型蓄電池を提供する。

【解決手段】第1の実施形態に係るキャパシタ型蓄電池には、導電性又は半導電性の第1粒子12Aが有機高分子中に埋め込まれた第1複合層12と、第1導電膜又は第1半導体膜からなる第1基材13と、が積層された第1積層基材11を設ける。第1積層基材11の第1基材13上には第1絶縁層21が設け、第1積層基材の第1複合層12の第1複合層12上には第2絶縁層22が設ける。第1絶縁層21上には、第1積層基材11の長尺方向(図1では紙面の手前から奥に向かう方向)に延在する第1導電路31が設け、第2絶縁層22上には、第1積層基材の長尺方向に延在し、第1導電路31と平行するように第2導電路32が設ける。

(もっと読む)

積層セラミックコンデンサ

【課題】 高誘電率かつ誘電損失が小さく、比誘電率の温度変化がEIA規格のX5R特性を満足し高温負荷試験での寿命特性に優れる積層セラミックコンデンサを提供する。

【解決手段】 誘電体磁器が、マグネシウム、マンガン、希土類元素(RE)を含み、チタン酸バリウムを主体とし、前記希土類元素の濃度が0.15原子%以下の結晶粒子からなる第1の結晶群と、前記チタン酸バリウムを主体とし、前記希土類元素の濃度が0.2原子%以上の結晶粒子からなる第2の結晶群とを有し、前記誘電体磁器の研磨面に見られる前記第1の結晶群を構成する結晶粒子の面積をa、前記第2の結晶群を構成する結晶粒子の面積をbとしたときに、b/(a+b)が0.4〜0.7であるとともに、前記第1の結晶群を構成する結晶粒子および前記第2の結晶群を構成する結晶粒子の平均粒径が0.15〜0.40μmである。

(もっと読む)

積層セラミックコンデンサ

【課題】 高誘電率かつ誘電損失が小さく、比誘電率の温度変化がEIA規格のX5R特性を満足し高温負荷試験での寿命特性に優れる積層セラミックコンデンサを提供する。

【解決手段】 誘電体磁器が、マグネシウム、マンガン、希土類元素(RE)を含み、チタン酸バリウムを主体とし、前記マグネシウムの濃度が0.2原子%以下の結晶粒子からなる第1の結晶群と、前記チタン酸バリウムを主体とし、前記マグネシウムの濃度が0.3原子%以上の結晶粒子からなる第2の結晶群とを有し、前記誘電体磁器の研磨面に見られる前記第1の結晶群を構成する結晶粒子の面積をa、前記第2の結晶群を構成する結晶粒子の面積をbとしたときに、b/(a+b)が0.4〜0.7であるとともに、前記第1の結晶群を構成する結晶粒子および前記第2の結晶群を構成する結晶粒子の平均粒径が0.15〜0.40μmである。

(もっと読む)

フィルムコンデンサ

【課題】上下端面にメタリコン電極を設けた二個のコンデンサ素子を縦に並べて、上端面に開口部のある有底筒状のケースに収容し、ケースの開口部に外部電極端子を設けるフィルムコンデンサにあって、コンデンサ素子を電気的に並列に接続すると、並列共振により、並列共振点でのインピーダンスと等価直列抵抗が高くなりやすいとともに、コンデンサ内部の並列回路内に循環電流が流れ、そのために異常発熱するという問題が発生しやすい。本発明は、並列コンデンサの共振点のインピーダンスの増加を低減することを目的としている。

【解決手段】コンデンサ素子同士を並列に接続するのに、コンデンサ素子間の向かい合った各メタリコン電極はそれぞれ別々に引き出し電極と接続されているので、並列コンデンサの共振点のインピーダンスの増加を十分低減することができる。

(もっと読む)

積層コンデンサ

【課題】ESRの向上を図ると共に、積層体内の発熱を抑制することのできる積層コンデンサを提供する。

【解決手段】内部電極41,42,50,51を静電容量部として機能させると共に内部電極40,52をESR制御部として機能させ、ESRを向上させる。接続導体11,21と端子電極10,20との界面に高抵抗層13,23が形成されることによって、各内部電極による抵抗成分R1と、高抵抗層13,23による抵抗成分R2によって、並列等価回路が形成されている。これによって、各内部電極に流れる電流の一部を高抵抗層13,23に流すことができるため、積層体内での発熱を抑制することが可能となる。

(もっと読む)

積層セラミックコンデンサ

【課題】高い静電容量を有するとともに、優れた高温負荷寿命を有し、かつ誘電損失の低い積層セラミックコンデンサを提供する。

【解決手段】複数の誘電体層5と複数の内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面に設けられた外部電極3とを有する積層セラミックコンデンサであって、前記誘電体層5がチタン酸バリウムを主結晶粒子として含有する誘電体磁器からなり、前記誘電体層5が、隣接する前記内部電極層7間において、粒径の大きい主結晶粒子を含む領域と粒径の小さい主結晶粒子を含む領域とを有している。

(もっと読む)

コンデンサ素子を含むデバイス

【課題】複数のコンデンサ素子を含むデバイスであって、大容量、低ESRおよび低ESLのデバイスを提供する。

【解決手段】デバイス1は、第1のコンデンサ素子21と、リードフレーム10と、リードフレーム10を挟むように積層された第2のコンデンサ素子22とを有する。リードフレーム10は、第1のコンデンサ素子21の陽極31と第1のボンディングワイヤ41を介して電気的に接続された陽極リード部11と、第1のコンデンサ素子21の陰極32に電気的に接続された陰極リード15および16とを含む。陽極リード11は、長手方向Xに対して直交する横方向Yに沿って第1のコンデンサ素子21から外側に向かって延びた電気的接続に供する部分11bを含み、第1のコンデンサ素子21から外側に向かって延びた電気的接続に供する部分を含まない。

(もっと読む)

積層コンデンサの実装構造

【課題】共振周波数におけるインピーダンスの急激な低下を抑えることができ、かつクラックの発生を抑制できる積層コンデンサの実装構造を提供する。

【解決手段】積層コンデンサ2の実装構造1では、樹脂電極層14が第2コンデンサ部12のESR成分として機能するようなフィレット高さHのハンダフィレット7によって積層コンデンサ2と回路基板6との接続がなされている。これにより、樹脂電極層14の厚みに応じたESR成分が第2コンデンサ部12に付与され、共振周波数におけるインピーダンスのフラット化を実現できる。また、積層コンデンサ2の実装構造1では、第1コンデンサ部11と第2コンデンサ部12との間に間隔Dが設けられている。これにより、回路基板6の変形応力や第1コンデンサ部11の電歪振動による応力が第2コンデンサ部12に伝達しにくくなり、クラックの発生を抑制できる。

(もっと読む)

コンデンサ

【課題】コンデンサの幅を抑えながらも外部接続用端子間に十分な絶縁距離を確保できるとともに、低インダクタンス化にも寄与するコンデンサを提供する。

【解決手段】本発明のコンデンサは、両端面に電極部10a、10aを有するコンデンサ素子10と、一方がコンデンサ素子10の一方の電極部10aに接続され、他方がコンデンサ素子10の他方の電極部10aに接続される一対の電極板20、30とを備えたコンデンサであって、一対の電極板20、30は、主電極部21、31と、主電極部21、31から角度をもって延設された副電極部22、32とをそれぞれ有し、副電極部22、32の相対する端部から外部接続用端子23、33を相対向させて延設している。

(もっと読む)

1 - 20 / 81

[ Back to top ]