Fターム[5E082BC40]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 目的、効果 (2,673) | その他の目的、効果 (460)

Fターム[5E082BC40]に分類される特許

1 - 20 / 460

積層セラミックコンデンサ及びその製造方法

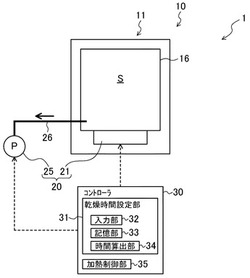

コンデンサ素子の乾燥方法およびコンデンサ素子の乾燥装置

【課題】コンデンサ素子の乾燥に要するエネルギーを削減する。

【解決手段】コンデンサ素子(43)の乾燥方法では、フィルム(44)を巻回してコンデンサ素子(43)を形成する素子形成工程と、素子形成工程で吸湿したコンデンサ素子(43)を100℃で加熱して乾燥させるための乾燥時間を設定する乾燥時間設定工程と、乾燥時間設定工程で設定された乾燥時間の間、100℃でコンデンサ素子(43)を加熱して乾燥する乾燥工程とを備えている。

(もっと読む)

積層セラミックコンデンサ

【課題】積層セラミックコンデンサの、基板上への実装状態での電界印加時における「鳴き」を抑制する。

【解決手段】コンデンサ本体29における内部電極27,28の対向による静電容量形成に寄与する活性部37を、積層方向に沿って分布する第1領域40と基板22側の第2領域41とに区分し、第2領域41における誘電体セラミック層25の誘電率を、第1領域40における誘電体セラミック層24の誘電率より低くし、かつ第2領域41における誘電体セラミック層25の体積に対する内部電極27,28の体積の比率を、第1領域40における誘電体セラミック層24の体積に対する内部電極27,28の体積の比率より高くする。

(もっと読む)

電子部品

【課題】回路設計において高い自由度を得つつ、鳴きを低減することができる電子部品を得る。

【解決手段】互いに対向する底面S2及び上面S1、並びに、互いに対向する第1の端面S3及び第2の端面S4を有する直方体状の積層体11と、誘電体層と共に積層されることによってコンデンサを形成し、かつ、第1の端面S3又は第2の端面S4に引き出されている複数のコンデンサ導体30a〜30d,32a〜32dと、第1の端面S3及び底面S2に跨って設けられ、かつ、コンデンサ導体32a〜32dと接続されている第1の外部電極12aと、第2の端面S4及び底面S2に跨って設けられ、かつ、コンデンサ導体30a〜30dと接続されている第2の外部電極12bと、を備える電子部品。底面S2と該底面S2に最も近いコンデンサ導体32dとの間の距離H5は、上面S1と該上面S1に最も近いコンデンサ導体30aとの間の距離よりも大きい。

(もっと読む)

静電容量素子、及び共振回路

【課題】静電容量素子において、焼成時に発生する残留応力を利用することで誘電率を向上させ、静電容量を増大する。

【解決手段】容量素子(可変容量素子1)は、誘電体層と、誘電体層を挟んで形成される少なくとも一対の内部電極10とを備える容量素子本体2と、容量素子本体2の側面に形成され、内部電極10に電気的に接続される外部端子3,4とを備える。そして、誘電体層5及び内部電極の線膨張係数の違いに起因して発生する応力が、誘電体層5と誘電体層5を挟む一対の内部電極10とで構成されるコンデンサCの中心に集中するように構成されている。

(もっと読む)

複合電子部品及び複合電子部品の実装構造

【課題】複数の電子部品を含む複合電子部品の信頼性を向上させること。

【解決手段】複合電子部品1は、電子部品2と、導体層3と、支持体4とを含む。電子部品2は、素体10の対向する表面のそれぞれに、第1端子電極11と第2端子電極12とを有する。導体層3は、複数の電子部品2が有する第1端子電極11を電気的に接続する。支持体4は、導体層3が設けられる。複数の電子部品2が有する第2端子電極12は、回路基板の端子に接続されるための実装端子電極となる。

(もっと読む)

蓄電素子、取付ボルト

【課題】電極端子に通電部材を取り付ける際に取付ボルトに強いトルクが発生しても抗することのできる蓄電素子の提供。

【解決手段】筐体120と、筐体120の外側に取り付けられる電極端子105と、導電性を有する通電部材200を電極端子105に取り付ける取付ボルト108と、取付ボルト108と筐体120とを絶縁する絶縁部材109とを備える蓄電素子であって、取付ボルト108は、外周部にねじ山が設けられる棒状のねじ部181と、ねじ部181の一端部から放射方向に張り出すフランジ状の部材であって、ねじ部181に螺合するナット201の回転方向と直交する、または、略直交する面に沿って配置される第一当接面部183を有する抗回転部182とを備え、絶縁部材109は、抗回転部182を収容し、第一当接面部183と当接する第二当接面部192を有する凹陥部191を備える。

(もっと読む)

金属粉末、導電性ペースト及び積層セラミックコンデンサ

【課題】平均粒径が小さくかつ粒径の分布が狭い金属粉末であって、構成する各金属粒子の表面の平滑性が優れた金属粉末を提供することを目的とする。

【解決手段】金属粉末は、走査型電子顕微鏡(以下、SEMと記載する。)による測定に基づいて算出された平均粒径をD50SEMとし、BET法により算出された平均粒径をD50BETとするとき、以下の式(1)および式(2)をともに満たす金属粉末。D50SEM≦200nm…(1),D50SEM/D50BET≦2…(2)

(もっと読む)

積層型コンデンサ及びその製造方法

【課題】単位体積あたりの静電容量を増大させると共に製造効率を向上させることが可能な積層型コンデンサ及びその製造方法を提供する。

【解決手段】積層型コンデンサは、第1電極部1、第2電極部2、及び誘電体層を備えている。第1電極部1は、第1帯部11と、該第1帯部の側縁から延びた複数の第1平板部12とを有している。第2電極部2は、第2帯部21と、該第2帯部の側縁から延びた複数の第2平板部22とを有している。第1電極部1及び第2電極部2は、第1平板部12及び第2平板部22が積層された状態で配置されている。第1平板部12は、第2平板部22と第2帯部21とに対向し、第2平板部22は、第1平板部12と第1帯部11とに対向している。誘電体層は、互いに隣り合う第1平板部12と第2平板部22との間に介在すると共に、第1平板部12と第2帯部21との間、並びに第2平板部22と第1帯部11との間に介在している。

(もっと読む)

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

誘電体磁器組成物およびセラミック電子部品

【課題】 誘電体層を薄層化した場合であっても、良好な特性を示す誘電体磁器組成物および電子部品を提供すること。

【解決手段】ペロブスカイト型化合物(ABO3)を含有し、化合物100モルに対して、各酸化物換算で、RA2O3(RAはDy、GdおよびTbから選ばれる1つ以上)を0.6〜2.5モル、RB2O3(RBはHoおよび/またはY)を0.2〜1.0モル、RC2O3(RCはYbおよび/またはLu)を0.1〜1.0モル含有し、Mg酸化物を、Mg換算で0.8〜2.0モル、Si化合物をSi換算で1.2〜3.0モル含有し、RA2O3の含有量(α)、RB2O3の含有量(β)およびRC2O3の含有量(γ)が、1.2≦α/β≦5.0、0.5≦β/γ≦10.0である誘電体磁器組成物。該誘電体磁器組成物は、誘電体層厚みが5.0μm以下の電子部品に適用することが好ましい。

(もっと読む)

積層貫通コンデンサ

【課題】高周波帯域でのノイズの除去能力を向上した積層貫通コンデンサを提供すること。

【解決手段】積層貫通コンデンサ1は、誘電体層5を積層してなるコンデンサ素体2と、主電極部10a及び引き出し電極部10b,10cを有する信号用内部電極10と、主電極部10aと対向する主電極部20a及び引き出し電極部20b,20cを有する接地用内部電極20と、信号用内部電極10に接続される信号用端子電極3,3と、接地用内部電極20に接続される接地用端子電極4,4とを備えている。積層貫通コンデンサ1では、信号用内部電極10の主電極部10aが、積層方向に対向する接地用内部電極20の主電極部20aに向かって屈曲しており、また、接地用内部電極20の主電極部20aが、信号用内部電極10の主電極部10aと同じ方向に屈曲している。

(もっと読む)

積層セラミック電子部品の内部電極用導電性ペースト及びこれを利用した積層セラミック電子部品

【課題】本発明は積層セラミック電子部品の内部電極用導電性ペースト及びこれを利用した積層セラミック電子部品に関する。

【解決手段】内部電極用導電性ペーストに窒化シリコーン、窒化ホウ素、窒化アルミニウム及び窒化バナジウムからなる群から選択される1つ以上の窒化物を添加して内部電極の収縮開始温度を上昇させることで、上記内部電極用導電性ペーストを利用した積層セラミック電子部品の信頼性を向上させることができる。

(もっと読む)

積層型コンデンサ

【課題】材料的な制約を受けることなく且つ汎用的な構造を含む場合にも適用可能であって、電歪振動を抑制することが可能な積層型コンデンサを提供すること。

【解決手段】誘電体セラミックスによって形成された素体及びその素体内部においてセラミックス層を挟んで重なりあうように配置された複数の内部電極4a,4bを有する積層体2と、を備え、複数の内部電極4a,4bを含むコンデンサ領域CAと、複数の内部電極4a,4bによって生じる電歪現象を低減させ音鳴きを抑制するための第一抑制領域EA及び第二抑制領域DAとが形成されており、第一抑制領域EAはコンデンサ領域CAに隣接し、第二抑制領域DAの厚みは複数の内部電極4a,4bの配置態様に応じて定められるものである。

(もっと読む)

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

積層型電子部品の製造方法

【課題】特性のばらつきが少なく、小型で高容量の電子部品を、低コストで製造することが可能な積層型電子部品の製造方法を提供すること。

【解決手段】グリーンシートに所定パターンで電極ペースト膜を形成する工程と、グリーンシートを積層して積層体4aを準備する工程と、積層体を、支持基板36の粘着層34に付着する工程と、積層方向と直交する第1方向に沿って、支持基板は切断せずに積層体を切断して端子電極接続面15a,15bを形成し、積層方向および第1方向と直交する第2方向に沿って、積層体および支持基板を切断してギャップ面16を形成し、支持基板と一体化された棒状体38を得る工程と、ギャップ面が同一平面に配置されるように複数の棒状体38を並べ、ギャップ面16に、セラミックペースト42を塗布する工程と、粘着層の粘着力を弱め、積層体2aと支持基板36とを分離する工程とを有することを特徴とする。

(もっと読む)

コンデンサおよび回路基板

【課題】 放電現象の発生を抑制でき、耐電圧が高く、かつ高い静電容量を有するコンデンサと、それを搭載した回路基板を提供する。

【解決手段】 誘電体層5と内部電極層7とが交互に積層され静電容量の発現に寄与する容量部1bと該容量部1bを前記誘電体層5および前記内部電極層7の積層方向から挟むように設けられている一対のカバー部1c、1dとを有するコンデンサ素体1とを具備し、前記一対のカバー部1c、1dは前記容量部1bの上面側に位置する前記カバー部1cの厚みt1と、前記容量部1bの下面側に位置する前記カバー部1bの厚みt2とは異なっており、厚みの薄い方の前記カバー部1dにおける角部付近8に絶縁材9が被覆されている。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、電極連結性を制御して容量を確保することができる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、セラミック本体10と、この前記セラミック本体10の内部に形成され、中央部70及び前記この中央部70から縁に向かって薄くなるテーパ部50を有する内部電極30、31と、を含む。前記内部電極30、31の面積に対する前記テーパ部50の面積の比率は、35%以下であることを特徴とする。本発明によると、小型及び高容量の積層型セラミックキャパシタにおいても、電極連結性を制御することにより所望の容量を確保することができる。

(もっと読む)

酸化物導電体を用いた酸化物導電体ペースト及びそれを用いた積層電子部品

【課題】

積層セラミックコンデンサの内部電極の導電材の収縮は通常異なるので、収縮量の差により内部電極が途切れ、クラックやはがれの原因になってしまう。

【解決手段】

酸化物導電ペーストの導電材料として誘電体と焼結温度が近い亜鉛を含む酸化物を用いることにより、被覆率の高い内部電極を持つ積層電子部品が得られた。さらに、Al、Ga、Si、Snのいずれかを含む亜鉛を主成分とした導電性酸化物を用いることにより、必要とする導電性、焼結温度、焼結挙動を制御することが可能になる。これにより、途切れの無い導電性の良い内部電極をもつ積層電子部品が得られた。

(もっと読む)

薄膜キャパシタ、多層配線基板および半導体装置

【課題】インダクタンスを低減すると共に、有効電極面積の減少を抑えて小型化することが可能な薄膜キャパシタ、多層配線基板、および半導体装置を提供する。

【解決手段】誘電体層の上面に第1極性の電極層、前記誘電体層の下面に第2極性の電極層を有し、特定位置の周りに配置された複数の第1容量素子と、前記誘電体層の上面に前記第2極性の電極層、前記誘電体層の下面に前記第1極性の電極層を有し、前記特定位置の周りに前記複数の第1容量素子と交互に配置された複数の第2容量素子と、前記特定位置に設けられ、前記複数の第1容量素子のすべての第1極性の電極層および前記複数の第2容量素子のすべての第1極性の電極層を接続する単一の共通接続孔と、前記共通接続孔の周りに設けられ、前記複数の第1容量素子の各々の第2極性の電極層を、隣接する前記第2容量素子の第2極性の電極層に接続する複数の個別接続孔とを備えた薄膜キャパシタ。

(もっと読む)

1 - 20 / 460

[ Back to top ]