Fターム[5E082GG12]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 端子 (2,765) | 端子の材質(金属等) (366) | 非金属 (47)

Fターム[5E082GG12]に分類される特許

1 - 20 / 47

セラミック電子部品及びその製造方法

セラミック電子部品及びその製造方法

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品及びその製造方法に関する。

【解決手段】誘電体層を含み、誘電体層の積層方向に互いに対向する第1及び第2主面、第1及び第2主面を連結し、互いに対向する長さ方向の第3、第4側面及び幅方向の第5、第6断面を有するセラミック本体と、セラミック本体内で誘電体層を挟んで互いに対向するように配置される第1及び第2内部電極と、第5断面上に形成され、第1内部電極と電気的に連結された一つ以上の第1外部電極及び第6断面上に形成され、第2内部電極と電気的に連結された一つ以上の第2外部電極と、を含んでおり、第1及び第2外部電極は、導電性金属及びガラスを含み、平均厚さが3〜30μmであり、第1及び第2外部電極のうち少なくとも一つを厚さ方向に3等分したときに、中央部領域の面積に対してガラスが占める面積が35〜80%である。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、還元雰囲気の熱処理を要しない積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、内部電極及び外部電極の材料として導電性酸化物を使用し、外部電極上に弾性を有する導電層を形成することを特徴とする。本発明による積層セラミックキャパシタは、大気雰囲気下で焼成を行うことができるため、製造工程が単純になり、製造費用が節減されることができる。

(もっと読む)

チップ型電子部品及びチップ型電子部品の製造方法

【課題】チップ型電子部品が外部から受ける応力を緩和して、チップ型電子部品に発生するクラックを抑制すること。

【解決手段】チップ型電子部品10は、誘電体を含むセラミック素体11と、セラミック素体11の内部に配置され、かつ、セラミック素体11の表面に一部が露出する内部電極17、18と、セラミック素体11の表面に配置された端子電極20、30と、を含む。端子電極20、30は、第1の導電性材料と第1の樹脂とを含み、かつセラミック素体11の内部電極17、18が露出する端面13、14に配置される第1の樹脂層21、31と、第2の樹脂を含むとともに、第1の樹脂層21、31の少なくとも一部と接触し、かつ第1の樹脂層21、31よりもヤング率が低い第2の樹脂層22、32と、を含む。

(もっと読む)

電子部品

【課題】低コストで且つ生産性に優れると共に、狭隣接高密度実装を可能とする電子部品を提供すること。

【解決手段】電子部品1は、素体2と、外部電極3,4と、絶縁性樹脂コーティング層21と、を備えている。素体2は、互いに対向する一対の端面2a,2bと、一対の端面2a,2b間を連結するように伸び且つ互いに対向する一対の主面2c,2dと、一対の主面2c,2dを連結するように伸び且つ互いに対向する一対の側面2e,2fと、を有している。外部電極3,4は、主面2c,2dの一部及び/又は側面2e,2fの一部を少なくとも覆うように形成されると共に、Sn又はSn合金からなるめっき層を有している。絶縁性樹脂コーティング層21は、外部電極3,4における側面2e,2fを覆うように形成された部分を少なくとも覆っている。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性が向上し、信頼性に優れた積層セラミック電子部品を提供する。

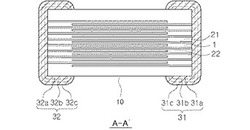

【解決手段】積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、セラミック本体10内で誘電体層1を介して対向配置される第1及び第2内部電極21,22と、第1内部電極21と電気的に連結された第1外部電極31、及び第2内部電極22と電気的に連結された第2外部電極32と、を含む。第1及び第2外部電極31,32は導電性金属及びガラスを含み、第1及び第2外部電極31,32のうちの少なくとも一つを厚さ方向に3等分する際、中央部領域の面積に対してガラスが占める面積は35から80%である。

(もっと読む)

電子部品及び電子部品の製造方法

【課題】電子部品の高密度実装を可能とする電子部品及び電子部品の製造方法を低コストで提供すること。

【解決手段】電子部品1は、素体2、外部電極3,4、及び絶縁層20,21を備えている。素体2は、互いに対向する一対の端面2a,2bと、一対の端面2a,2bを連結するように伸び且つ互いに対向する一対の主面2c,2dと、一対の主面2c,2dを連結するように伸び且つ互いに対向する一対の側面2e,2fと、を有している。外部電極3,4は、素体2の端面2a,2b側に形成され、端面2a,2bに隣接する主面2c,2d及び側面2e,2fの一部を覆う。少なくとも外部電極3,4における側面2e,2f側に位置する電極部分3e,3f,4e,4fの表面が、絶縁層20,21で覆われている。

(もっと読む)

金属化フィルムコンデンサ

【課題】ケースレス構造であって小型化と軽量化が実現され、耐透湿性能に優れた金属化フィルムコンデンサを提供する。

【解決手段】金属化フィルムを巻き回し、もしくは積層させてなる金属化フィルム柱体1の2つの電極取り出し面に外部電極2,2が形成され、金属化フィルム柱体1の電極取り出し面以外の領域を外装フィルム4が被覆してなる金属化フィルムコンデンサ10において、外部電極2は、低透湿性の熱硬化性樹脂接着剤2a内に導電性フィラー2bが含有されてなる導電性接着剤で形成されている。

(もっと読む)

積層セラミックコンデンサ

【課題】 コンデンサ本体と外部電極との接合強度が高い積層セラミックコンデンサを提供する。

【解決手段】 複数の誘電体層5と複数の内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面1aに設けられ、前記内部電極層7と接続された外部電極3とを具備する積層セラミックコンデンサであって、積層セラミックコンデンサを縦断面視したときに、前記コンデンサ本体1の前記端面1aの前記誘電体層5と前記外部電極3との間にSiの酸化物層8を有する。

(もっと読む)

積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法

【課題】内部電極層が位置ずれして積層されても、所定の静電容量を確保できる、寸法安定性に優れた積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法を提供する。

【解決手段】この積層セラミックコンデンサは、静電容量形成部及び引出部を有する第1の内部電極層23及び第2の内部電極層23が、セラミック誘電体層21を介して交互に積層されたセラミック積層体20と、その両端面に形成された外部電極とを備え、第1の内部電極層23の静電容量形成部23aの幅は、第2の内部電極層25の静電容量形成部25aの幅よりも広く形成され、第1の内部電極層23の引出部23bは、その静電容量形成部23aよりも幅狭で、かつ、第2の内部電極層25の引出部25bの幅と等しくなるように形成されている。

(もっと読む)

外部電極用導電性ペースト組成物、これを含む積層セラミックキャパシタ及びその製造方法

【課題】本発明は、外部電極用導電性ペースト組成物、これを含む積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】本発明による外部電極用導電性ペースト組成物は、導電性金属粉末100重量部と、平均粒径が50〜500nmであるセラミック粉末0.1〜10重量部と、を含む。本発明による外部電極用導電性ペースト組成物は、薄膜でも緻密な焼成密度を具現し、電極焼成の際、外部電極の膨れ現象であるブリスター(blister)の発生を抑制して緻密、且つ薄い膜で具現することができる。

(もっと読む)

外部電極用導電性ペースト組成物、これを含む積層セラミックキャパシタ及びその製造方法

【課題】本発明は、チップ信頼性を向上させることができる外部電極用導電性ペースト組成物、これを含む積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】外部電極用導電性ペースト組成物は、導電性金属粉末と、aSiO2−bB2O3−cAl2O3−dTMxOy−eR12O−fR2Oの化学式で組成されるガラスフリットと、を含み、ここで、TMは亜鉛、チタン、銅、バナジウム、マンガン、鉄、ニッケルからなる群から選択された遷移金属であり、R1はリチウム、ナトリウム、カリウムからなる群から選択され、R2はマグネシウム、カルシウム、ストロンチウム、バリウムからなる群から選択され、x、y>0であり、aは15〜70、bは15〜45、cは1〜10、dは1〜50、eは2〜30、fは5〜40モル%の範囲でa+b+c+d+e+f=100モル%となるように夫々選択される。

(もっと読む)

チップ型電子部品の実装構造、チップ型電子部品の実装方法、チップ型電子部品、及びチップ型電子部品の製造方法

【課題】メッキレスの外部電極を用いた場合であってもハンダ濡れ性及び固着強度を好適に確保できるチップ型電子部品の実装構造、チップ型電子部品の実装方法、チップ型電子部品、及びチップ型電子部品の製造方法を提供する。

【解決手段】実装構造1では、SnでコーティングされたCuフィラーと、当該Snの融点以下で熱硬化された樹脂成分とを含む樹脂電極層18によって端子電極13の最外層を形成している。これにより、メッキ層を形成する工程が不要となり、初期絶縁抵抗不良や耐圧不良などが生じることを回避できる。また、ランド電極22には、樹脂電極層18のSnよりも融点の低いハンダペーストが付与されている。このため、ハンダフィレットPの形成の際、ランド電極22上のハンダペーストが先に溶融して端子電極13側に流れ、樹脂電極層18のSnと親和するため、ハンダ濡れ性及び固着強度を確保できる。

(もっと読む)

セラミック電子部品

【課題】内部電極と外部電極との接合強度を向上させると共に、緻密な外部電極を得るセラミック電子部品を提供する。

【解決手段】本発明に係るセラミック電子部品は、セラミック素体と、セラミック素体の内部に設けられ、少なくともPdを含む内部電極と、セラミック素体の端面に設けられ、金属成分として少なくともAgを含むと共に、ガラス成分として結晶化ガラスを含み、内部電極と導通する一対の外部電極とを有し、外部電極は、セラミック素体の端面に、外部電極に含まれる金属成分を形成するための金属粉末と外部電極に含まれるガラス成分を形成するためのガラス粉末とを含む導電性ペーストを塗布し、結晶化ガラスの軟化点Tsより50℃低い温度から結晶化ガラスの軟化点Tsまでの温度であって、Agの融点より150℃以下の温度範囲で焼付けを行うことにより形成される。

(もっと読む)

電子部品

【課題】めっきにより形成された外部電極が積層体から剥離することを抑制できる。

【解決手段】積層体11は、複数のセラミック層が積層されて構成されており、かつ、該複数のセラミック層の外縁が連なって構成されている実装面を有している。コンデンサ導体18は、セラミック層上に設けられており、実装面においてセラミック層間から露出している露出部を有する。外部電極を構成する導電層12,13は、露出部を覆うように設けられ、かつ、直接めっきにより形成されている。導電層14は、導電層12,13を覆うと共に、積層体11の表面の一部を覆っており、金属及びガラス又は樹脂を含む材料により構成されている。

(もっと読む)

積層セラミックコンデンサ

【課題】ショート時に流れる電流を遮断することができ、しかも、ショート状態の再発を防止することができる、積層セラミックコンデンサを提供する。

【解決手段】積層セラミックコンデンサ10は、直方体状のセラミック素体12を含む。セラミック素体12の第1の端面20a上には、第1の内部電極26aと電気的に接続される第1の外部電極34aの導電性高分子膜36が、第1の内部電極26aの第1の露出部32aを被覆するようにして形成される。導電性高分子膜36は、それ自体で導電性を有する導電性高分子を含む。第1の内部電極26aと第2の内部電極26bとの間でショートが発生した場合、導電性高分子膜36においてショートした第1の内部電極26aと接触する部分37が絶縁化する。

(もっと読む)

積層コンデンサ、及び積層コンデンサの実装構造

【課題】実装ミスを防止することのできる積層コンデンサ、及び積層コンデンサの実装構造を提供する。

【解決手段】積層コンデンサ1において、回路基板100などに実装されない接続導体4の最外層21は、端子電極3よりもはんだ濡れ性の低い膜によって形成されており、視覚的にもはんだ濡れ性の良い端子電極3と識別することが可能となる。従って、積層コンデンサ1を回路基板100などに実装する際は、目視によって接続導体4と端子電極3との識別が可能となるため、実装ミスを防止することができる。また、接続導体4の最外層21は、はんだ濡れ性が低いため、誤って接続導体4を回路基板100に実装しようとした場合であっても、はんだ付けを行うことができない。更に、端子電極3のはんだ付けの際のはんだブリッジ不良による実装ミスも防止することができる。

(もっと読む)

積層コンデンサの実装構造

【課題】共振周波数におけるインピーダンスの急激な低下を抑えることができ、かつクラックの発生を抑制できる積層コンデンサの実装構造を提供する。

【解決手段】積層コンデンサ2の実装構造1では、樹脂電極層14が第2コンデンサ部12のESR成分として機能するようなフィレット高さHのハンダフィレット7によって積層コンデンサ2と回路基板6との接続がなされている。これにより、樹脂電極層14の厚みに応じたESR成分が第2コンデンサ部12に付与され、共振周波数におけるインピーダンスのフラット化を実現できる。また、積層コンデンサ2の実装構造1では、第1コンデンサ部11と第2コンデンサ部12との間に間隔Dが設けられている。これにより、回路基板6の変形応力や第1コンデンサ部11の電歪振動による応力が第2コンデンサ部12に伝達しにくくなり、クラックの発生を抑制できる。

(もっと読む)

セラミックコンデンサ

【課題】セラミックコンデンサの電歪現象に起因して発生する音鳴りを抑制すること。

【解決手段】セラミックコンデンサ1は、セラミックコンデンサ素子10と、一対の外部電極20、30と、一対の接続端子40、50と、を有する。一対の外部電極20、30は、セラミックコンデンサ素子10の対向する端面をそれぞれ別個に覆う。一対の接続端子40、50は、それぞれの外部電極20、30と電気的に接続される。そして、接続端子40、50は、ヤング率の異なる材料が少なくとも2層積層されるとともに、最も厚みが大きい層である基材層のヤング率は、他の層のヤング率よりも小さい。さらに、外部電極20、30は、基材層の両面に導電層を有し、両方の導電層を電気的に接続するための導電手段を有する。

(もっと読む)

1 - 20 / 47

[ Back to top ]