Fターム[5E346AA23]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | 基板と基板・層相互の形状、構造が特定されたもの (1,912) | 基板と基板 (1,426) | 誘電性に関するもの (87)

Fターム[5E346AA23]に分類される特許

1 - 20 / 87

多層配線基板およびその製造方法、並びに半導体装置

【課題】薄膜キャパシタの導電層と誘電層との界面での剥離を抑えることが可能な多層配線基板およびその製造方法、並びにこの多層配線基板を備えた半導体装置を提供する。

【解決手段】上部電極および下部電極の間に誘電層を有する薄膜キャパシタを備えた機能領域と、前記機能領域以外の周辺領域とを有し、前記周辺領域の少なくとも一部に、前記誘電層および導電層が積層された係留部が設けられ、前記導電層の前記誘電層に接する面のラフネスが、前記上部電極または前記下部電極の前記誘電層に接する面のラフネスよりも大きい多層配線基板。チップおよび前記多層配線基板を備えた半導体装置。

(もっと読む)

電子部品内蔵型多層基板

【課題】層間密着性に優れ、高温高湿の環境下においても誘電特性の変動が少なく、伝送損失の小さい電子部品内蔵型多層基板を提供すること。

【解決手段】第一の誘電体層4の少なくとも片面に回路パターン3,5により受動素子3a,5aを形成してなる回路板の両面に、第一の誘電体層4よりも低い比誘電率を有する第二の誘電体層2,6を積層してなる積層板を含んでなり、第一の誘電体層4は脂環式構造含有ポリマー及び無機充填剤を含む架橋性樹脂成形体(I)を硬化してなるものである、電子部品内蔵型多層基板。

(もっと読む)

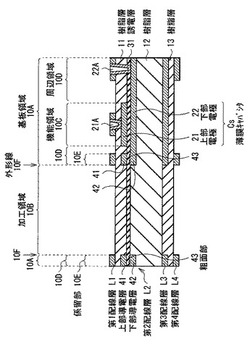

多層導波管、及びその製造方法

【課題】複数の導波管が重ね合わされ、各導波管の内部が誘電体で充填された構成において、高集積化及び軽量化を図ることができるとともに、信頼性を向上させることができる多層導波管、及びその製造方法を提供する。

【解決手段】基礎導波管形成部101と積層導波管形成部102とは、絶縁性の第1の接着剤50により互いに接着されている。基礎導波管形成部101は、互いに間隔をおいて対向配置された板状の第1及び第2の主導体1a,1bと、それらの間に充填された第1の誘電体2とを有している。積層導波管形成部102は、第3の主導体21と、第3の主導体層21の主面に層状に形成された第2の誘電体22とを有している。第2の誘電体22の主面における第2の貫通導体23aの接着剤50に接する側には、第2の誘電体22の主面から突出するように、ランド24が設けられている。

(もっと読む)

表面実装素子および埋め込み素子用の放電保護

電圧切り替え型誘電体材料(VSDM)を含むプリント回路ボードが開示される。このVSDMは、プリント回路ボード上に配置されるかあるいはその中に埋め込まれた電子素子を、静電放電のような放電あるいは電気的な過大ストレスに対して保護するために用いられる。過大電圧事象の間、VSDM層は過剰電流をアースに分路し、それによって電子素子の破壊または損傷を防ぐ。 (もっと読む)

多層配線基板

【課題】寄生インダクタンスの影響を抑え、設計の自由度を保ちつつキャパシタ−レジスタ回路を配置できる多層配線基板を提供する。

【解決手段】複数の絶縁性基板が積層された多層配線基板1は、複数の絶縁性基板の少なくとも1つを貫通する第1接続部21Aを有し、電源を供給する電源パターンと、複数の絶縁性基板の少なくとも1つを貫通する第2接続部22Aを有し、基準電圧を形成するグラウンドパターンと、高誘電率材料からなるキャパシタ部31と、高抵抗材料からなるレジスタ部32と、キャパシタ部とレジスタ部との間に形成される電極部33とを備え、電源パターンとグラウンドパターンとを電気的に直列に接続するように配置されるキャパシタ−レジスタ回路部30とを備え、キャパシタ−レジスタ回路部は、キャパシタ部、レジスタ部、及び電極部が複数の絶縁性基板の面方向に積層されて形成されていることを特徴とする。

(もっと読む)

半導体パッケージ基板

【課題】ノイズ除去性能が高い半導体パッケージ基板を提供する。

【解決手段】この半導体パッケージ基板3では、基板3を貫通して半導体チップ1の電源バンプB1とプリント配線基板2の電源パッドP11とを接続するためのビアホールVH1と、基板3を貫通して半導体チップ1の接地バンプB2とプリント配線基板2の接地パッドP12とを接続するためのビアホールVH2との間に、比誘電率が高く、ビアホールVH1,VH2と略同じ長さを有する絶縁部材7を設け、ビアホールVH1,VH2と絶縁部材7とでコンデンサ8を構成する。したがって、半導体チップ1で発生したノイズは、コンデンサ8でバイパスされる。

(もっと読む)

プリント配線基板および設計支援システム

【課題】簡単なレイアウトでコストアップ無くプリント配線基板の給電系雑音の低減することができるプリント配線基板を提供する。

【解決手段】プリント配線基板101において、半導体装置102の電源端子103とバイパスコンデンサ107の一端とを接続する電源配線110と、プリント配線基板101のグランド層に接続されるビアホール106aと、半導体装置102のグランド端子104とビアホール106aとを接続するグランド引き出し配線111とを備え、バイパスコンデンサ107、電源配線110、電源端子103、およびビアホール106aを同一直線上に配置した。

(もっと読む)

電圧で切替可能な誘電体材料を有するコア層構造

基板およびパッケージデバイスのためのコア層構造が提供される。このコア層構造は、第1の層、第1の層と組み合わされる第2の層、および第1と第2の層の間に設けられた、電圧で切替可能な誘電体(VSD)材料の層を備えている。  (もっと読む)

(もっと読む)

セラミック部品及びその製造方法

【課題】機械的強度に優れていて変形も少ないセラミック基体を有するとともに、セラミック基体との接着強度及び同時焼結性に優れた低抵抗かつ好適形状の導体を有するセラミック部品を提供すること。

【解決手段】本発明のセラミック配線基板10は、銅の融点よりも高い温度で焼結するセラミックを主体とするセラミック基体11に導体18,19,23,27,28が形成されたものである。導体18,19,23,27,28は、無機化合物フィラーと銅との混合相からなる。フィラーは、チタン−アルミニウム系金属化合物、チタン酸化物及びアルミニウム酸化物のうちから選択される少なくとも2種の無機化合物を主体とする。フィラー中のチタン酸化物及びアルミニウム酸化物としては、チタン−アルミニウム系金属化合物が熱分解して酸化することにより生じたものが好適である。

(もっと読む)

キャパシタ内蔵基板およびキャパシタ内蔵基板の製造方法

【課題】導体の脱落を抑制でき、かつ高周波のノイズの遮断が容易なキャパシタ内蔵基板およびキャパシタ内蔵基板の製造方法を提供する。

【解決手段】内蔵基板は、導電層12と基板13とキャパシタ14と導体18とを備え、上面13aにおける貫通孔13bの開口形状の短手方向の寸法が150μm以下であり、かつ短手方向の寸法に対する貫通孔13bの深さの比が2/3以上であり、キャパシタ14から導電層12まで最小の距離をなす方向に対して直交する方向の導体18の面積が0.09mm2以上である。導電層12は接地電位とする。基板13は、導電層12上に形成され、上面13aから導電層12に達する貫通孔13bを有している。キャパシタ14は上面13a上に形成されている。導体18は、貫通孔13bの内部に充填され、導電層12とキャパシタ14とを電気的に接続している。

(もっと読む)

電磁気バンドギャップ構造物及び印刷回路基板

【課題】電磁気バンドギャップ構造物及び印刷回路基板を提供する。

【解決手段】誘電層220、315、325と、複数の導電板210、230、310、320と、上記誘電層を貫通し、その一部分が上記導電板とは異なる平面上を経由して上記導電板と導電板間を電気的に接続させるステッチングビア240と、貫通ビア330と、を含み、上記誘電層、上記導電板、及び上記ステッチングビアは、任意の二つの導電層の間に位置し、上記貫通ビアは上記導電板に設けられたクリアランスホール250、340を貫通して上記任意の二つの導電層を電気的に接続させることを特徴とする電磁気バンドギャップ構造物。

(もっと読む)

キャパシタ、キャパシタ内蔵配線基板、及びその製造方法

【課題】キャパシタ面積が増大することを効果的に抑制するとともに、キャパシタ容量値を調整することのできるキャパシタ、キャパシタ内蔵配線基板、及びその製造方法を提供すること

【解決手段】本発明の第1の態様にかかるキャパシタ1は、基板101上に形成された下部電極102と、下部電極102上に形成された第1絶縁膜103と、第1絶縁膜103を介して下部電極102と対向配置され、下部電極102上に電極開口部106を有する上部電極104と、電極開口部106内に設けられた第2絶縁膜105と、を備え、電極開口部106の側面となる部分の上部電極104は、電極開口部106の底面と重複する部分の下部電極102よりも面積が大きいものである。

(もっと読む)

セラミック多層部品

【課題】異種セラミック同士が多層化された構造を有しながら、焼成によるデラミネーション及び反り等の不具合が抑制されたセラミック多層部品を提供する。

【解決手段】絶縁体部110と、絶縁体部内に配設された複数の電極層120と、を備え、絶縁体部110は、低誘電率層111及び113と、高誘電率層112と、を有し、低誘電率層は、低誘電率層ガラス及び低誘電率層無機フィラーを含有し、高誘電率層は、高誘電率層ガラス及び高誘電率層無機フィラーを含有するセラミック多層部品であって、低誘電率層ガラスと高誘電率層ガラスとは同一組成系であり、セラミック多層部品全体の厚さをDとした場合に高誘電率層112は実装面d1側からD/2の範囲に配設されており、且つ、絶縁体部110のうちの実装面d1側の最外層に厚さDに対して3.5%以上の低誘電率層113を備える。

(もっと読む)

プリント基板とその製造方法

【課題】 プリント基板内層における差動配線において、誘電損失と抵抗損失による高周波成分の減衰とそれによるデジタル信号の波形歪を低減し良好な高速信号特性と低コストを両立させる。

【解決手段】 プリント基板内層における差動配線対の間に、これら差動配線を含む層を上下から挟む誘電体層よりも低誘電率の誘電材料を配置した構造とすることで、差動配線間の前方クロストーク係数を負にし、お互いの前方クロストークが差動信号に重畳することで、波形の立ち上がり、下がりの波形歪を軽減する。

(もっと読む)

誘電体組成物及びこれを用いた積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板

【課題】誘電体組成物及びこれを用いた積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板を提供すること。

【解決手段】主成分として80wt%以上のBaTiO3と、副成分として20wt%以下のCuBi2O4及びZnO−B2O3−SiO2系ガラスを含む誘電体組成物と、セラミックシートの内部電極が印刷された複数のセラミックグリーンシートが積層されたセラミック積層体の内部に、複数の誘電体層と、前記誘電体層の間に形成され前記セラミックシートの内部電極に接続された複数のキャパシタの内部電極を含み、上記誘電体組成物を含む積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板を提供する。

(もっと読む)

多層プリント配線板

【課題】高誘電率の部材で絶縁層を形成する必要のある素子と、インダクタとを近接して配置しても、インダクタの共振周波数を高く保つことが可能な多層プリント配線板を提供する。

【解決手段】多層プリント配線板10は少なくとも第一の絶縁層11、第二の絶縁層12、および第三の絶縁層13が順に重ねて配されてなる。また、第二の絶縁層12と第三の絶縁層13との間には、インダクタ15が形成されている。そして、第一の絶縁層11、第二の絶縁層12、および第三の絶縁層13のうち、少なくとも1つの絶縁層は、他の絶縁層に対して誘電率の異なる部材で形成されている。

(もっと読む)

セラミック多層基板

【課題】チタン酸バリウム系の高誘電率セラミック層と低誘電率セラミック層との積層体を、低温焼成によってデラミネーションやクラックを抑制しつつ接合することである。

【解決手段】低誘電率の絶縁体からなる低誘電率層と高誘電率の誘電体からなる高誘電率層との共焼結によって得られるセラミック多層基板を提供する。低誘電率層は、xBaO−yTiO2−zZnO(x、y、zは、それぞれ、モル比率を示し、x+y+z=1;0.09≦x≦0.20;0.49≦y≦0.61;0.19≦z≦0.42)の組成を有する低誘電率セラミック成分と、この低誘電率セラミック成分100重量部に対して1.0重量部以上、5.0重量部以下添加されている酸化ホウ素含有ガラス成分と含む。高誘電率層が、CuOおよびBi2O3が添加されたチタン酸バリウム系誘電体からなる。

(もっと読む)

電子部品およびその製造方法

【課題】

小型、かつ、湿度や温度の影響を受けにくく、長期的な信頼性の高い電子部品を提供する。

【解決手段】

受動素子を内蔵した低温同時焼成セラミックス(LTCC)基板10と;LTTC基板10の表面上に形成され、インダクタ固定に用いられる固定用樹脂絶縁層31と;固定用樹脂絶縁層31のLTTC基板10側と接触していない表面上に形成されたスパイラル状の金属銅製のインダクタ32と;を備える構成を採用する。

(もっと読む)

多層プリント配線基板

【課題】回路が動作することにより発生する放射ノイズを低減するために最も有効な磁性材料と実装形態を有する多層プリント配線基板を実現・提供すること。

【解決手段】内部導電体層としてグランド層321及び電源層322を有する多層プリント配線基板において、グランド層321及び電源層322の信号層351、352と対向する面上に、結合剤等の非磁性構成要素を含まない磁性体層331、332即ち磁性構成要素のみからなる磁性体層331、332を化学結合又はファン・デル・ワールス力等の作用で隙間なく密着形成した。

(もっと読む)

キャパシタおよび多層配線板

【課題】容易かつ安価に製造することができる高性能のキャパシタを提供すること。また、本発明のキャパシタを実装しても他の回路要素の実装スペースを確保することができる多層配線板を提供すること。

【解決手段】本発明の多層配線板1Aは、2枚の積層配線板3A、3Bの間にキャパシタ2を内蔵している。このキャパシタ2は、2枚の電極5の間に金属ガラス粉末6を含む誘電体4を挟んで形成される。また、このキャパシタ2は、2枚の電極5を上方の積層配線板3Aの把持穴8の周辺に予め形成しておき、その把持穴8に誘電体4を挿入して形成される。

(もっと読む)

1 - 20 / 87

[ Back to top ]