Fターム[5E346HH22]の内容

多層プリント配線板の製造 (97,916) | 目的、課題、効果 (10,213) | 製品性能に関するもの (1,703) | 小型化 (338)

Fターム[5E346HH22]に分類される特許

1 - 20 / 338

プリント基板およびそれを用いた電子機器

【課題】

電子機器において、コネクタや電子部品の接続に用いられるプレスフィット接続に関し、プレスフィット端子近傍のプリント基板が損傷し、プリント基板の耐湿性や実装部品の信頼性を低下させる現象を防止し、高密度実装が可能な電子機器を提供する。

【解決手段】

プリント基板を上面から見たときに、多数のスルーホールのうち隣接するスルーホール間でプレスフィット端子を挿入したときに圧縮力が作用するスルーホール間に、ランド又は最上層の基板と最下層の基板とに挟まれた基板に形成されたスルーホールの内壁面に形成された導体膜に接続する導体膜またはスルーホールの内壁面に形成された導体膜に電気的に接続しない導体膜のいずれかがスルーホールの直径と同じかそれよりも広い幅に亘って存在するようにプリント基板を形成した。

(もっと読む)

コネクタ接続用配線基板、コネクタ接続用配線基板の製造方法、及び基板/配線基板の接続構造

【課題】基板上に回路部品及び電子部品を実装して電子機器の高性能化及び小型化を図るという要請に反することなく、回路基板などの所定の基板と配線基板とを簡易に接続する技術を提供する。

【解決方法】互いに離隔して配設された複数の配線層と、各層が、前記複数の配線層間に配設された複数の絶縁層とを有し、コネクタを有する所定の基板を、前記コネクタを介して接続するための配線基板であって、前記複数の絶縁層の少なくとも一つにおいて、前記配線基板の側面に開口し、前記配線基板の側面から内側に向けて前記コネクタを接続するための凹部が形成され、前記凹部の内壁面において、前記複数の配線層の少なくとも一つと電気的に接続された金属膜が形成されている。

(もっと読む)

電子素子内蔵型印刷回路基板及びその製造方法

【課題】電子素子内蔵型印刷回路基板及びその製造方法を提供する。

【解決手段】本発明に係る印刷回路基板は、キャビティが形成された第1基板と、キャビティにフェースダウン方式で内蔵された第1電子素子と、第1電子素子の上側に積層され、キャビティにフェースアップ方式で内蔵された第2電子素子と、第1基板の上下面にそれぞれ積層された第2基板と、を含むことを特徴とする。

(もっと読む)

表面実装型受動素子部品、部品キャリアテープ、部品内蔵配線板

【課題】板厚み内部に位置させたとき部品端子からの導電路の配置密度を向上させること。

【解決手段】直方体状の素子部材と、素子部材の長手方向の一方向側の端部面である第1の端部面上に、および該第1の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に第1の端部面上と連なるように設けられた第1の端子電極と、素子部材の長手方向の他方向側の端部面である第2の端部面上に、および該第2の端部面に連なる素子部材の少なくとも上面上および下面上のそれぞれ一部に前記第2の端部面上と連なるように設けられた第2の端子電極と、を具備し、第1の端子電極および第2の端子電極が、いずれも、素子部材の上面上に設けられている面積の方が、素子部材の下面上に設けられている面積よりも広い。

(もっと読む)

高周波部品及び通信装置

【課題】小型化を図った高周波部品および通信装置を提供する。

【解決手段】複数の誘電体層を積層してなる積層基板に高周波信号処理回路を備えた高周波部品であって、高周波信号の入力、出力端子および高周波信号処理回路の複数の電源端子を含む端子群が積層基板の一方の主面に形成されており、積層基板を構成する誘電体層には、インダクタンス素子用等のパターン電極が構成され、一端がそれぞれ電源端子に接続された複数の電源ラインは、誘電体層1に形成されたビア電極を介して高周波信号処理回路が有する少なくとも一つの半導体素子に接続され、複数の電源ラインのうち少なくとも二つの電源ラインは、それぞれ、隣接する二以上の誘電体層1にわたって積層方向から見て重なるように形成されたビア電極列2を有し、少なくとも二つの電源ラインのビア電極列2は、隣接する誘電体層間において、他の導体パターンを介さずに近接している。

(もっと読む)

電源制御回路モジュール

【課題】電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供する。

【解決手段】積層体20の表面には、スイッチングレギュレータ用素子31A,31B,31C,31Dおよびリニアレギュレータ用素子32が間隔をおいて実装されている。積層体20の誘電体層202,203の界面には、電極非形成部300によって分離された内部グランド電極2211,2212,2213,2214,2215が形成されている。内部グランド電極2211,2212,2214,2215は、それぞれスイッチングレギュレータ用素子31A,31B,31C,31Dに接続されている。内部グランド電極2213は、リニアレギュレータ用素子32に接続されている。内部グランド電極2211,2212,2213,2214,2215は、それぞれ異なる外部グランド端子に接続されている。

(もっと読む)

配線基板及びその製造方法、半導体パッケージ

【課題】接続信頼性が高く、狭ピッチの接続端子を形成可能な配線基板を提供する。

【解決手段】配線基板1は、無機材料からなる基板本体11に形成された配線パターン12と、前記配線パターンと電気的に接続され、半導体チップが搭載される外部接続端子15と、を備えた無機基板10と、絶縁層31、33、35と配線層32、34、36が積層された有機基板30と、熱膨張係数が前記無機基板よりも大きく前記有機基板よりも小さい材料からなる応力緩和層21と、前記応力緩和層を貫通する貫通配線22と、を備えた接合層20と、を有し、前記無機基板は、前記有機基板上に前記接合層を介して積層され、前記無機基板の配線パターンと前記有機基板の配線層とは、前記貫通配線を介して電気的に接続されている。

(もっと読む)

半導体モジュール

【課題】複数の異種のデバイスを集積して受動部品を内蔵することが可能で、小型薄型化が可能である半導体モジュールを、歩留まり良く製造することを可能にする、高い信頼性を有する半導体モジュールを提供する。

【解決手段】複数層の配線層を絶縁層中に形成して成る多層配線層と、この多層配線層の少なくとも一方の主面に設けられた半導体チップと、この半導体チップを覆う封止材とを有し、多層配線層の両主面及び多層配線層の側面に、同一の材料による封止材が設けられている半導体モジュールを構成する。

(もっと読む)

部品内蔵基板およびその製造方法

【課題】電子部品を内蔵するための開口部を小さくできる部品内蔵基板を提供する。

【解決手段】第1絶縁層3cに第1導電層4c1と層間導通部1c2が形成された第1の基板3Aと、層間導通部1c2と接続される電子部品2と、第2絶縁層3bに第2導電層4b1が形成され、電子部品2を内蔵する位置に開口部6を有する第2の基板2Aと備えた部品内蔵基板10。第2導電層4b1は、平面視枠状の枠状部7b1を有する。開口部6は、枠状部7b1の内側領域8b1全域の第2絶縁層3bを厚さ方向に貫通して形成されている。

(もっと読む)

素子内蔵配線基板、及びその製造方法

【課題】チップ状の電気素子及び膜素子を含む素子内蔵配線基板であって、これらの素子の接続距離を短縮化して高周波特性を改善するとともに、小型化及び高集積化された素子内蔵配線基板を提供する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層、並びにこれらの配線層間に配設された第1の絶縁層を有する両面配線基板と、両面基板の、第1の配線層と対向するようにして設けられた第3の配線層と、第1の配線層及び第3の配線層間に配設された第2の絶縁層と、第2の絶縁層内に配設されるとともに、第1の配線層に実装されてなるチップ状の電気素子と、第1の絶縁層内又は第2の絶縁層内において、第1の配線層と電気的に接続されるとともに、電気素子と相対向するようにして配設され、電気素子より外方に露出したトリミング領域を有する膜素子と、を具える。

(もっと読む)

部品内蔵基板およびその製造方法

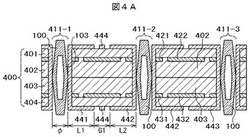

【課題】複数の電子部品を立体的に実装することが容易な、設計自由度の高い部品内蔵基板およびその製造方法の提供。

【解決手段】基板1の面1aに導電層2を備え、導電層2から絶縁基板1の面1bに伸びる層間導通部3を備え、面1b側において層間導通部3と接続される第一電子部品4を備える第一基板1と、基板5の両面に導電回路6が形成され、第一電子部品4を内部に配する空間部S1を設けた両面基板5と、基板7の面7bに導電層8を備え、導電層8から基板7の面7aに伸びる層間導通部9を備え、面7b側において導電層8と接続される電子部品11を備える第二基板7とを備え、第一基板1は、導電層2から当該基板1の面1bに伸びる層間導通部12を介し、両面基板5の面5a側に接続され、第二基板7は層間導通部9を介して両面基板5の面5b側に接続され、第二電子部品11は異方性導電膜13を介し、導電層8と接続される部品内蔵基板10。

(もっと読む)

半導体パッケージ基板及び半導体パッケージ基板の製造方法

【課題】本発明は、半導体パッケージ基板及び半導体パッケージ基板の製造方法に関する。

【解決手段】本発明の一実施例によると、パッドが形成されたキャリア基板を準備する段階と、前記パッドの上部に絶縁層を形成する段階と、前記キャリア基板を除去する段階と、前記絶縁層及び前記パッドの上部に回路層を形成する段階と、前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

(もっと読む)

素子内蔵配線基板、及びその製造方法

【課題】チップ状の電気素子及び膜素子を含む素子内蔵配線基板であって、これらの素子の接続距離を短縮化して高周波特性を改善するとともに、小型化及び高集積化された素子内蔵配線基板を提供する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層、並びにこれらの配線層間に配設された第1の絶縁層を有する両面配線基板と、両面配線基板の、第1の配線層と対向するようにして設けられた第3の配線層と、第1の配線層及び第3の配線層間に配設された第2の絶縁層と、第2の絶縁層内に配設されるとともに、第1の配線層に実装されたチップ状の電気素子と、第1の絶縁層上又は第1の絶縁層内において、第1の配線層と電気的に接続されるとともに、電気素子と相対向するようにして配設され、電気素子より外方に露出したトリミング領域を有する膜素子と、を具えるようにして、素子内蔵配線基板を構成する。

(もっと読む)

多層フレキシブルプリント配線板を用いた表示素子モジュール

【課題】対象機器の両面への液晶等の表示素子実装が可能な内層端子を有する多層フレキシブルプリント配線板の両面に液晶等の表示素子を実装した表示モジュールを提供すること。

【解決手段】部品実装可能な2以上の多層部3、前記多層部から引き出された接続端子を持つ第1の配線層を含む可撓性ケーブル部2,32、および前記多層部間を繋ぐ第2の配線層を含む可撓性ケーブル部を有する多層フレキシブルプリント配線板4,34の接続端子1,31に表示素子6を実装した表示素子モジュールにおいて、前記接続端子を前記多層フレキシブルプリント配線板の一方の面に向け折り曲げて前記表示素子部品を実装するとともに他方の面にチップ部品5,35を実装し、前記可撓性ケーブル部を用いて前記表示素子部品を前記一方の面に向くように折り曲げた表示素子モジュール。

(もっと読む)

配線基板の製造方法

【課題】レーザによりパッドの一部を露出するように絶縁層に形成された開口部と、その開口部に設けられたビアとを備え、開口部を小径化できる配線基板の製造方法を提供する。

【解決手段】支持体上に配線層23と絶縁層24とを交互に積層後、前記支持体を除去して配線基板を得る配線基板の製造方法であって、樹脂からなる支持フィルム74と、前記支持フィルムの一方の面に設けられ、樹脂からなり半硬化状態とされた絶縁層24と、を備えた絶縁層形成部材を準備する絶縁層形成部材準備工程と、前記絶縁層形成部材を前記配線層に貼り付ける絶縁層形成部材貼付工程と、前記絶縁層形成部材を加熱し、前記半硬化状態の絶縁層を硬化させる絶縁層硬化工程と、前記支持フィルムを介して硬化した前記絶縁層にレーザを照射し、前記支持フィルム及び硬化した前記絶縁層に開口部51を形成し、前記配線層の一部を露出させる開口部形成工程と、を含む。

(もっと読む)

薄膜キャパシタ、多層配線基板および半導体装置

【課題】インダクタンスを低減すると共に、有効電極面積の減少を抑えて小型化することが可能な薄膜キャパシタ、多層配線基板、および半導体装置を提供する。

【解決手段】誘電体層の上面に第1極性の電極層、前記誘電体層の下面に第2極性の電極層を有し、特定位置の周りに配置された複数の第1容量素子と、前記誘電体層の上面に前記第2極性の電極層、前記誘電体層の下面に前記第1極性の電極層を有し、前記特定位置の周りに前記複数の第1容量素子と交互に配置された複数の第2容量素子と、前記特定位置に設けられ、前記複数の第1容量素子のすべての第1極性の電極層および前記複数の第2容量素子のすべての第1極性の電極層を接続する単一の共通接続孔と、前記共通接続孔の周りに設けられ、前記複数の第1容量素子の各々の第2極性の電極層を、隣接する前記第2容量素子の第2極性の電極層に接続する複数の個別接続孔とを備えた薄膜キャパシタ。

(もっと読む)

半導体装置の製造方法

【課題】実装効率を維持しながら、信頼性を向上させることを目的とする。

【解決手段】金型内で金属板2に搭載された電子部品の周囲に流動性の高い絶縁樹脂6を圧縮しながら充填し、その後絶縁樹脂6を硬化させることにより、電子部品の損傷や金属線の変形や短絡を防ぎ、配線基板の反りや歪、クラック等の発生を防止して信頼性を向上させながら、高密度に電子部品を配線基板の内部に内蔵することができる。

(もっと読む)

部品内蔵基板

【課題】内部の部品の配置密度をさらに向上できる部品内蔵基板を提供すること。

【解決手段】第1の面と該第1の面に対向する第2の面とを有する板状絶縁層と、棒状の形状を有して該棒状の形状の少なくとも両端面がそれぞれ電極面とされた構造を備え、両端面のうちの一方の端面が第1の面に対向しかつ両端面のうちの他方の端面が第2の面に対向するように、板状絶縁層の厚み方向の内部に配置された部品と、板状絶縁層の第1の面上に設けられた第1の配線パターンと、第1の配線パターンと部品の一方の端面の側の電極面とを電気的に接続する第1の接続部材と、板状絶縁層の第2の面上に設けられた第2の配線パターンと、板状絶縁層の厚み方向の一部を貫通して、第2の配線パターンと部品の他方の端面の側の電極面とを電気的に接続する第2の接続部材とを具備する。

(もっと読む)

多層回路モジュール

【課題】従来のようにICチップやその周りの配線を覆う接地電極パターンを新たに形成することなく、他の電子回路部品の誤動作や特性劣化などを引き起こすようなICチップからの輻射ノイズを抑制することが可能な多層回路モジュールを提供する。

【解決手段】複数の誘電体層を積層してなるコア基板6と、コア基板に少なくとも一部が埋設されるような態様で搭載されたICチップ4と、磁性体基板を素体としてその内部にコイル素子L1,L2が形成されてなるインダクタ基板31とを備え、インダクタ基板31が、平面視したときに、ICチップを覆うような態様でコア基板の表面に搭載された構成とする。

ICチップとインダクタ基板とを電気的に接続する配線が、平面視したときに、インダクタ基板の投影範囲内に収まるように引き回された構成とする。

ICチップがコア基板の内部に埋設された構成とする。

(もっと読む)

半導体装置内蔵基板モジュール及びその実装構造、並びに、半導体装置内蔵基板モジュールの製造方法

【課題】半導体チップを内蔵した基板モジュールにおいて、当該半導体チップの上面側と下面側に設けられた配線層や電極を導通する構成を設けた場合であっても、基板モジュールの平面サイズを小型化することができるとともに、良好な回路特性を実現することができる半導体装置内蔵基板モジュール及びその実装構造並びにその製造方法を提供する。

【解決手段】半導体装置内蔵基板モジュール10は、コア基板11に設けられた開口部11hに半導体装置20が埋め込まれ、コア基板11の上面側及び下面側に積層配線が設けられている。半導体装置20は、シリコン基板21の上面に形成された集積回路と、シリコン基板21の上面側及び下面側に設けられた配線層25a、25b、外部接続用の柱状電極26a、26b、第1、第2の封止層27a、27bと、シリコン基板21の上面側と下面側を導通し、配線層25a、25bに接続された貫通電極22cと、を有している。

(もっと読む)

1 - 20 / 338

[ Back to top ]