Fターム[5F003BM02]の内容

バイポーラトランジスタ (11,930) | 構成材料 (828) | 3−5族 (514)

Fターム[5F003BM02]の下位に属するFターム

三元以上 (275)

Fターム[5F003BM02]に分類される特許

61 - 80 / 239

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

トランジスタ素子用エピタキシャルウェハの製造方法

【課題】HEMT用エピタキシャル層の移動度を低下させることのない、電気特性の良いトランジスタ素子用エピタキシャルウェハを製造することができるトランジスタ素子用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に高電子移動度トランジスタ用エピタキシャル層3を形成し、高電子移動度トランジスタ用エピタキシャル層3上に、ヘテロバイポーラトランジスタ用エピタキシャル層4を形成するトランジスタ素子用エピタキシャルウェハ1の製造方法において、高電子移動度トランジスタ用エピタキシャル層3を、成長温度600℃以上750℃以下、V/III比10以上150以下で成長させ、ヘテロバイポーラトランジスタ用エピタキシャル層4を、高電子移動度トランジスタ用エピタキシャル層3の成長温度よりも低温で成長させる方法である。

(もっと読む)

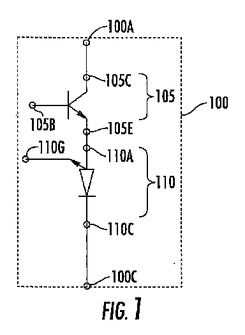

非負の温度係数及び関連した制御回路を有するワイド・バンドギャップ・バイポーラ・ターンオフ・サイリスタ

アノード、カソード及びゲート端子を有するワイド・バンドギャップ・サイリスタと、ベース、コレクタ及びエミッタ端子を有するワイド・バンドギャップ・バイポーラ・トランジスタを含む。バイポーラ・トランジスタとサイリスタとが直列接続されるように、バイポーラ・トランジスタのエミッタ端子は、サイリスタのアノード端子に直接結合される。バイポーラ・トランジスタ及びサイリスタは、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスを特徴付け、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスは、非導通状態と、ベース端子への第一制御信号の印加及びゲート端子への第二制御信号の印加に応答してバイポーラ・トランジスタのコレクタ端子に対応する第1主端子とサイリスタのカソード端子に対応する第2主端子との間に電流を流すことができる導通状態との間を切り替えるように構成される。関連した制御回路も開示される。  (もっと読む)

(もっと読む)

化合物半導体エピタキシャル基板

【課題】電流増幅率を向上させ、基板種に影響されず良好な特性のデバイスを製造できる化合物半導体エピタキシャル基板を提供すること。

【解決手段】GaAs基板2上に、サブコレクタ層41、コレクタ層42、ベース層43、エミッタ層44、エミッタコンタクト層46、47がこの順序で形成されている化合物半導体エピタキシャル基板1において、GaAs基板2とサブコレクタ層41との間に形成されるバッファ層3を酸素を含むAlx Ga1-x As (0≦X≦1)層とし、酸素を含むバッファ層3によりGaAs基板2に存在する欠陥の伝播を抑制し、ベース層43の結晶性を基板種によらず安定かつ良好にできるようにした。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

61 - 80 / 239

[ Back to top ]