Fターム[5F003BM02]の内容

バイポーラトランジスタ (11,930) | 構成材料 (828) | 3−5族 (514)

Fターム[5F003BM02]の下位に属するFターム

三元以上 (275)

Fターム[5F003BM02]に分類される特許

221 - 239 / 239

半導体装置、高周波増幅器および携帯情報端末

【課題】チップ面積の増大を抑制しつつ、電流コラプス現象を低減することができる半導体装置と高周波増幅器を提供する。

【解決手段】半導体装置は、GaAs基板6と、GaAs基板の上に設けられたサブコレクタ層5と、サブコレクタ層5の上の一部に設けられたコレクタ層4と、コレクタ層4の上に設けられたベース層(第1の半導体層)3と、ベース層3のうち真性ベース領域11の上に設けられた第2エミッタ層(第2の半導体層)2aと、ベース層3のうち外部ベース領域2aの上に設けられた第2エミッタ層(第2の半導体層)2bと、第2エミッタ層2aの上に設けられた第1エミッタ層1とを有している。

(もっと読む)

半導体基板、半導体素子、及び半導体発光素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性を、目的とする半導体素子の寸法相当において向上し、これにより半導体素子の特性の高性能化を図る。

【解決手段】 {0001}面から<1-100>方向へのオフ角度の絶対値が0.14°以上0.35°以下、且つ{0001}面から<11-20>方向へのオフ角度の絶対値が0.00°以上0.06°以下の面方位のGaN基板11と、このGaN基板11上に積層された窒化物系III−V族化合物半導体層12と、この窒化物系III−V族化合物半導体層12上の素子構造部(13〜20)とを備える。

(もっと読む)

磁気抵抗トランジスタとその制御方法

【課題】 固定した電圧で異なるエミッタ電流入力を得ることができ、さらに、エミッタ電流入力を制御しながら変化させることによってベース電流を変化することができ、且つ複雑な半導体の製造工程を必要としない磁気抵抗トランジスタを提供する。

【解決手段】 エミッタとして機能する磁気抵抗素子と、コレクタとして機能する受動素子を有する磁気抵抗トランジスタ。そのベースは、その受動素子とその磁気抵抗素子の間に挿入されており、それによってその受動素子とその磁気抵抗素子とを結合している。与えられた強度の磁界がその磁気抵抗トランジスタの少なくとも1つの部分に印加され、その与えられた強度によって磁気抵抗トランジスタのその少なくとも1つの部分の抵抗が決定されている。そうして、与えられる磁界の強度を調整することによって抵抗が調節できる場合もある。

(もっと読む)

トランジスタを具備したフリップチップ構造発光装置用サブマウント

【課題】 本発明はフリップチップ構造の発光装置において発光素子の搭載に用いられるトランジスタ付きサブマウントに関するものである。

【解決手段】 本発明は、フリップチップ構造の発光装置において窒化物半導体発光素子を搭載するためのサブマウントにおいて、第1導電型半導体物質から成る基板; 上記基板上の一領域に形成され第2導電型半導体物質から成る第1領域; 上記第1領域以外の領域に形成され第2導電型半導体物質から成る第2領域; 上記第1領域及び第2領域上に各々形成される第1及び第2電極; 及び、上記基板の背面に形成される導電層を含み、上記第1及び第2電極は上記窒化物半導体発光素子のn側電極及びp側電極とバンプを通して連結されることを特徴とするトランジスタを具備したサブマウントを提供する。本発明によると、フリップチップ構造の発光装置において窒化物半導体発光素子へ流入する静電気などによる高圧電流を遮断して素子の破壊を防止し、素子の信頼性を向上させる効果がある。

(もっと読む)

異種結晶多層構造体ならびに異種結晶多層構造体を含む金属ベーストランジスタ、面発光レーザ、磁気抵抗膜および共鳴トンネルダイオード

【課題】 層同士が異なる結晶構造であり、かつ、結晶性に優れた多層構造体を実現することである。

【解決手段】 結晶構造の異なる2以上の層を含む多層構造体であって、結晶構造を構成する結合軌道が各層で同じである異種結晶多層構造体による。NaCl構造である化合物とCaB6構造である化合物を含む多層構造体、体心立方構造である金属とCsCl構造である化合物を含む多層構造体、CaF2構造である化合物と面心立方構造である金属を含む多層構造体、CaF2構造である化合物と体心立方構造である金属を含む多層構造体などが好ましい。これらの多層構造体によれば、金属ベーストランジスタ1、面発光レーザ、磁気抵抗膜および共鳴トンネルダイオードなどのデバイスが得られる。

(もっと読む)

GaAsをベースとする半導体構造の上に酸化膜層を有する部品及びその形成方法

化合物半導体構造は、支持半導体構造(7)の上に位置して支持半導体構造との界面を形成する酸化ガリウムの第1層(8)を備える。Ga−Gd酸化膜の第2層(9)が第1層の上に配置される。GaAsをベースとする支持半導体構造は、少なくとも一部が完全な半導体装置(例えば、金属−酸化膜電界効果トランジスタ(430)、ヘテロ接合バイポーラトランジスタ(310)、または半導体レーザ)のようなGaAsをベースとするヘテロ構造とすることができる。このようにして誘電体層構造が提供され、この構造は、誘電体構造がGa2O3の層の形成、及びそれに続くGa−Gd−酸化膜の層の形成により得られるので、酸化膜−GaAs界面での欠陥密度が低く、かつ酸化膜リーク電流密度が低い。Ga2O3層を使用してGaAsをベースとする支持半導体構造との間に高品質界面を形成するとともにGa−Gd−酸化膜によって低い酸化膜リーク電流密度が実現する。  (もっと読む)

(もっと読む)

発光半導体素子と発光半導体素子の製造方法

この発明は、半導体本体(1)と基板(2)とを備え、半導体本体(1)がエミッタ領域(3)とベ−ス領域(4)とコレクタ領域(5)とを有する縦型バイポーラトランジスタを備え、領域の各々には接続領域(6,7,8)が設けられ、ベ−ス領域(4)とコレクタ領域(5)との間の境界にpn結合が形成され、そして、動作中、pn結合に逆バイアスが加わり、又は、十分に大きなコレクタ電流が流れると、電荷キャリアのなだれ現象が起こり、コレクタ領域(5)に発光が生じる発光半導体素子に関する。この発明によれば、コレクタ領域(5)は生じた発光が伝送されるような厚みを有し、そして、コレクタ領域(5)は半導体本体(1)の自由面上に境界を成す。このようにして、生じた発光の吸収によるロスが少なくなり、生じた発光をより簡単に、例えば、素子(10)の他の部分又は他の素子(10)のための光信号として用いることができる。コレクタ領域(5)内に第二のサブ領域(5B)が、例えば、半導体本体(1)内に導電チャネルを誘起させるゲート電極(11)をもって形成されてもよい。半導体本体(1)の表面に発光導体(14)が存在すると好ましい。この発明は、さらに、この発明の素子(10)を製造する方法を備える。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

本発明は、それぞれ第1の導電型、第1の導電型と反対の第2の導電型、及び第1の導電型の、エミッタ領域、ベース領域及びコレクタ領域(1、2、3)を有するバイポーラ・トランジスタを備える半導体本体(12)を有する半導体装置(10)に関する。エミッタ領域又はコレクタ領域(1、3)のうちの一方がナノワイヤ(30)を備える。半導体本体(12)の表面における層(20)からベース領域(2)が形成されており、ベース領域(2)の下の半導体本体(12)中にエミッタ領域又はコレクタ領域(1、3)のうちの他方の領域(3、1)が形成されている。ナノワイヤ(30)を備えるエミッタ領域又はコレクタ領域(1、3)は、その縦軸がその表面に対して垂直に延びるように半導体本体(12)の表面上に設けられている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 高周波動作時における各トランジスタの高周波電力利得の差の発生を抑制し、高周波での動作の均一性に優れた半導体装置を提供する。

【解決手段】 半導体装置10は、接地配線の接地距離の長さがより大きいGaAsHBT12のベース引き出し配線14−コレクタ引き出し配線15間に接続された容量素子20の容量をより小さくしている。これによって、各GaAsHBT12の接地インダクタンスの増加に伴う高周波電力利得の低下を、容量素子20の容量の低減による高周波電力利得の増加によって補償することができる。したがって接地インダクタンスの差異によって生じる各GaAsHBT12の高周波電力利得の差を少なくすることができる。このように半導体装置10では、高周波動作時における各GaAsHBT12の不均一な動作の発生を抑制することができる。

(もっと読む)

バイポーラトランジスタ

【課題】容量を自由に調整することができ、さらなる高周波領域での要求に耐えうるバイポーラトランジスタを提供する。

【解決手段】本発明のバイポーラトランジスタは、半導体基板と、前記半導体基板内に形成されたトランジスタ動作領域と、前記半導体基板表面を覆うように形成された絶縁膜と、前記トランジスタ動作領域から前記絶縁膜を貫通し、コレクタ、ベース、エミッタのうちの少なくとも2つにそれぞれ接続され、前記絶縁膜上まで引き出された第1および第2の引出配線と、前記第1および第2の引出配線にそれぞれ接続されるボンディング用の第1および第2のパッドと、前記第1および第2のパッドにそれぞれ接続された第1および第2の容量調整用配線とを備え、第1および第2の容量調整用配線が互いに異なる層で構成される。

(もっと読む)

半導体装置の製造方法とこの方法により得られる半導体装置

この発明は、仮基板(2)を有する半導体基体(1)内において、少なくとも一つの半導体素子(3)が形成され、半導体素子(3)が、半導体基体(1)の基板(2)とは反対側に少なくとも一つの接続領域(4)を備え、そして、前記側に誘電体(5)が形成され、そして、接続領域(4)を露出させるようにパターンニングされ、その後、接続領域(4)と接続するように誘電体(5)上部に金属層(6)が堆積され、金属層(6)が接続領域(4)の電気的接続導電体として機能し、その後、仮基板(2)が除去され、そして、金属層(6)が半導体装置(10)の基板として機能する半導体装置(10)の製造方法に関する。この発明によれば、金属層(6)が堆積される前に、誘電体(5)のパターンニングされた部分の周囲と半導体素子(3)の周囲とに誘電体(5)よりも厚い樹脂のリング状領域(7)が形成され、そして、長方形のリング状領域(7)内部に金属層(6)が堆積される。このようにして、金属層(6)が堆積された後に、好ましくは、装置(10)を領域(7)外部に押圧することにより各装置(10)が容易に形成できる。好ましくは、誘電体(5)と領域(7)とのために(異なる)フォトレジストが選ばれる。この発明は、さらに、このようにして得られる半導体装置(10)を備える。  (もっと読む)

(もっと読む)

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

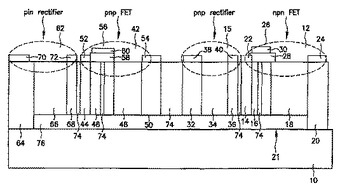

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

多層配線基板及び半導体装置

【課題】エミッタ配線からバイアホール、サーマルビアを介して多層配線基板下面につながる放熱経路の熱抵抗を低減し、半導体装置全体の熱抵抗を低減すること。

【解決手段】厚さ方向に貫通孔4を有する多層配線基板3において、多層配線基板3に実装される半導体基板1がその厚さ方向に貫通孔5を有し、かつ、多層配線基板3及び半導体基板1の厚さ方向と直交する平面内において、半導体基板の貫通孔5の占める領域全体が多層配線基板内貫通孔4の占める領域に含まれている多層配線基板。

(もっと読む)

221 - 239 / 239

[ Back to top ]