Fターム[5F003BP93]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 異方性エッチング (71)

Fターム[5F003BP93]に分類される特許

1 - 20 / 71

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOA(安全動作領域)拡大と良好な静特性とを同時に達成するトランジスタを提供する。

【解決手段】第1導電型のコレクタ層(2)と、前記コレクタ層上に形成される第2導電型のベース層(3)と、前記ベース層上に島状に形成される第1導電型のエミッタ層(4)と、前記ベース層とベース電極(11)とが電気的に接続されるとベースコンタクト(11’)と、前記エミッタ層とエミッタ電極(12)とが電気的に接続されるエミッタコンタクト(12’)と、を有する半導体装置であって、

平面的に見て前記ベースコンタクトと前記エミッタコンタクトとの間に形成されるトレンチ(6)を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

半導体装置及びその製造方法並びにその半導体装置を用いたスーパーヘテロダイン方式の通信機

【課題】バイポーラトランジスタのベース走行時間の低減とエミッタ・ベース接合容量の低減により、遮断周波数と低電流駆動性能の向上を図ったバイポーラトランジスタを提供する。

【解決手段】半導体基板上に設けられた第1導電型の第1の半導体層5と、前記第1の半導体層の上に設けられた第1導電型の第2半導体層6と、前記第2半導体層上に設けられた第2導電型の第3の半導体層7と、該第3の半導体層上に設けられ、開口部を有する第1の絶縁膜9と、前記開口部内に設けられた第1導電型の第4の半導体層11と、前記第4の半導体層上に設けられた第1導電型の第5の半導体層13とで構成され、第4の半導体層が第1の絶縁膜の側壁に接しないように形成し、少なくとも前記第4の半導体層と第1の絶縁膜で囲まれた空洞12を有して成ることを特徴とする。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

バイポーラトランジスタの製造方法及びバイポーラトランジスタ

【課題】バイポーラトランジスタの高周波特性を向上させる。

【解決手段】ヘテロバイポーラトランジスタ70は、ベースとエミッタ、ベースとコレクタがヘテロ接合を有し、双条ベース構造を有する。N型エピタキシャル層3上の内部ベース層(P型SiGe層)5と接する外部ベース層10、及び内部ベース層(P型SiGe層)5上には、絶縁膜7及びN型多結晶シリコン膜8が積層形成される。積層形成された絶縁膜7及びN型多結晶シリコン膜8の中央部にはエミッタ開口部19が設けられる。エミッタ開口部19にはN型エピタキシャル層11が設けられる。N型エピタキシャル層11及びN型多結晶シリコン膜8上には、エミッタ開口部19を覆うようにT型形状を有するN型多結晶シリコン膜12が設けられる。左右のN型多結晶シリコン膜8及びエミッタ開口領域は同時に形成され、左右のN型多結晶シリコン膜8の幅は同一に設定される。

(もっと読む)

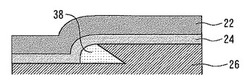

高周波デバイスの誘電体突出部

(例えばシリコン)バイポーラデバイス(40、100、100’)の高周波性能は、外部ベースコンタクト(46)とコレクタ(44、44’、44”)との間の容量結合(Cbc)の低減により向上される。外部ベースコンタクト(46)をコレクタ(44、44’、44”)の外周部(441)から隔てるように、製造中に誘電体突出部(453、453’)が作製される。誘電体突出部(453、453’)は、外部ベースコンタクト(46)を真性ベース(472)に結合するトランジション領域(461)の下に位置する。デバイス製造中に、多層誘電体スタック(45)が真性ベース(472)に隣接して形成され、真性ベース(472)から外部ベースコンタクト(46)へのトランジション領域(461)を形成可能なアンダーカット領域(457、457’)の同時作製が可能にされる。キャビティ(457、457’)内に形成されたトランジション領域(461)が、それをコレクタ(44、44’、44”)の外周部(441)から隔てる誘電体突出部(453、453’)の上に位置することで、ベース−コレクタ接合容量(Cbc)が低減される。デバイスのfMAXが有意に上昇される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体素子の製造方法

【課題】 偶発的に生成される層を異方性エッチングすることにより、エッチングを行う時間によるエッチングのばらつきを改善し、かつ任意の層を異方性エッチングで一定量エッチングすることにより、回り込みエッチングの制御性の向上を図ることを実現する。

【解決手段】 第1の層の表面に第2の層を積層したものに、前記第1の層を横方向にエッチングする半導体素子の製造方法において、前記第2の層側から前記第1の層側に向かって縦方向に異方性エッチングを行うステップと前記第1の層を横方向に等方性エッチングを行うステップとを有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、電極の側方に形成された異種の材料からなる複合膜の残渣の除去を容易に行うことが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、シリコン基板11の電界効果型トランジスタが形成される領域B上にゲート電極を形成する工程と、シリコン基板11のバイポーラトランジスタが形成される領域A上にバイポーラトランジスタを構成するSiGeからなるエピタキシャル層19aを形成する工程と、エピタキシャル層19aの形成時にゲート電極の側方に形成されるSiGeおよび多結晶シリコンからなるエッチング残渣19c、25bおよび43aを除去する工程と、その後、ゲート電極の側方を覆うサイドウォール絶縁膜と、エミッタ電極25の側方を覆うサイドウォール絶縁膜とを形成する工程とを備える。

(もっと読む)

バイポーラトランジスタ基盤の非冷却型赤外線センサ及びその製造方法

【課題】本発明は、バイポーラトランジスタ基盤の非冷却型赤外線センサ及びその製造方法に関する。

【解決手段】基板と、上記基板から浮遊されるように形成された少なくとも一つのバイポーラトランジスタと、上記少なくとも一つのバイポーラトランジスタの上側面に形成された熱吸収層とを含み、上記少なくとも一つのバイポーラトランジスタの夫々は、上記熱吸収層を通じて吸収された熱に従い、出力値を変化させることを特徴とし、これにより、CMOS工程と両立しながらも、より優れた温度変化感知の特性を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】いわゆるメサ型の半導体装置において、耐圧の向上を図ると共に高信頼性の半導体装置及びその製造方法を提供することを目的とする。

【解決手段】レジスト層をマスクとした異方性エッチングで絶縁膜5及び半導体基板1を選択的に除去し、半導体基板1の主面に対して実質的に垂直な側壁を有する溝8を形成する。次に、溝8に対して等方性エッチングする。これにより、溝8の内壁に生じた荒れは除去されて、溝8の内壁が平坦化される。また、同時に水平方向にもエッチングが進行し、溝8の上部10は、半導体基板1の表面側に近付くにつれて広がるように傾斜する。次に、溝8内にパッシベーション膜11を形成する。次に、所定のダイシングラインに沿って半導体基板1等を切断し、チップ状の個々の半導体装置を得る。

(もっと読む)

半導体装置の製造方法

【課題】第1素子の第1電極の表面上に形成される第1絶縁膜を除去する際に、素子分離絶縁膜の端部が除去されることに起因する不都合が発生するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、バイポーラトランジスタ1が形成される領域Aに隣接するように素子分離絶縁膜16bを形成する工程と、エミッタ電極25の表面上にシリコン窒化膜47aを形成する工程と、領域Aに不純物を注入する工程と、少なくとも素子分離絶縁膜16bがスペーサ絶縁膜42により覆われた状態でシリコン窒化膜47aを除去する工程と、シリコン窒化膜47aが除去された後に領域Aおよび素子分離絶縁膜16bを覆うようにシリコン窒化膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の第2素子が形成される領域にエッチングによるダメージが発生するのを抑制しながら第1素子のゲート電極の側面を覆うサイドウォール絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の電界効果型トランジスタ2が形成される領域にゲート電極28を形成する工程と、ゲート電極28の表面およびシリコン基板11のバイポーラトランジスタ1が形成される領域を覆うようにスペーサ絶縁膜42を形成する工程と、スペーサ絶縁膜42を表面から所定の厚み分エッチングすることにより、シリコン基板11のバイポーラトランジスタ1が形成される領域にスペーサ絶縁膜42を所定の厚み分残した状態でゲート電極28の側面を覆うサイドウォール絶縁膜30を形成する工程とを備える。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】半導体層間の隔離構造を改善してコレクタのサイズが減少し、半導体層間の電流が最短経路に流れることができ、コレクタ抵抗が最小化できるバイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタ100の製造方法は、基板101にコレクタ領域102が形成されるステップと、コレクタ領域102を含んだ基板101上にエピタキシャル層115が形成されるステップと、エピタキシャル層115にベース領域103が形成され、ベース領域103にエミッタ領域104が形成されるステップと、エミッタ領域104とベース領域103を貫通してコレクタ領域102までトレンチが形成され、トレンチの側壁に酸化膜108が形成されるステップと、トレンチの内部にポリシリコン層110が形成されるステップとを含む。

(もっと読む)

1 - 20 / 71

[ Back to top ]