Fターム[5F003BP94]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270)

Fターム[5F003BP94]の下位に属するFターム

リフトオフ (34)

エッチングレートの差を利用するもの (76)

酸化後のエッチング (10)

Fターム[5F003BP94]に分類される特許

141 - 150 / 150

メサ型半導体装置の製造方法

【課題】メサ分離溝のエッチングばらつきを低減するメサ型半導体装置の製造方法を提供する。

【解決手段】本発明の製造方法は、n-型半導体ウエハ1の表面側にn++型半導体領域2を形成する工程と、さらにp型不純物を選択的に拡散し、p型半導体領域3を形成する工程と、半導体ウエハ1上に絶縁膜4を形成する工程と、PN接合部を分離するための分離溝8を形成する工程と、PN接合部が露出した分離溝表面を覆うようにガラス保護膜9bを形成する工程を備え、分離溝8を形成する工程において、ウエハ1の表面に形成された自然酸化膜等をフッ化アンモニウムとフッ化水素酸の混合溶液13を用いて除去する工程と、純水を用いて混合溶液13をウエハ1から洗い流す工程と、ウエハ1をフッ酸と硝酸と酢酸の混合液17中に浸してウエハ1をエッチングする工程と、を含む。

(もっと読む)

バイポーラトランジスタを備えた半導体装置及び同半導体装置の製造方法

【課題】

動作を高速化させるとともに、小型化を図ったバイポーラトランジスタを備えた半導体装置及びこの半導体装置の製造方法を提供する。

【解決手段】

バイポーラトランジスタのコレクタ領域の上部に開口を設け、この開口に凹部を有する真性ベース層を設けるとともに、この真性ベース層の凹部にエミッタ層を設ける。さらに、ベース引出し層の開口に、コレクタ領域の上面に形成した絶縁膜の開口部の端縁よりも張出した張出し部を形成し、この張出し部で、真性ベース層とベース引出し層とを接続する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】さらなる微細化の可能なセルフアラインHBTとその製造方法を提供する。

【解決手段】本発明のヘテロ接合バイポーラトランジスタの製造方法では、まず、基板1の上に、コレクタコンタクト層2、コレクタ層3、ベース層4、ベース保護層5、エミッタ層6およびエミッタコンタクト層7、WSi層8を順次形成する。その後、WSi層8の上にレジストパターン9を形成し、レジストパターン9をマスクとしてWSi層8のパターニングを行う。その後、レジストパターン9をマスクとして、ICP方式ドライエッチングにより、エミッタコンタクト層7とエミッタ層6とを順次除去する。ドライエッチングによってエミッタコンタクト層7およびエミッタ層6を除去することにより、エミッタ層6の側面を上面に対してほぼ垂直にすることができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の製造方法として、縦型バイポーラトランジスタの底部に、形状良く低抵抗層を設ける方法を提供する。

【解決手段】2重SOI基板を用意する工程と、ディープトレンチを形成する工程と、ディープトレンチを埋め込む工程と、開口部54を設ける工程と、空孔部56を設ける工程と、多結晶シリコン層80を堆積する工程と、バイポーラトランジスタを形成する工程とを有している。開口部を設ける工程では、ドライエッチングを行って、バイポーラトランジスタ被形成領域55の、第2埋め込み酸化膜40を露出させる。空孔部を設ける工程では、ウェットエッチングにより、バイポーラトランジスタ被形成領域内の第2埋め込み酸化膜を除去する。多結晶シリコン層を堆積する工程では、上述の工程で形成された、互いに連通している開口部及び空孔部に多結晶シリコン層を堆積する。

(もっと読む)

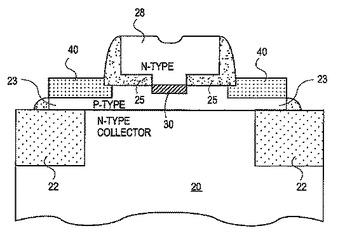

自己整合エピタキシャル成長バイポーラ・トランジスタ

照明システムは、複数個の発光素子(R、G、B)を含む光源(1)を有する。これらの発光素子は、少なくとも第1の原色の第1の発光ダイオードと、少なくとも第2の原色の第2の発光ダイオードとを備え、第1と第2の原色がお互いに異なっている。この照明システムは、発光素子によって発せられた光を平行にするためのファセット光コリメータ(2)を有する。このファセット光コリメータは、照明システムの長手方向軸(25)に沿って構成される。ファセット光コリメータ内の光伝搬は、全内部反射に、又はファセット光コリメータのファセット上に施された反射コーティングでの反射に基づいている。ファセット光コリメータは、光源から離れて面する側で、ファセット光反射板に組み合わせる。この照明システムは、光整形拡散体(17)を更に備える。この照明システムは、均一な空間の及び空間角度色分散で光を発する。  (もっと読む)

(もっと読む)

バイポーラトランジスタおよび関連構造におけるアライメント許容誤差を向上させるための方法

例示的一実施例によれば、ヘテロ接合バイポーラトランジスタ(HBT)などのバイポーラトランジスタは、上面(324)を有するベース(327)を備える。HBTは、ベースの上面に位置する、第1の内部スペーサ(317)および第2の内部スペーサ(318)をさらに備える。HBTは、ベース(327)の上面(324)の上に、第1の内部スペーサ(317)に隣接する第1の外部スペーサ(327)および第2の内部スペーサ(318)に隣接する第2の外部スペーサ(328)をさらに備える。この例示的実施例によれば、HBTは、第1および第2の内部スペーサ(317、318)の間に位置するエミッタ(326)をさらに備える。HBTは、第1および第2の外部スペーサ(327、328)の上に位置する中間酸化層(316)をさらに含んでもよい。HBTは、前記中間酸化層(316)の上に位置するアモルファス層(321)をさらに含んでもよい。HBTは、アモルファス層(321)の上に反射防止膜層(322)をさらに含んでもよい。  (もっと読む)

(もっと読む)

BICMOSプロセスにおいてシード層トポグラフィを軽減する方法

バイポーラデバイスにおいてエピタキシャルベース層を形成する方法。同方法は:活性シリコン領域(10)に隣接したフィールドアイソレーション酸化物領域(12)を有する構造を提供するステップと;前記フィールドアイソレーション酸化物領域(12)上に窒化シリコン/シリコン積層(14,16)を形成するステップであって、前記窒化シリコン/シリコン積層(14,16)はシリコンの上位層(14)と窒化シリコンの下位層(16)とを含む、前記ステップと;階段状シード層を形成するために前記窒化シリコン/シリコン積層(14,16)にエッチングを実行するステップであって、前記窒化シリコンの下位層がエッチングされると同時に前記シリコンの上位層が横方向にエッチングされる、前記ステップと;前記階段状シード層および活性領域(10)とにわたってSi/SiGe/Si積層(20)を成長させるステップと;含む。  (もっと読む)

(もっと読む)

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

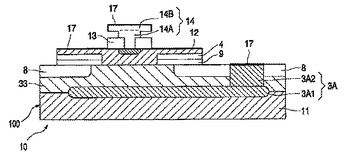

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

141 - 150 / 150

[ Back to top ]