Fターム[5F003BP94]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270)

Fターム[5F003BP94]の下位に属するFターム

リフトオフ (34)

エッチングレートの差を利用するもの (76)

酸化後のエッチング (10)

Fターム[5F003BP94]に分類される特許

41 - 60 / 150

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOA(安全動作領域)拡大と良好な静特性とを同時に達成するトランジスタを提供する。

【解決手段】第1導電型のコレクタ層(2)と、前記コレクタ層上に形成される第2導電型のベース層(3)と、前記ベース層上に島状に形成される第1導電型のエミッタ層(4)と、前記ベース層とベース電極(11)とが電気的に接続されるとベースコンタクト(11’)と、前記エミッタ層とエミッタ電極(12)とが電気的に接続されるエミッタコンタクト(12’)と、を有する半導体装置であって、

平面的に見て前記ベースコンタクトと前記エミッタコンタクトとの間に形成されるトレンチ(6)を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法並びにその半導体装置を用いたスーパーヘテロダイン方式の通信機

【課題】バイポーラトランジスタのベース走行時間の低減とエミッタ・ベース接合容量の低減により、遮断周波数と低電流駆動性能の向上を図ったバイポーラトランジスタを提供する。

【解決手段】半導体基板上に設けられた第1導電型の第1の半導体層5と、前記第1の半導体層の上に設けられた第1導電型の第2半導体層6と、前記第2半導体層上に設けられた第2導電型の第3の半導体層7と、該第3の半導体層上に設けられ、開口部を有する第1の絶縁膜9と、前記開口部内に設けられた第1導電型の第4の半導体層11と、前記第4の半導体層上に設けられた第1導電型の第5の半導体層13とで構成され、第4の半導体層が第1の絶縁膜の側壁に接しないように形成し、少なくとも前記第4の半導体層と第1の絶縁膜で囲まれた空洞12を有して成ることを特徴とする。

(もっと読む)

半導体積層体を含む半導体装置の製造方法

【課題】 半導体下層と半導体上層が積層された半導体積層体において、半導体下層の表面に損傷を与えることなく、半導体下層の一部を露出させる技術を提供する

【解決手段】 半導体下層18の表面の一部に、半導体上層15とは格子定数の異なる格子不整合層30を形成する工程と、格子不整合層30の表面と格子不整合層30で被覆されていない半導体下層18の表面に、半導体上層15を結晶成長させる工程と、格子不整合層30上の半導体上層15に形成された転位40を介してウェットエッチング液を導入し、格子不整合層30とその格子不整合層30上の半導体上層15を除去して半導体下層18の一部を露出させる工程を備える。ドライエッチングにより半導体下層18に損傷を与えることなく、半導体下層18の一部を露出させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストを抑えつつ、ガードリングに接するPN接合部の耐圧の向上を図る。

【解決手段】半導体基板10の表面にN−型半導体層11を形成し、その上層にP型半導体層12を形成する。P型半導体層12上には、絶縁膜13を形成する。その後、絶縁膜13からN−型半導体層11の厚さ方向の途中に至る複数の溝、即ち第1の溝17A、第2の溝17B、第3の溝17Cを形成する。これらの複数の溝は、そのうち互いに隣接する2つの溝において、電子デバイスに近い側、即ちアノード電極14に近い側の溝は、該溝よりも外側の他方の溝よりも浅く形成される。その後、第1の溝17A内、第2の溝17B内、第3の溝17C内に、絶縁材料18が充填される。その後、半導体基板10及びその上層に積層された各層からなる積層体をダイシングラインDLに沿ってダイシングする。

(もっと読む)

トランジスタデバイス及びその製造方法

トランジスタデバイス(600)の製造方法であって、この製造方法が、基板(102)中に溝(106)を形成するステップと、この溝(106)を電気絶縁材料(202)により部分的にのみ充填するステップと、部分的にのみ充填された溝(106)を介して前記トランジスタデバイス(600)のバイポーラトランジスタ(608)のコレクタ領域(304)にインプラント処理するステップとを有するトランジスタデバイスの製造方法を提供する。  (もっと読む)

(もっと読む)

バイポーラトランジスタの製造方法

【課題】各拡散領域を形成する際のアライメントずれを抑制することができ、各拡散領域の位置精度が高く、電気特性のばらつきを低減することのできるバイポーラトランジスタの製造方法を提供する。

【解決手段】N型半導体基板10の表層部に、ベース領域であるP型拡散領域30、エミッタ領域である第1のN型拡散領域31およびコレクタ領域である第2のN型拡散領域32a,32bを形成するバイポーラトランジスタ100の製造方法であって、半導体基板上10に、複数の開口部を有するLOCOS酸化膜20を形成し、所定の開口部を介して不純物をイオン注入し、P型拡散領域30または第1のN型拡散領域31の一方を最初に形成し、次に、縮小または拡大された前記所定の開口部を介して不純物をイオン注入し、P型拡散領域30または第1のN型拡散領域31のもう一方を形成する製造方法とする。

(もっと読む)

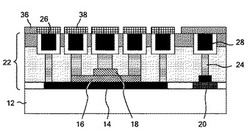

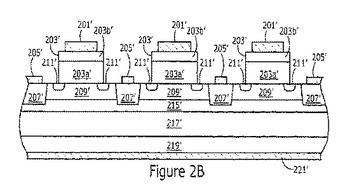

高周波デバイスの誘電体突出部

(例えばシリコン)バイポーラデバイス(40、100、100’)の高周波性能は、外部ベースコンタクト(46)とコレクタ(44、44’、44”)との間の容量結合(Cbc)の低減により向上される。外部ベースコンタクト(46)をコレクタ(44、44’、44”)の外周部(441)から隔てるように、製造中に誘電体突出部(453、453’)が作製される。誘電体突出部(453、453’)は、外部ベースコンタクト(46)を真性ベース(472)に結合するトランジション領域(461)の下に位置する。デバイス製造中に、多層誘電体スタック(45)が真性ベース(472)に隣接して形成され、真性ベース(472)から外部ベースコンタクト(46)へのトランジション領域(461)を形成可能なアンダーカット領域(457、457’)の同時作製が可能にされる。キャビティ(457、457’)内に形成されたトランジション領域(461)が、それをコレクタ(44、44’、44”)の外周部(441)から隔てる誘電体突出部(453、453’)の上に位置することで、ベース−コレクタ接合容量(Cbc)が低減される。デバイスのfMAXが有意に上昇される。  (もっと読む)

(もっと読む)

41 - 60 / 150

[ Back to top ]