Fターム[5F003BP94]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270)

Fターム[5F003BP94]の下位に属するFターム

リフトオフ (34)

エッチングレートの差を利用するもの (76)

酸化後のエッチング (10)

Fターム[5F003BP94]に分類される特許

61 - 80 / 150

半導体装置およびその製造方法

【課題】追加部材を形成することなく表面保護膜の端部での剥がれを防止でき、チップエッジからの水分浸入を防止して信頼性(耐湿性)を向上できる半導体装置を提供する。

【解決手段】この半導体装置では、エピタキシャル層4Aを覆う表面保護膜11が高抵抗GaAs層(素子間絶縁層)5の外周側の外周エピタキシャル層4A−1の一部を覆って上記一部に接しているので、表面保護膜11の端部の密着性が向上して外部からの水分侵入を防止できる。

(もっと読む)

半導体デバイスの製造方法

【課題】犠牲層を介してInP系のデバイスを形成したときに、犠牲層としてAlAs単層を用いたときのデバイス特性よりも良好なデバイス特性を得ることができ、かつ、犠牲層をエッチングする際に、デバイス層もエッチングされてしまう虞のない半導体デバイスの製造方法を提供する。

【解決手段】保護膜35の平坦面35Aに支持基板10を接合もしくは接着したのち、InPと疑似格子整合するInAlAsからなる犠牲層42を、フッ酸を用いて選択的に除去することにより、InP基板41を、InP系のデバイス層21を含む支持基板10から剥離する。

(もっと読む)

半導体装置

【課題】正のサージが印加された場合に、従来の半導体装置よりもブレークダウン電圧を高くすることなくサージ電流による発熱を抑制することができ、サージ保護素子が破壊されることを防止することができる半導体装置を提供する。

【解決手段】コレクタ層7に第1のトレンチ8を形成し、第1のトレンチ8の底面および側壁のうち底面側の端部を覆い、第1のトレンチ8の底面からコレクタ層7の裏面方向と第1のトレンチ8の底面と平行な方向、および第1のトレンチ8の底面の端部からコレクタ層7の表面方向に不純物を拡散させることにより高濃度層9を形成する。

(もっと読む)

半導体装置

【課題】 エッチング量を工程内で測定し、フィードバックをかけることにより、エッチング量のばらつきを無くすことを実現する。

【解決手段】 半導体層が選択エッチングされることにより半導体素子が形成される半導体素子領域と、前記半導体層と同じ材質からなり、前記半導体素子が選択エッチングされた量を検査するモニタ用半導体素子が設けられたモニタ領域とを有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トレードオフの関係にあるHBTの特性上のメリットとHFETの特性上のメリットとを両立することが可能な半導体装置及びその製造方法を提供する。

【解決手段】Bi−HFETであって、HBTは、順次積層されたサブコレクタ層107、GaAsコレクタ層108、GaAsベース層109及びInGaPエミッタ層110を有し、サブコレクタ層107は、GaAs外部サブコレクタ領域107aと、GaAs外部サブコレクタ領域107a上に位置するGaAs内部サブコレクタ領域107bとを有し、GaAs外部サブコレクタ領域107a上には、メサ状のコレクタ部830と、コレクタ電極203とが離間して形成され、HFETは、GaAs外部サブコレクタ領域107aの一部により構成されたGaAsキャップ層105と、GaAsキャップ層105上に形成されたソース電極304及びドレイン電極305とを有する。

(もっと読む)

半導体素子の製造方法

【課題】 偶発的に生成される層を異方性エッチングすることにより、エッチングを行う時間によるエッチングのばらつきを改善し、かつ任意の層を異方性エッチングで一定量エッチングすることにより、回り込みエッチングの制御性の向上を図ることを実現する。

【解決手段】 第1の層の表面に第2の層を積層したものに、前記第1の層を横方向にエッチングする半導体素子の製造方法において、前記第2の層側から前記第1の層側に向かって縦方向に異方性エッチングを行うステップと前記第1の層を横方向に等方性エッチングを行うステップとを有することを特徴とする。

(もっと読む)

半導体基板と半導体基板の製造方法

【課題】フローティングボディを備える半導体基板と半導体基板の製造方法を提供する。

【解決手段】基板領域110、絶縁領域130及びフローティングボディー領域150を備える半導体基板。絶縁領域130は、基板領域110上に位置する。フローティングボディー領域150は、絶縁領域130により基板領域110から分離され、絶縁領域130上に位置する。基板領域110とフローティングボディー領域150とは同じ特性を持つ材質で形成される。バルク基板をエッチングして少なくとも一つのフローティングボディーパターンを形成する第1工程と、フローティングボディーパターン下部のバルク領域をエッチングして、バルク基板を基板領域とフローティングボディー領域とに分離する第2工程と、フローティングボディー領域と基板領域との間を絶縁物質で満たす第3工程と、を含む半導体基板の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、電極の側方に形成された異種の材料からなる複合膜の残渣の除去を容易に行うことが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、シリコン基板11の電界効果型トランジスタが形成される領域B上にゲート電極を形成する工程と、シリコン基板11のバイポーラトランジスタが形成される領域A上にバイポーラトランジスタを構成するSiGeからなるエピタキシャル層19aを形成する工程と、エピタキシャル層19aの形成時にゲート電極の側方に形成されるSiGeおよび多結晶シリコンからなるエッチング残渣19c、25bおよび43aを除去する工程と、その後、ゲート電極の側方を覆うサイドウォール絶縁膜と、エミッタ電極25の側方を覆うサイドウォール絶縁膜とを形成する工程とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得、高周波特性が良好であり、かつ微細化することができるようにする。

【解決手段】基板1上に、コレクタ層3、ベース層4、エミッタ層およびキャップ層9を順次積層する。エミッタ層が、ベース層4に接したバリア層14とキャップ層9に接したキャリア供給層13との積層構造から形成されている。バリア層14のバンドギャップが、キャリア供給層13のバンドギャップよりも大きく、バリア層14とキャリア供給層13とが、タイプI型のヘテロ接合を形成している。キャリア供給層13を構成する半導体が、不純物添加によって縮退している。

(もっと読む)

静電気保護用半導体素子

【課題】面積を増大させることなく、サージ耐量を向上させた静電気保護用半導体素子を提供することを課題とする。

【解決手段】

素子領域は、トレンチ形状のトレンチ絶縁膜5およびポリシリコン膜11により、他の素子とは完全に絶縁分離されている。また、素子領域の上には、熱酸化処理によってLocos酸化膜12が形成されており、このLocos酸化層12の上には層間絶縁膜13が形成され、層間絶縁膜13を貫通するコレクタ電極14、ベース電極15、エミッタ電極16が接続されている。ポリシリコン膜11には、トレンチバイアス用電極17が接続されており、トレンチバイアス用電極17には、電源18から負バイアスが印加される。この負バイアスにより、トレンチ絶縁膜5に近いn+型埋め込み領域3及びn型半導体層4内に正孔が偏在し、これにより電子の流れの中心はpn接合の中心だけではなく、トレンチ絶縁膜5側にシフトする。

(もっと読む)

半導体装置

【課題】応答性に優れ、瞬間的な動作や過大入力がある場合においてもダイオード素子の順方向動作時の損失増加や過剰電流による絶縁ゲートトランジスタ素子の破壊を防止できる小型の半導体装置を提供する。

【解決手段】絶縁ゲートトランジスタ素子21とダイオード素子22とが同じ半導体基板に形成され、絶縁ゲートトランジスタ素子21とダイオード素子22が逆並列に接続されてなる半導体装置60であって、ダイオード素子22に電流が流れた場合に、絶縁ゲートトランジスタ素子21のゲート(G)端子の電位を下げて、該絶縁ゲートトランジスタ素子21のゲートをオフする第1制御トランジスタ素子ST1が、前記半導体基板に形成されてなる半導体装置60とする。

(もっと読む)

電極構造、ヘテロ接合バイポーラトランジスタおよびそれらの製造方法

【課題】Auの拡散を抑制して、電流利得が突然劣化するのを防止する。

【解決手段】基板1上にサブコレクタ層2を形成し、サブコレクタ層2上にコレクタ層3を形成し、コレクタ層3上にベース層4を形成し、ベース層4上にエミッタ層5を形成し、エミッタ層5上にエミッタコンタクト層6を形成し、エミッタコンタクト層6上にTiからなるコンタクト用金属層7を形成し、コンタクト用金属層7上にWからなるAu拡散防止用のバリアメタル層8を形成し、バリアメタル層8上にTi/Pt/Au/Pt/Tiからなる低抵抗金属層9を形成し、エミッタ層5、エミッタコンタクト層6およびコンタクト用金属層7、バリアメタル層8、低抵抗金属層9からなるエミッタ電極の側面を覆うシリコン窒化膜10を形成する。

(もっと読む)

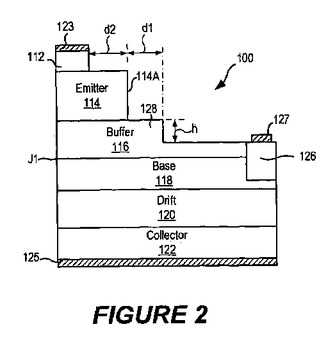

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】 高温時のウェーハ反りを抑制し、チッピングや欠けを回避した自己発熱を半導体基板裏面から放熱できる放熱特性改善がされた薄型半導体装置及び製造が容易なその製造方法を提供する。

【解決手段】 複数の素子領域及び当該素子領域を区画する素子分離領域14を有する半導体基板9と、素子領域に形成された半導体素子とを有する。素子分離領域は、DTI(Deep Trench Isolation) 構造であり、その底面は半導体基板9裏面に露出し、その内部は空洞になっている。この半導体基板は半導体素子を形成後に半導体基板裏面を素子分離領域14の底面が露出するまで研磨もしくはエッチングして半導体基板9を薄くすると共に素子分離領域14内部を空洞にする。

(もっと読む)

半導体装置の製造方法

【課題】不純物を拡散させる熱処理を低温化・短時間化し、かつ、良品率を向上させること。

【解決手段】親水性膜19を成膜するステップと、親水性膜19の開口部22により露出する基板表面25を親水性膜19とともに薬液で処理するステップと、基板表面25に隣接するように成膜されたポリシリコン膜32に注入された不純物をポリシリコン膜32から基板8に拡散させるステップとを備えている。このとき、半導体装置は、基板表面25が薬液で処理されることにより、基板8とポリシリコン膜32との界面に膜が形成されることが防止され、ポリシリコン膜32から基板8に不純物を拡散させる熱処理を低温化し、または、短時間化することができる。さらに、半導体装置は、薬液で処理されるときに用いられた液体が親水性膜19の表面に残ることが防止され、ウォーターマークが生成されることが防止され、パターン異常の発生が防止される。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、第1素子のゲート電極および第2素子の電極部のそれぞれの側面を覆うサイドウォール絶縁膜の幅を異ならせることが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域B上にゲート電極28を形成する工程と、シリコン基板11の領域Aにスペーサ絶縁膜42を、ゲート電極28の側面および領域Aを覆うように形成することにより、領域Aを覆う保護膜と、ゲート電極28の側面を覆う絶縁膜42aを形成する工程と、その後、領域A上にエミッタ電極25を形成する工程と、ゲート電極28およびエミッタ電極25を覆うようにシリコン酸化膜49を形成する工程と、スペーサ絶縁膜42およびシリコン酸化膜49をエッチングすることにより、絶縁膜42aを覆う絶縁膜30aを形成するとともに、エミッタ電極25の側面を覆うサイドウォール絶縁膜26を形成する工程とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】 複数個の半導体素子を備えている半導体装置において、その半導体装置のサイズを小さくする技術を提供する。

【解決手段】 不純物注入工程では、半導体基板9の表面にn型半導体領域13とp型半導体領域14が隣接して出現する関係に不純物の注入範囲を管理して、不純物を半導体基板9に注入する。熱処理工程では、半導体基板9を加熱して半導体基板9に注入した不純物12、14を活性化する。トレンチ形成工程では、半導体基板9の表面に隣接して出現しているn型半導体領域13とp型半導体領域14の双方を分断して一巡するととともに半導体基板9の表面から半導体基板9の裏面に向けて不純物の注入範囲12、14を貫通する深さにまで伸びているトレンチ15を形成する。絶縁膜形成工程では、トレンチ15内に絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の中に分離領域を熱拡散により形成する際に、その横方向拡散を抑制して、半導体集積回路の微細化を実現する。

【解決手段】第3のホトレジスト24をマスクとして、第3の開口部K3から、ボロン(B+)をエピタキシャル層21にイオン注入してP型の不純物領域25を形成する。そして、シリコン酸化膜23上に、P型の不純物領域25と部分的にオーバーラップする領域に第4の開口部K4(リン注入領域)を有する第4のホトレジスト26を形成する。第4のホトレジスト26をマスクとして、P型の不純物領域25が除去されたエピタキシャル層21の表面にリン(P+)をイオン注入して、P型の不純物領域25に隣接したN型の不純物領域28を形成する。その後、熱拡散を行うことにより、エピタキシャル層21の中にP型の上分離領域29が形成され、この上分離領域29と下分離領域22とは連結されて分離領域30が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積を従来に比して小さくすることが可能な、半導体素子の分離技術を提供することを目的とする。

【解決手段】N−半導体層3の表面にN+半導体層4、P半導体層5,N+半導体層6を形成する。次に、N+半導体層4の内側に開口部を有するレジスト層7を形成する。次に、当該レジスト層7をマスクとして半導体基板1を選択的にエッチングしてN+半導体層4を分断する溝8を形成する。分断されたN+半導体層4をN+半導体層4a,4bとする。次に、溝8の内部をシリコン酸化膜等の絶縁膜9で埋設する。次に、P半導体層5(ベース領域),N+半導体層6(エミッタ領域),N+半導体層4a,4b(コレクタ領域)、の各表面に至るコンタクトホールを有するシリコン酸化膜10を形成する。次に、各コンタクトホール内にベース電極11,エミッタ電極12,コレクタ電極13を形成する。

(もっと読む)

61 - 80 / 150

[ Back to top ]