Fターム[5F004CA02]の内容

半導体のドライエッチング (64,834) | 装置の操作、制御方法 (5,292) | ガス圧力、流量 (1,078)

Fターム[5F004CA02]に分類される特許

141 - 160 / 1,078

真空処理装置

【課題】

真空処理室の残留ガスと導入ガスを高速に置換することのできる真空処理装置を提供する。

【解決手段】

真空処理室109内に、それぞれ異なるガスを導入する複数の処理ステップにより試料117の処理を行なう真空処理装置において、複数の処理ステップを継続する時、前ステップ終了時のガス流量を定常処理時の設定値より減少させる、または後ステップの開始時のガス流量を設定値より増加させる、または前ステップ終了時のガス流量を設定値より減少させ、且つ後ステップの開始時のガス流量を設定値より増加させる。これにより高速置換が可能となり安定した真空処理が実現できる。

(もっと読む)

シリコン含有膜の平滑SiConiエッチング

シリコン含有材料をエッチングする方法を説明する。この方法は、フッ素と比べた水素の流量比が従来技術で見られる流量比よりも大きい、または小さいSiConi(登録商標)エッチングを含む。このように流れ比率を修正すると、エッチング後の表面の粗さが低減し、かつ高密度にパターニングされた区域と低密度にパターニングされた区域との間のエッチング速度の差が低減することが分かった。エッチング後の表面粗さを低減する代替手段には、前駆体流および/またはプラズマ出力をパルス化することが含まれ、それによって相対的に高い基板温度が維持され、複数のステップでSiConi(登録商標)が実施される。これらの取組みのそれぞれは、単独または組合せで固体残留物粒径を限定することによって、エッチングされた表面の粗さを低減するのに役立つ。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線構造を形成する際に、ウェハ面内の配線溝の深さのばらつきを抑え、均一加工を実現する。

【解決手段】高炭素濃度絶縁膜114と、炭素を含まないまたは炭素濃度が低い低炭素濃度絶縁膜116との積層構造にドライエッチングで配線溝を形成する際、CHF系ガスを添加した第1のエッチングガスを用いた第1のエッチング条件で低炭素濃度絶縁膜116に配線溝を形成し、当該配線溝底部に高炭素濃度絶縁膜114を露出させる。第1のエッチング条件の第1のエッチングガス中のCHF系ガスの分圧は、第1のエッチングガスに当該CHF系ガスを添加していない場合の各膜へのエッチングレートを基準として、当該CHF系ガスを添加することにより、高炭素濃度絶縁膜114に対するエッチングレートが低下するとともに、低炭素濃度絶縁膜116に対するエッチングレートを変化させない範囲に設定されている。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】 本発明の目的は、クリーニング時間を短縮し、生産性を向上させることのできる半導体装置の製造方法および基板処理装置を提供することにある。

【解決手段】 処理容器内の下部から上部まで立ち上がった第1ノズル部、第2ノズル部を介して、それ単独で膜を堆積させることのできる第1ガス、それ単独で膜を堆積させることのできない第2ガスをそれぞれ処理容器内に供給してその下方に向けて流し、処理容器の下部に設けられた排気口より排気して、基板上に薄膜を形成する処理を繰り返した後、処理容器の天井壁に設けられた第3ノズル部を介してハロゲン系ガスに第2ガスの少なくとも一部を添加したガスを処理容器内に供給すると共に第1ノズル部を介してハロゲン系ガスを処理容器内に供給してその下方に向けて流し、排気口より排気して処理容器内および第1ノズル部内に付着した堆積物を除去するようにした。

(もっと読む)

パルスプラズマを用いた原子層エッチング

高速の原子層エッチング(ALET)を行うシステムおよび方法であり、パルスプラズマ源と、反応チャンバを有している。プラズマ源は、螺旋状コイル電極と、冷却されるファラデーシールドと、管の上部に配置されたカウンタ電極と、ガス注入口とを有し、反応チャンバは基板サポートと境界電極を有する。この方法は、プラズマエッチングチャンバの中にエッチング可能な基板を設置する段階と、基板の表面上に生成層を形成する段階と、プラズマ源をパルス駆動することによって生成層の一部を除去する段階と、その後、生成層を形成する段階と生成層の一部を除去する段階とを繰り返してエッチングされた基板を形成する段階を有する。  (もっと読む)

(もっと読む)

ドライエッチングガス及びそれを用いたドライエッチング方法

【課題】半導体デバイスの製造プロセスにおいて、シリコン酸化膜、窒化シリコン膜、シリコン含有低誘電率膜等のシリコン含有膜のエッチング速度の低下を防ぎ、レジストや下地のシリコンなどに対して、選択的にエッチングすることができるドライエッチングガス及びそれを用いたエッチング方法を提供する。

【解決手段】CF3CF=CH2を含むドライエッチングガス。CF3CF=CH2の含有率は、流量比5〜100%であることが好ましい。

(もっと読む)

半導体発光装置および半導体発光装置の製造方法

【課題】個々の半導体発光装置を区画する素子分割溝を形成することによって表出した半導体膜の側面の所定位置で終端している保護膜を安定的に形成することにより、高い歩留りを確保する。

【解決手段】成長用基板の上に半導体膜20を形成し、半導体膜20に成長用基板に達する素子分割溝を形成し、素子分割溝を形成することによって表出した半導体膜20の側面を部分的に覆い且つ成長用基板から離間している保護膜50を形成する。素子分割溝を形成する工程は、エッチングによる表出面の半導体膜20の主面に対する傾斜角が第1の傾斜角を有するように半導体膜20をエッチングする第1エッチング工程と、第1エッチング工程の後に、エッチングによる表出面の半導体膜20に対する傾斜角が第1の傾斜角よりも大きい第2の傾斜角を有するように半導体膜20をエッチングして傾斜角が異なる表出面を形成する第2エッチング工程と、を含む。

(もっと読む)

コンビナトリアル式プラズマプロセス試験方法及び傾斜プラズマ発生装置

【課題】プラズマプロセスの外部条件を容易に最適化する。

【解決手段】本発明によれば、小型のプラズマ発生装置を用い、例えば4.Aに示されるようにプラズマ密度が位置によって異なり、4.Bに示されるようにラジカル密度が位置によって異なる状態を形成できる。そこでこのような小型のプラズマ発生装置に、プラズマプロセスの被処理物や材料形成基板を配置し、当該被処理物等の表面でプラズマ密度やラジカル密度を測定しながらプラズマプロセスを実行する。プラズマプロセスの結果物を位置ごとに評価し、最も評価の高くなる位置でのプラズマ密度やラジカル密度を決定する。この上で、他の、大型或いは一括処理形のプラズマプロセスにおいて、当該最適なプラズマ密度やラジカル密度が生成できるように外部条件を調整する。この調整の際には、被処理物等をプラズマ処理等する必要がない。

(もっと読む)

基板処理方法,基板処理装置,プログラムを記録した記録媒体

【課題】基板面内における堆積度合いのばらつきを効果的に抑制する。

【解決手段】被エッチング膜上に形成された反射防止膜上に,複数の開口部を有するレジストパターンが形成された基板に対して,被エッチング膜をエッチングする前にレジストパターンの各開口部の側壁に堆積物を堆積させるステップを有し,堆積ステップは処理室内の圧力を100mTorr以上にし,CHF系ガスを1000sccm以上導入してプラズマを生起する。

(もっと読む)

基板処理装置及びそのクリーニング方法並びにプログラムを記録した記録媒体

【課題】下部電極のセルフバイアス電圧を上げることなく,基板載置台の付着物の除去レートを上げる。

【解決手段】処理室102内を所定の処理条件に基づいてクリーニングする際に,O2ガスと不活性ガスからなる処理ガスを下部電極111のセルフバイアス電圧に応じてその絶対値が小さいほど,O2ガスの流量比が減少しArガスの流量比が増大するように設定した流量比で処理室内に供給し,下部電極111と上部電極120の電極間に高周波電力を印加してプラズマを発生させる。

(もっと読む)

半導体素子のパターン構造物形成方法

【課題】磁性物質又は相変化物質を含む半導体素子のパターン構造物の形成方法を提供する。

【解決手段】基板上に、磁性物質又は少なくとも3つの元素を含む合金からなった相変化物質のいずれか一つの物質を含むエッチング対象膜を形成する段階と、少なくともアンモニア(NH3)ガスを含むエッチングガスを使って前記エッチング対象膜をプラズマ反応性エッチングすることによってパターン構造物を形成する段階とを有する。

(もっと読む)

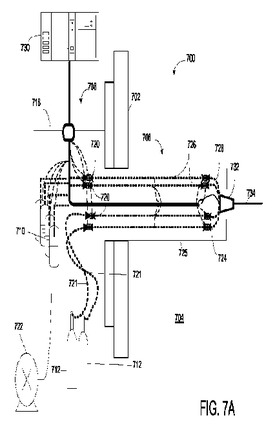

ビーム処理システムに対するガス送達

それぞれのガス源用のサイクリング弁によって、複数のガス源からビーム・システムの試料室内へのガス流が制御され、弁が開いている相対時間および弁の上流の圧力によって、試料室内のガス圧が決定される。真空室の内部に配置されたガス弁が、ガスを遮断する際の迅速な応答を可能にする。好ましいいくつかの実施形態では、使用中も真空システムの外部に置かれる容器内の固体または液体材料から前駆体ガスが供給され、この容器は、重大な漏れを生じることなく、ガス注入システムに容易に接続され、またはガス注入システムから容易に分離される。  (もっと読む)

(もっと読む)

MEMSデバイスの製造方法及びMEMSデバイスの製造装置

【課題】基板の厚さ方向への貫通部の形成に際し、その形成に要する時間の長期化を抑えつつ、該基板に亀裂が生じることを抑制可能なMEMSデバイスの製造方法、及びこのMEMSデバイスの製造方法を実施する装置を提供する。

【解決手段】基板Sの表面と裏面との間を貫通する貫通部が該基板Sの表面に照射されるエッチングプラズマによって形成することにより、MEMSデバイスを製造する。上記貫通部を形成する際に、エッチングプラズマのエネルギーに応じて昇温される基板Sを該基板Sの裏面と該基板Sが載置されるトレイ22が有する凹部22aとからなる冷媒空間に対して圧送される冷却媒体としてのヘリウムガスによって冷却した後に、基板Sの裏面に設けられた上記冷媒空間におけるヘリウムガスの圧力を上記エッチングプラズマのエネルギーと共に下げるようにする。

(もっと読む)

プラズマ処理装置及びプラズマ処理方法

【課題】誘導結合型のプラズマ処理装置において方位角方向さらには径方向のプラズマ密度分布の均一性または制御性を向上させること。

【解決手段】この誘導結合型プラズマエッチング装置において、チャンバ10の天井の誘電体壁52上の設けられるRFアンテナ54は、アンテナ室56内で誘電体窓52から離間してその上方に配置され、高周波給電部58からのRF給電ライン60,68に接続される一次コイル62と、この一次コイル62と電磁誘導により結合可能な位置で、かつこの一次コイル62よりも誘電体窓52の下面(処理空間と対向する面)の近くに配置される二次コイル64とを有している。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】p型半導体領域、n型半導体領域を有する半導体基板から成る半導体素子のpn接合部における耐圧性の向上を可能にする。

【解決手段】本発明の半導体素子の製造方法では、p型半導体領域、n型半導体領域を有する半導体基板から半導体素子を形成する。本発明の製造方法では、プラズマ処理装置1を用いて前記半導体基板の表面をプラズマエッチングすることによって前記半導体素子を取り囲む溝を形成する。そして、プラズマ条件を適宜に設定することにより、溝の内側壁のうちp型半導体領域とn型半導体領域の境界部分に横穴状の溝を形成する。この結果、形成される半導体素子は、側壁のうちp型半導体領域とn型半導体領域の境界部分に横穴構造を有することになり、pn接合部における耐圧性が向上する。

(もっと読む)

ドライエッチング方法

【課題】微細パターンに形成でき、エッチング選択比が高く、かつ高いアスペクト比でパターニングできるドライエッチング方法を提供すること。

【解決手段】このドライエッチング方法は、基板1と、基板1上に積層され、Si、SiO2、及びSi3N4からなる群から選ばれた少なくとも1つのエッチング材料を含有するエッチング層2と、エッチング層2上に積層され、Ti、V、Ga、Ge、Nb、Mo、Sb、Te、及びWからなる金属群、並びに該金属群から選ばれた金属の合金からなる群から選ばれた少なくとも1種を含有するレジスト材料を含有するレジスト層3と、を備えた積層体に対するドライエッチング方法であって、CxFy(xは2〜4、yは2x)、及びCHF3、CH2F2からなる群より選ばれた少なくとも1種を含有するとともに、エッチングガス全体のFのCに対するモル比F/Cが重量比で3以下であるエッチングガスを用いる。

(もっと読む)

レジスト膜の除去方法および表示装置の製造方法

【課題】 CF4、CHF3、C2F6等の地球温暖化の一因となるガスを用いずに、レジスト膜を良好にアッシングするレジスト膜の除去方法、およびそれを用いた表示装置の製造方法を提供する。

【解決手段】 薄膜トランジスタ及び画素電極の上層側に成膜されたオーバーコート膜12から前記画素電極の少なくとも一部を露出させる際のマスクとして前記オーバーコート層12上にパターニングして形成されたレジスト膜28を、前記オーバーコート層12から前記画素電極の少なくとも一部を露出させた後にCOF2またはF2のいずれか一方と酸素ガスとを含む混合ガスを用いて除去する。

(もっと読む)

材料処理のための新規なRFプラズマソース

【課題】コイルとプラズマ間の容量結合を減らし、プラズマチューブ内表面の腐食を有意に減らすRFプラズマソースの提供。

【解決手段】プラズマソース200は、第1コイルセグメント204と第2コイルセグメント206を有するコイル202、コイル202に接続されたRF電源208、および第1コイルセグメント204と第2コイルセグメント206間に配設されたエンクロージャ210を備える。さらに中間コイルセグメント222は、第1コイルセグメント204、第2コイルセグメント206間に電圧ノード(接地に関連する低電圧領域)を提供する。

(もっと読む)

DC/RFハイブリッド処理システム

【課題】 現状では、次世代のSOI膜である完全空乏型シリコン・オン・インシュレータ(FD SOI)は、厚さ制御の均一性及び欠陥に限界があるので、製造されていない。

【解決手段】 本発明は、少なくとも1つの直流(DC)/高周波(RF)ハイブリッド(DC/RFH)処理システム並びに関連する直流(DC)/高周波(RF)ハイブリッド(DC/RFH)手順及びDC/RFH処理パラメータ及び/又はDC/RFHモデルを用いることによってリアルタイムで基板及び/又はウエハを処理する装置並びに方法を供することができる。

(もっと読む)

フォトレジストおよびエッチング残渣の除去方法

【課題】フォトレジスト及びエッチング残渣の除去方法

【解決手段】方法は、プラズマアッシングに対し先行する誘電層のプラズマエッチングの間形成されたフォトレジスト残り及びエッチング残渣を取り除くことを提供する。アッシング方法は、酸素含有ガスを含み、基板からフォトレジスト残りとエッチング残渣のかなりの量を除去するため低バイアスもしくはゼロバイアスを基板に印加する第1のクリーニングステップと、加えてチャンバ表面からの不利益なフルオロカーボン残渣をエッチングし除去する2ステッププラズマを使用する。増加されたバイアスは、フォトレジストの残りと、エッチング残渣を基板から除去するために第2のクリーニングステップにおいて基板に印加される。2ステッププロセスは、従来の1ステップアッシングプロセスに共通に観察されるメモリー効果を減らす。終点検出の方法は、アッシングプロセスをモニタするのに使用できる。

(もっと読む)

141 - 160 / 1,078

[ Back to top ]