Fターム[5F004CA03]の内容

半導体のドライエッチング (64,834) | 装置の操作、制御方法 (5,292) | 印加電力、電圧 (997)

Fターム[5F004CA03]に分類される特許

101 - 120 / 997

プラズマエッチング方法

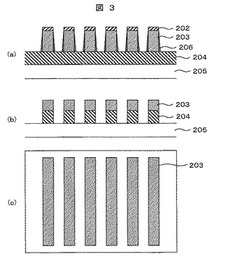

【課題】多層レジストマスクを用いたシリコン酸化膜等のプラズマエッチング後にパターンの倒壊等により発生するラインウィグリングやストライエーションを防止,抑制することを課題とする。

【解決手段】本発明は、多層レジストマスクを用いて、被エッチング膜をプラズマエッチングするプラズマエッチング方法において、前記多層レジストマスクは、上層レジストと無機膜系中間膜と下層レジストを含み、前記下層レジストの側壁に側壁保護膜を形成する側壁保護膜形成工程を有することを特徴とするプラズマエッチング方法である。

(もっと読む)

多重周波数プラズマ・エッチング反応装置及び方法

【課題】プラズマの化学的性質、密度、イオン・エネルギー、及びそれらの2つ以上のパラメータを正確に制御する装置を提供することである。

【解決手段】3以上の周波数52,54,56でプラズマを励起し、それによって、その前記3以上の周波数によるプラズマの励起がプラズマ中でいくつかの異なる現象を同時に発生させることにより、加工物18が真空プラズマ処理チャンバ10内のプラズマで処理される。装置は、チャンバ10、RFて電力供給51、またはプラズマ励起周波数のうちの少なくとも1つを他の周波数を除外して通過させるフィルタ構成67、それに依って、て基準電位に接続される中央の頂部電極14および底部電極13ならびに周辺の頂部42および/または底部電極34、を含む構成である。前記装置で前記プラズマ処理を実施することで課題を解決する事が出来る。

(もっと読む)

半導体装置の製造方法、電源回路、及びプラズマ処理装置

【課題】異なるプラズマ処理装置との間における加工寸法のばらつきを低減できる半導体装置の製造方法、電源回路、及びプラズマ処理装置を提供する。

【解決手段】半導体装置の製造方法は、プラズマ処理装置を用いた半導体装置の製造方法であって、処理室内の電極に半導体基板を載置する載置工程と、電源回路から前記電極に電力を供給するとともに、前記処理室内における前記電極から隔てられた空間にプラズマを発生させる発生工程と、前記発生工程で発生したプラズマの電位と電力が供給された前記電極の電位との差であるバイアス電圧を検出する検出工程と、前記検出工程で検出されたバイアス電圧が目標値に一致するように前記電源回路の容量値を補正する補正工程と、前記補正工程が行われた後に前記検出工程で検出されたバイアス電圧が前記目標値に一致した状態で、前記プラズマ処理装置を用いて前記半導体基板を加工する加工工程とを備えている。

(もっと読む)

基板処理方法

【課題】正イオンによるエッチング効率を低下させることなく、負イオンを有効利用して全体としてのエッチング効率を高めることができる基板処理方法を提供する。

【解決手段】プラズマRF及びバイアスRFをそれぞれパルス波として印加し、プラズマRF及びバイアスRFを共に印加してプラズマ中の正イオンによって基板にエッチング処理を施す正イオンエッチングステップ3bと、プラズマRF及びバイアスRFの印加を共に停止して処理室内で負イオンを発生させる負イオン生成ステップ3cと、プラズマRFの印加を停止し、バイアスRFを印加して負イオンを基板に引き込む負イオン引き込みステップ3aとを順次繰り返し、バイアスRFのデューティー比をプラズマRFのデューティー比よりも大きくする。

(もっと読む)

電力導入端子およびそれを備えたプラズマ処理装置

【課題】高電力供給時の高温環境下でも破損しない電力導入端子およびそれを備えたプラズマ処理装置を提供すること。

【解決手段】チャンバー1の壁を貫通する端子導入孔1bに気密に固定される一端部11a1および貫通孔11a3を有する碍子11aと、碍子11aの他端部11a2に配置される貫通孔を有する蓋体11bと、碍子11aの貫通孔11a3と蓋体11bの貫通孔に挿通される一端および一端の蓋体近傍部分に形成された雄ネジ部11c1を有する棒状導電体11cと、棒状導電体11cの雄ネジ部11c1に螺着される雌ネジ部を有する締結部材11dと、蓋体11bと締結部材11dとの間に圧接して配置される緩衝部材11eとを備えた電力導入端子。

(もっと読む)

基板処理方法及び基板処理装置

【課題】上部電極の消耗を防止しつつ、処理空間におけるプラズマの密度分布の制御性を向上することができる基板処理装置を提供する。

【解決手段】第1の高周波電源18に接続され且つウエハWを載置するサセプタ12と、該サセプタ12と対向して配された上部電極板28と、サセプタ12及び上部電極板28の間の処理空間PSとを備え、プラズマを用いてウエハWにプラズマエッチング処理を施す基板処理装置10は、上部電極板28における処理空間PSに面する部分を覆う誘電体板27を備え、上部電極板28は、ウエハWの中央部と対向する内側電極28aと、ウエハWの周縁部と対向する外側電極28bとに分割され、内側電極28aと外側電極28bとは互いに電気的に絶縁され、内側電極28aには第2の可変直流電源33から正の直流電圧が印加されるとともに、外側電極28bは電気的に接地される。

(もっと読む)

ドライエッチング装置及びドライエッチング方法

【課題】単一の電源及び単一のマッチングボックスにより、各被エッチング物の最適な周波数を用いてエッチングする。

【解決手段】被エッチング材が載置されるステージを内部に有する真空容器と、前記真空容器内にプロセスガスを供給するプロセスガス供給手段と、前記真空容器内にプラズマを生成させるためのプラズマ生成手段と、前記プラズマ生成手段の電極にプラズマ生成用高周波電力を供給するプラズマ生成用電源と、前記ステージの自己バイアス電位を制御するための単一のバイアス電源であって、出力周波数を変更可能なバイアス電源と、前記ステージと前記バイアス電源との間に電気的に接続された単一の整合器であって、前記バイアス電源の負荷と前記バイアス電源とのインピーダンス整合をとる整合器と、前記バイアス電源の出力周波数を設定する周波数設定手段と、前記バイアス電源の出力周波数に応じて前記整合器のインピーダンスを制御する制御手段とを備えたドライエッチング装置によって上記課題を解決する。

(もっと読む)

半導体基材の状態測定方法及び状態測定装置

【課題】プラズマ環境下で半導体基材の結晶状態を測定することができる装置及び方法を提供する。

【解決手段】プラズマエッチング装置10では、チャンバ11にエッチング用のガスが導入されるとともに、高周波電源16によって高周波コイル15に電圧が印加されることにより、チャンバ11内にプラズマが発生する。チャンバ11内には、半導体基材Aを保持する基材ホルダー電極20と、基材ホルダー電極20に対応して配置される陰極21とが設けられる。陰極21には、高圧パルス電源22により負電圧が印加される。分光計23は、半導体基材Aの発光態様を測定する。

(もっと読む)

プラズマ処理装置

【課題】真空処理室内壁表面に発生する自己バイアスを抑制することにより、真空処理室内壁表面の削れあるいは真空処理室内パーツの消耗を抑制することを課題とする。

【解決手段】本発明は真空処理室と、前記真空処理室の上部を閉塞する真空処理室蓋と、誘導アンテナと、前記誘導アンテナと前記真空処理室蓋との間に設置されたファラデーシールドと、前記誘導アンテナに高周波電力を印加する高周波電源とを有するプラズマ処理装置において、前記誘導アンテナは、2つ以上に分割され、前記ファラデーシールドは、前記誘導アンテナの分割数に応じた分割数で分割され、また、一つの前記高周波電源から整合器を介して、高周波電圧を印加されることを特徴とするプラズマ処理装置である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10にトランジスタ36を形成する工程と、半導体基板上に、トランジスタを覆う第1のシリコン窒化膜38を形成する工程と、第1のシリコン窒化膜にNH4Fラジカルを供給する工程と、NH4Fラジカルを供給する工程の後、第1のシリコン窒化膜に対して熱処理を行う工程と、熱処理を行う工程の後、第1のシリコン窒化膜上に第2のシリコン窒化膜を形成する工程とを有している。

(もっと読む)

エッチング方法およびエッチング装置

【課題】SF6ガスとおよびO2ガスを用いてシリコン及びSOI基板にTrnch又はViaを形成する際に、マスク加工寸法異常やマスク消失を抑制し、かつウエハ面内の形状差を抑制する方法を提供する。

【解決手段】シリコン及びSOI基板2に溝および/または穴を形成するエッチング方法であって、フッ素含有ガスと酸素含有ガスと珪素含有ガスの混合ガスを用いて、プロセスガス導入口4から反応容器1内に導入して混合ガスプラズマを生成し、反応容器1内に設置する基板2を載置する電極(試料台)3内外に温度差を設け、かつ高周波バイアス電源11から高周波電力を時間的に変調した間欠的な高周波のバイアスを印加する。

(もっと読む)

プラズマ処理装置、プラズマ処理方法および半導体素子の製造方法

【課題】導電体の熱断線の発生を抑制することができるプラズマ処理装置を提供すること。

【解決手段】反応性ガスが導入される密封可能なチャンバーと、前記チャンバー内に対向状に配置されたカソード電極およびアノード電極を有し前記カソード電極と前記アノード電極の間でプラズマ放電を発生する放電部と、前記カソード電極に電力を供給する電源と、前記電源と前記カソード電極とを電気的に接続する導電体と、前記導電体を冷却する空冷手段とを備えたことを特徴とするプラズマ処理装置。

(もっと読む)

プラズマ処理方法及びプラズマ処理装置

【課題】プロセスに応じて適正にA/C比を制御する。

【解決手段】第1の高周波電源140からプラズマ生成用の高周波電力を印加して処理容器内のプラズマ処理空間Uにプラズマを生成するプラズマ処理装置を用いたプラズマ処理方法であって、プラズマ処理装置は、バイアス用の高周波電力を印加する第2の高周波電源150と、プラズマ処理空間Uを形成する処理容器100の内壁に少なくとも一部が接し、処理容器内にて上下動することによりプラズマ処理空間Uの接地容量を調整する調整機構200とを有し、プラズマ処理方法では、第2の高周波電源150から印加される高周波電力が500W以下の場合、調整機構200を可動範囲の上側に位置付け、該高周波電力が1500W以上の場合、調整機構200を可動範囲の下側に位置付ける。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】

ウエハ面内における入射イオンエネルギーの分布関数の均一性を高め、ウエハ面内で均一なプラズマ処理(エッチング等)を実現する。

【解決手段】

プラズマ処理装置において、ウエハ2を戴置するための戴置電極4のバイアス印加部分をウエハ2の中心付近と外周付近で内側電極4−1と外側電極4−2に分割し、ウエハ2に入射するイオンを加速するための第1のバイアス電力21−1と第2のバイアス電力21−2をそれぞれ2つに分岐し、電力分配器29−1、29−2を用いて内側電極4−1と外側電極4−2に電力比を調整して供給する。

(もっと読む)

プラズマ処理装置の制御方法

【課題】稼動状態を維持したまま処理室内から付着物を除去することが可能なプラズマ処理装置およびその制御方法を提供する。

【解決手段】ウェハに対するプラズマ処理が開始される直前に下部電極に対してオーバーシュート電圧が印加される。このオーバーシュート電圧によって,下部電極の周辺部に付着し堆積した付着物が除去されるため,プラズマ点火直後の処理室内における異常放電の発生が防止される。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比でも異なる開口幅のトレンチの深さ制御が行え、かつ、プロセス時間の増大を抑制できるようにする。

【解決手段】エッチングステップ時にM種類の異なる幅の複数のトレンチ33のうちN番目(ただし、NはM未満の整数)に幅の狭いトレンチ33の底面上で保護膜34が除去されたタイミングに合せて、当該エッチングステップの残り時間内でN番目のトレンチ33の底面上におけるシリコンのエッチング量が(N+1)番目に幅の狭いトレンチ33の底面上におけるシリコンのエッチング量以上になるように、反応性イオンエッチングにおける入射イオンのエネルギー値を設定する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】イオンエネルギー分布の制御に加えて正イオンによるチャージアップの緩和を行うことで、加工形状の制御をさらに高精度に行うことができる半導体装置の製造方法及び半導体製造装置を提供する。

【解決手段】半導体製造装置としてのプラズマ処理装置10は、チャンバー11と、チャンバー11に設けられ、半導体ウエハWが配置されるウエハ設置電極12と、ウエハ設置電極12に対向するようにチャンバー11内に設けられた対向電極13と、ウエハ設置電極12に高周波電圧を印加する高周波電源14と、ウエハ設置電極12に高周波電圧と重畳するように負の第1のDCパルス電圧V1を印加する第1のDCパルス電源17Aと、第1のDCパルス電圧V1のオフ期間に、対向電極13に負の第2のDCパルス電圧V2を印加する第2のDCパルス電源17Bとを備える。

(もっと読む)

複数温度領域分割制御構造体

【課題】異なる温度に調整される2つ以上の領域を有する構造体であって、水平方向の熱伝導を抑制すると共に、垂直方向からの入熱に対してはスムーズな熱の移動を確保して熱的特異点の発生を抑制することができる複数領域温度分割制御構造体を提供する。

【解決手段】表面温度がそれぞれ異なる温度に制御されるセンターエリア51及びエッジエリア52と、その間に配置され、センターエリア51とエッジエリア52の配列方向に沿った熱伝導率が、配列方向に交差する方向における熱伝導率よりも小さく、水平方向の熱伝導に対して、例えば断熱材として機能し、且つ垂直方向の熱伝導に対して、例えば熱伝導材として機能する傾斜材56を配置する。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】 インピーダンスの可変範囲内の広域にわたって処理速度の制御を容易に行うことを可能とする。

【解決手段】 基板処理装置は、基板を処理する処理室と、処理室内にて基板を支持する基板支持部と、処理室内に処理ガスを供給する処理ガス供給部と、処理室内に供給された処理ガスをプラズマ状態とするプラズマ生成電極と、プラズマ生成電極に高周波電力を印加する高周波電源と、基板支持部に設けられ基板の電位を制御するインピーダンス可変電極と、インピーダンス可変電極に接続され、プラズマ生成電極のピーク間電圧値の逆数に応じてインピーダンスを変更可能なインピーダンス可変機構と、処理室内の雰囲気を排気する排気部と、少なくともインピーダンス可変機構を制御する制御部と、を備えて構成される。

(もっと読む)

エッチング処理方法

【課題】形成されるパターンのアスペクト比が高くてもパターンが歪むのを防止することができるエッチング処理方法を提供する。

【解決手段】処理室15内部にプラズマ生成用の高周波電力55が印加され、サセプタ12にイオン引き込み用の高周波電力56が印加され、上部電極板27に負の電位の直流電力が印加される基板処理装置10において、ウエハW上のフォトレジスト膜45において形成されたパターン44の形状を改良する際、フォトレジスト膜45をプラズマでエッチングし、該フォトレジスト膜45を用いてSiO2膜40をプラズマでエッチングする際、負の電位の直流電力を上部電極板27に印加するとともに、プラズマ生成用の高周波電力55及びイオン引き込み用の高周波電力56をパルス波状に印加してプラズマ生成用の高周波電力55及びイオン引き込み用の高周波電力56が印加されない状態を作り出す。

(もっと読む)

101 - 120 / 997

[ Back to top ]