Fターム[5F004FA08]の内容

半導体のドライエッチング (64,834) | エッチング工程前後の処理 (659) | その他 (343)

Fターム[5F004FA08]に分類される特許

1 - 20 / 343

プラズマ処理方法

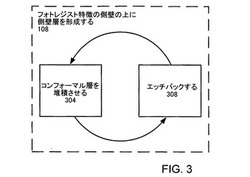

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

イオンビームにより基板を加工するための方法、及び基板を加工するためのイオンビーム装置

【課題】改善されたイオンビームにより基板を加工するための方法、及び基板を加工するためのイオンビーム装置を提供する。

【解決手段】本発明は、イオンビーム装置(1) のイオンビーム源(1.1) によって発生し、基板(2) を加工するために基板(2) の表面(2.1) を向いたイオンビーム(I) により基板(2) を加工するための方法に関する。イオンビーム(I) は、炭素含有材料から少なくとも部分的に形成されたオリフィス板(1.3) によって導かれる。本発明によれば、炭素と反応する遊離体(E) が、イオンビーム(I) によってオリフィス板(1.3) から放出された炭素が酸化するように方向性のある流れでオリフィス板(1.3) と基板(2) との間に導かれる。

(もっと読む)

半導体装置の製造方法

【課題】トレンチの深さを安定化する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に前記半導体基板に比べエッチング選択比の高い第一膜を作成する工程と、前記第一膜上に前記第一膜に比べエッチング選択比の高い第二膜を作成する工程と、一部の領域の前記第二膜および第一膜をエッチングし前記領域の半導体基板表面を露出させる工程と、前記露出した半導体基板表面をエッチングしトレンチを作成する工程を有する安定したトレンチ深さを提供する半導体装置の製造方法とした。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

基板処理装置および基板処理方法

【課題】処理液による処理の際に電荷の移動による基板の損傷を防止するとともに、処理液と他の液体との混合による悪影響を防止する。

【解決手段】基板処理装置1では、除電液供給部6により、SPM液よりも比抵抗が大きい除電液が基板9上に供給され、基板9の上面91全体が除電液にてパドルされることにより、基板9が比較的緩やかに除電される。続いて、基板回転機構5により基板9が回転することにより、基板9上から除電液が除去された後、処理液供給部3により基板9上にSPM液が供給されてSPM処理が行われる。これにより、SPM処理の際に、基板9からSPM液へと大量の電荷が急激に移動することが防止され、基板9の損傷を防止することができる。また、除電液とSPM液との混合による悪影響(例えば、除電液中の水とSPM液中の硫酸との反応熱による基板9の損傷)を防止することができる。

(もっと読む)

マスクブランクの製造方法及び転写用マスク

【課題】転写用マスクの黒欠陥の発生を抑制することのできるマスクブランクの製造方法を提供する。

【解決手段】基板上に転写パターンを形成するための薄膜を備えたマスクブランクの製造方法であって、前記薄膜は、ドライエッチングが可能な材料からなり、前記薄膜の表面に、エッチング阻害要因物質の濃度が0.3ppbよりも高く、pHが8以上である第1の処理液を用いて表面処理を行う第1処理工程と、前記第1処理工程後、エッチング阻害要因物質の濃度が0.3ppb以下であり、pHが8以上である第2の処理液を用いて表面処理を行う第2処理工程と、前記第2処理工程後、エッチング阻害要因物質の濃度が0.3ppb以下であり、pHが6より大きく8未満である第3の処理液を用いて表面処理を行う第3処理工程と、を有することを特徴とするマスクブランクの製造方法。

(もっと読む)

半導体ドライプロセス後の残渣除去液及びそれを用いた残渣除去方法

【課題】本発明は、Cu及びlow-k膜にダメージを与えずに、従来のポリマー剥離液で解決し得なかったわずかな亀裂状のCu腐食の抑制が可能なドライプロセス後の残渣除去液を提供し、これを用いた半導体デバイスの製造方法を確立する。

【解決手段】ドライエッチング及び/又はアッシング後の半導体基板に存在する残渣の除去液であって、フッ素化合物を含まず、銅に配位し得る2以上の酸素原子を有する中性有機化合物及び/又はC4以上のモノアルコールのうち少なくとも1種と、水とを含むことを特徴とする残渣除去液、或いは、過塩素酸塩と水とを含むことを特徴とする残渣除去液に関する。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

レジスト除去方法、修復方法および素子

【課題】レジスト残渣を残さず、かつ、レジストの下層(例えば半導体層)へのダメージを従来よりも抑えることが可能なレジスト除去方法を実現する。

【解決手段】本発明は、素子に付いたレジスト3の一部を除去対象として除去するレジスト除去方法の発明である。本発明では、例えば、除去対象の一部が除去加工されるとともに除去対象の残りの一部6が露光されるように除去対象に向けてレジストが吸収する波長のレーザー光4を照射するとともに、露光された部分6を現像により除去することで、半導体素子に塗布したレジスト3の一部を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

プラズマエッチング確認装置

【課題】ウェーハに対して所望のプラズマエッチングが行われたか否かを確認できるようにする。

【解決手段】ウェーハ10を保持する測定テーブル2と、ウェーハ10の外周部の形状確認をするための形状測定手段3とを有し、形状測定手段3が測定テーブル2の上方に位置し、形状測定手段3と測定テーブル2とを相対的に移動させることにより形状測定手段3がウェーハの形状を測定するプラズマエッチング確認装置1を用い、プラズマエッチング処理後のウェーハ10の形状に基づき、プラズマエッチングの良否を判定する。

(もっと読む)

半導体基板の表面エッチング装置、およびそれを用いて表面に凹凸形状が形成された半導体基板を製造する方法

【課題】ClF3,XeF2,BrF3およびBrF5のガスを用いつつ、量産化に対応可能な半導体基板表面をエッチングする装置を提供すること。

【解決手段】大気圧以下に減圧可能な反応室と;反応室内を移動可能であり、半導体基板を載置するための移動ステージと;半導体基板表面に向けて、ClF3,XeF2,BrF3およびBrF5からなる群から選ばれる一以上のガスを含むエッチングガスを噴射するノズルと;半導体基板に向けて、窒素ガスまたは不活性ガスを含む冷却ガスを噴射するノズルと、大気圧以下に減圧可能な洗浄室と;洗浄室内を移動可能であり、半導体基板を載置するための移動ステージと;半導体基板表面に向けて、純水、フッ化水素水からなる一以上のガスを含むエッチングガスを噴射するノズルと;半導体基板に向けて、窒素ガスまたは不活性ガスを含む乾燥ガスを噴射するノズルとを有する、半導体基板の表面エッチング装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20を窒素プラズマに曝露する。これにより、既存の側壁保護膜32にAlNが合わさって側壁保護膜32を分厚くすることができる。

(もっと読む)

アッシング方法およびアッシング装置

【課題】ポッピングの発生を抑制するとともに、ポッピングが発生してしまった場合には飛散した変質層の破片をも除去することができるアッシング方法およびアッシング装置を提供する。

【解決手段】イオン注入により表面に形成された変質層4とその下の未変質層3とを有するレジストを除去するアッシング方法であって、基板の前記レジストが形成された面を覆うように塗布膜5を形成し、前記レジストと前記塗布膜5とを反応性ガスを用いたプラズマ処理により除去する。

(もっと読む)

シリコン酸化物加工方法

【課題】 シリコン酸化物加工方法に関し、有害物質を用いることなく且つ加工屑を発生させることなく、シリコン酸化物の微細加工を可能にする。

【解決手段】 シリコン酸化物からなる被加工物上に水素と6個以上の炭素を含む有機化合物を供給しながら、エネルギビームを照射して、照射部位における前記シリコン酸化物をシリコン含有炭素化合物に変換し、前記変換したシリコン含有炭素化合物をハロゲンを含まない雰囲気中で化学反応により除去する。

(もっと読む)

洗浄組成物、これを用いた洗浄方法及び半導体素子の製造方法

【課題】半導体製造における大型のメタル等の洗浄において、プラズマエッチング残渣やアッシング残渣を十分に除去する高い洗浄力を発揮し、部材の剥離や変色を抑制し、さらには必要によりメタル材料の表面荒れをも抑制しうる半導体基板用洗浄組成物、これを用いた洗浄方法及び半導体素子の製造方法を提供する。

【解決手段】洗浄組成物により、エッチング工程及び/又は前記アッシング工程において半導体基板上に形成されたプラズマエッチング残渣及び/又はアッシング残渣を洗浄除去する洗浄工程を含む半導体素子の製造方法であって、該洗浄組成物は、水と、塩基性有機化合物と、酸性有機化合物と、有機溶媒とを組み合わせて含有し、pHが1.5〜5.0に調整されたことを特徴とする半導体素子の製造方法。

(もっと読む)

1 - 20 / 343

[ Back to top ]