Fターム[5F032BA08]の内容

Fターム[5F032BA08]に分類される特許

1 - 20 / 139

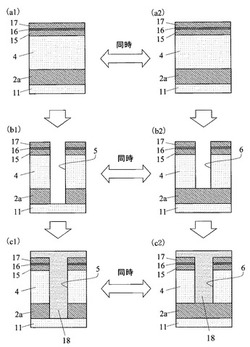

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減化を通じて、出力容量Cossの低減化に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1とこの半導体基板1上に埋め込み絶縁層を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域3内に形成された素子領域と、素子領域の少なくとも1つに接続される外部取り出し用の電極(ドレインパッド9p)とを有する半導体装置において、外部取り出し用の電極9p下に位置する活性領域が、埋め込み絶縁層2に到達するように形成された絶縁分離領域11で囲まれており、絶縁分離領域11で分離された活性領域3と、外部取り出し用の電極9pとの間に絶縁体13が配されたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置

【課題】複雑な形状を有しながらも応力分布のばらつきが少ない活性領域を有する半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、素子分離領域を有する基板と、前記素子分離領域に分離された、不純物拡散領域を有する前記基板上の複数の四角形の活性領域と、前記複数の活性領域の集合からなり、段差を含む輪郭形状を有する大活性領域とを有する。前記複数の活性領域の前記不純物拡散領域のうち、前記素子分離領域を挟んで向かい合う不純物拡散領域は、電気的に接続される。

(もっと読む)

半導体メモリおよびその製造方法

【課題】素子分離トレンチ内の絶縁膜のエッチングとアライメントトレンチ内の絶縁膜のエッチングとを、1つのマスクを用いて同時に行える構造の半導体メモリを提供する。

【解決手段】シリコン基板2には、メモリセル領域70およびアライメントマーク領域80が設定されている。メモリセル領域70には、シリコン基板2の表層部に、アクティブ領域30を分離する素子分離トレンチ21が形成されている。アライメントマーク領域80には、シリコン基板2の表層部に、マスク合わせのためのアライメントトレンチ82が形成されている。素子分離トレンチ21内には、素子分離トレンチ21間のアクティブ領域30が突出するように、絶縁物(酸化膜)23が素子分離トレンチ21の深さ方向途中まで埋め込まれている。一方、アライメントトレンチ82内には、絶縁物23がアライメントトレンチ82の深さ方向途中まで埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コスト削減、サイズ縮小ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、P型Si基板21の主面にトレンチ22を形成することによって、エンハンスメント型FET形成用の幅狭部分とでプレション型FET形成用の幅広部分とを含むアクティブ領域25を形成する工程と、主面の法線に対して30度〜45度の範囲内の注入角で、且つ、注入方向が法線を中心に相対的に回転するように、Si基板21に対してP型不純物を注入して、幅広部分にP型のチャンネルストッパー領域25aを形成すると共に、幅狭部分にP型チャンネル拡散領域25bを形成する工程と、トレンチ22をトレンチ素子分離絶縁層26で埋める工程と、ゲート絶縁膜27を形成する工程と、Si基板21上にN型不純物を注入して第2の部分にN型チャンネル拡散領域28を形成する工程と、ゲート電極29を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】占有面積を増やすことなくロジック回路領域におけるトランジスタ特性の変動が抑制される半導体装置を提供する。

【解決手段】NMOS領域の素子形成領域4と、この素子形成領域4に隣り合う他の素子形成領域4との間隔(ゲート幅方向)が一定の間隔(距離2×LA)に設定されている。また、この素子形成領域4と、この素子形成領域4に隣り合う素子形成領域8との間隔(ゲート幅方向)も一定の間隔(距離2×LA)に設定されている。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

不均一な半導体装置のアクティブ領域パターン形成方法

【課題】不均一な半導体装置のアクティブ領域パターン形成方法を提供する。

【解決手段】具体例によると、少なくとも3つのアクティブ領域を含む半導体装置が提供される。少なくとも3つのアクティブ領域は隣接する。少なくとも3つのアクティブ領域の縦軸は平行で、少なくとも3つのアクティブ領域は、それぞれ、対応するアクティブ領域の縦軸と交差する辺縁を有する。少なくとも3つのアクティブ領域の辺縁は弧形を形成する。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

1 - 20 / 139

[ Back to top ]