Fターム[5F032CA09]の内容

Fターム[5F032CA09]の下位に属するFターム

砒化ガリウム (103)

多結晶シリコン・非晶質シリコン (19)

Fターム[5F032CA09]に分類される特許

1 - 20 / 261

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

電力用半導体装置

【課題】基板の欠陥に起因した歩留まりの低下を抑制しつつ、容易に製造することができる電力用半導体装置を提供する。

【解決手段】セル電極150は、半導体基板130上に設けられており、セル構造CLのそれぞれに設けられている。セル電極150は、2以上のセル電極150を含むグループ150a〜150cに分けられている。導電部材160a〜160cはグループ150a〜150cのそれぞれに電気的に接続されている。導電部材160a〜160cは使用部UDおよび非使用部NDを有する。使用部UDは、互いに電気的に接続された2以上の導電部材160aおよび160bを有する。非使用部NDは、導電部材160a〜160cの少なくとも1つを有し、かつ使用部UDと電気的に絶縁されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法

【課題】 生産性に優れる空洞半導体基板、ならびに空洞半導体基板および半導体素子の製造方法を提供する。

【解決手段】 空洞半導体基板1は、支持基板10と、半導体基板20と、を有する。この半導体基板20は、下主面21bの上に一体的に形成され且つ当該下主面21bから突出している脚部22を介して支持基板10の上に張り合わされている。この半導体基板20は、下主面21bが支持基板10から離隔している。

(もっと読む)

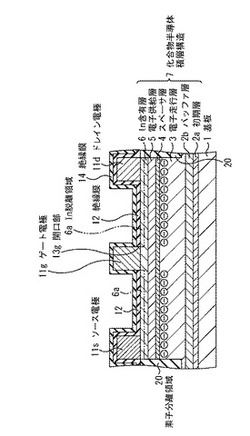

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置

【課題】半導体電子素子を含む電子装置の微細化、及び低コスト化を実現する。

【解決手段】半導体膜を含む電子素子を複数備える電子装置であって、電子素子の素子間に素子分離領域が存在し、素子分離領域は、バンドギャップが1.95eV以上である半導体膜と、絶縁体膜と、素子分離電極と、を含み、素子分離電極は、絶縁体膜によって素子分離領域の半導体膜と隔てられ、電圧が印加されて素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離するための電極であることを特徴とする電子装置。

(もっと読む)

有機トランジスタ及び有機トランジスタの製造方法

【課題】導体層におけるソース電極とドレイン電極との電極間のチャネル領域が結晶相であり、且つ該半導体層における該チャネル領域以外の第2の領域が非結晶相である構成ではない場合に比べて、半導体素子間の電気的な分離が実現された有機トランジスタを提供する。

【解決手段】有機トランジスタ10は、基板12上に、ゲート電極14G、ゲート絶縁膜16、ソース電極18S及びドレイン電極18D、及び半導体層20が設けられている。半導体層20における、ソース電極18S及びドレイン電極18Dとの電極間の領域であるチャネル領域20Aは、結晶相とされている。また、半導体層20における、このチャネル領域20A以外の第2の領域20Bは、非結晶相とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

トレンチ埋め込み用組成物

【課題】基板表面上のナノメートルレベルの開口幅を有し、アスペクト比が大きいトレンチ(溝)への埋め込み性に優れ、ボイドなどの欠陥の発生が抑制され、電気的絶縁性に優れたアイソレーション構造を製造するのに好適なトレンチ埋め込み用組成物、および該組成物を用いたトレンチ・アイソレーション構造の製造方法の提供。

【解決手段】アルキルトリアルコキシシランを50モル%以上含むアルコキシシラン原料を加水分解、縮合して得られる加水分解縮合物を含有し、該加水分解縮合物の重量平均分子量が1000〜50000であり、該加水分解縮合物の含有量が組成物全量に対して14質量%超30質量%以下であるトレンチ埋め込み用組成物の塗膜14により、基板10表面上に形成されたトレンチ12を埋め込む。

(もっと読む)

半導体装置の製造方法及び半導体装置並びにその半導体装置を内蔵する多層基板

【課題】dv/dtサージにより、寄生容量を充放電する変位電流の発生を抑制できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】低電位基準回路部LV、高電位基準回路部HV、レベルシフト回路部LSを形成したSOI基板の半導体層の主面上にサポート部材を貼り付け、支持基板を除去する。次いで、回路部と対向するように絶縁部材を半導体層の裏面上に固定した後、サポート部材を剥がす工程と、チップ内にLV,HV,LSが含まれるように絶縁部材の固定された半導体層をダイシングする工程を経る。そして、サポート部材を剥がし、チップ化した半導体層を、絶縁部材を挟んで、第1のリードがLVと、第2のリードがHVと対向するように、第1リード及び第2リード上に固定するとともに、第1のリードとLVにおける第1の電位が印加される部位を電気的に接続し、第2のリードとHVにおける第2の電位が印加される部位を電気的に接続する。

(もっと読む)

1 - 20 / 261

[ Back to top ]